Page 1 of 2

VDU, V9958

Posted: Tue Jan 20, 2015 11:08 am

by legacy

hi guys

i am playing with so pretty old hardware stuff and i wander if anyone has already realized a PCB with a V9958 on it, plus DRAM and the proper interface an RGB-S device

also, i am looking for any examples about the sw side

let me know

Re: VDU, V9958

Posted: Tue Jan 20, 2015 2:01 pm

by HansO

You can have a look at the MSX machines with a V9958.

Like the turbo-R. Circuit is in the service manual on

http://msx.hansotten.com

Re: VDU, V9958

Posted: Tue Jan 20, 2015 5:51 pm

by lordbubsy

After Aslak3 successfully made an interface for the V9958 to his 6809 SBC, I made my own for the 65xxx CPU and modified the RGB output to get a better picture.

Furthermore I took the output drivers from a schematic which HansO provided.

(see attachment)

So credit goes to Aslak3 and HansO.

The picture is stable and sharp. Picture quality depends very much on a clean power supply provided for the VDP.

Re: VDU, V9958

Posted: Tue Jan 20, 2015 6:46 pm

by legacy

thank you guys

could i ask if there is a library or a piece of code that shows how to use the blitter and such a things about V9958 ?

i am planning to realize a PCB with a V9958 on it, and a library to use it.

Re: VDU, V9958

Posted: Tue Jan 20, 2015 7:16 pm

by legacy

about the VDU, i see you have

{R,G,B,H_sync,C_sync}

C_sync stands for "

Composite SYNC output", so the VDU is RGB-S compatible

wandering what is H_sync useful for …

umm, it seems TMS9918/28/29 doesn't do RGB-S

the V9958 there is no separate Vsync output, V9958 does RGB-S, so it output Csync only.

and reading its data sheet of V9958, the Hsync is the

horisontal part of the Csync signal.

So the

Csync contains both

Hsync and

Vsync, but how are they mixed ?

a few hypothesis:

- Csync = Hsync AND Vsync

- Csync = Hsync XOR Vsync

- Csync = Hsync -?- Vsync

Re: VDU, V9958

Posted: Tue Jan 20, 2015 7:34 pm

by lordbubsy

I think you can use an LM 1881 Video Sync Separator to separates Csync into Hsync and Vsync.

http://www.ti.com/lit/ds/symlink/lm1881.pdf

Why, do you want to connect it to a VGA monitor? If so, the VGA monitor has accept 31kHz, and as far as I know, only old MultySync monitors can do that.

Edit:

I don’t use a library, so far, I programmed it from the datasheets from the

• TMS9918

• V9938

• V9958

since the V9958 is backward compatible to those other two.

• TMS9918

http://www.cs.columbia.edu/~sedwards/papers/TMS9918.pdf

http://map.grauw.nl/resources/video/ti- ... -guide.pdf

http://bifi.msxnet.org/msxnet/tech/tms9918a.txt

• V9938

http://rs.gr8bit.ru/Documentation/V9938 ... -guide.pdf

http://bitsavers.informatik.uni-stuttga ... _Aug85.pdf

http://www.konamiman.com/msx/msx2th/th-4a.txt

• V9958

http://primrosebank.net/computers/mtx/t ... l_v1.0.pdf

Re: VDU, V9958

Posted: Tue Jan 20, 2015 8:46 pm

by legacy

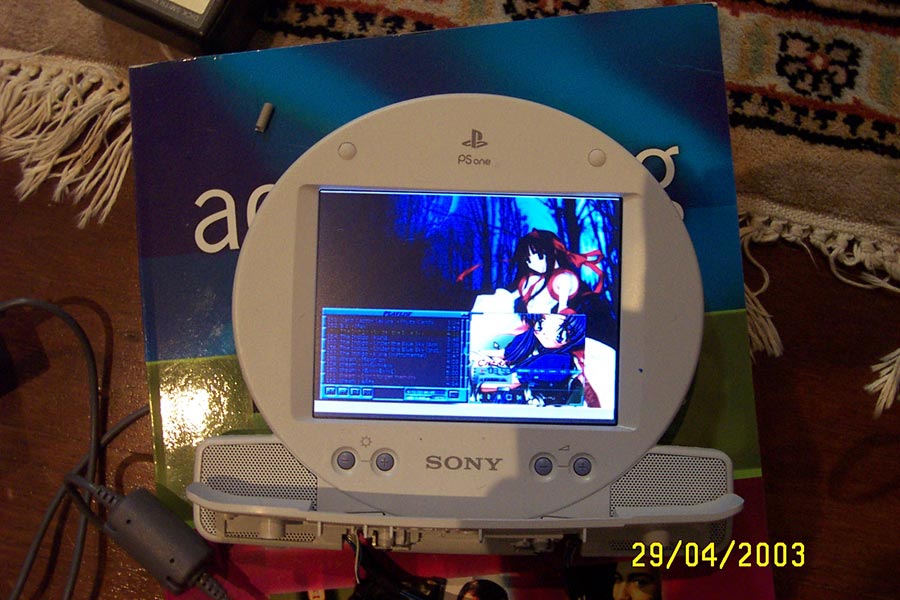

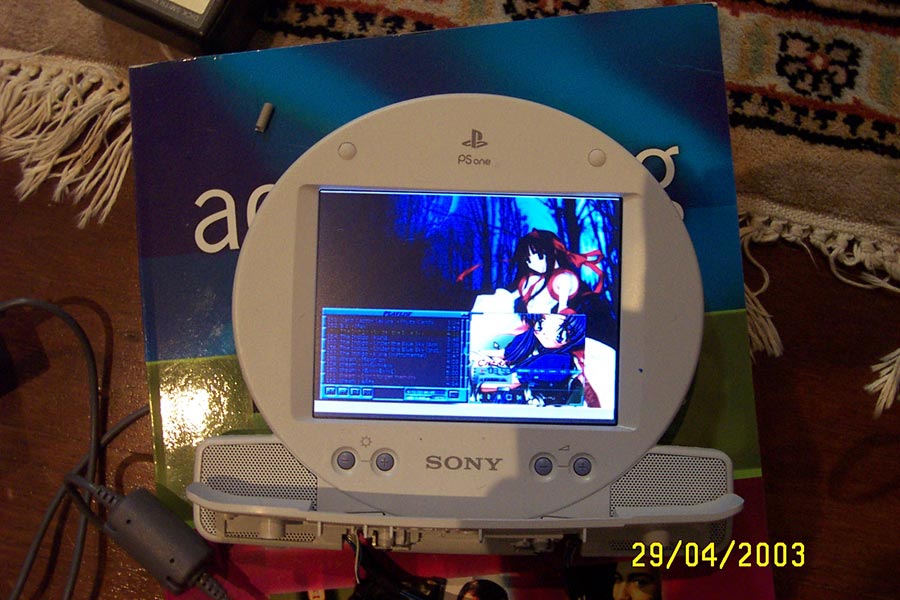

Sony Playstation LCD, aka PSOne LCD

Why, do you want to connect it to a VGA monitor? If so, the VGA monitor has accept 31kHz, and as far as I know, only old MultySync monitors can do that.

the story goes more complex

i have also been designing a VDU in vhdl, i have realized something (a few vhdl lines of code for a very simple bitmap frame buffer) that works for a VGA lcd, so i am using H and V sync, as they are described in the VGA documentation.

For the V9958 & my VDU-fpga-project I'd like to use the Sony Playstation LCD, which is RGB-S, so, in order to re-use what i have done for VGA i need to combine my actual H_sync and V_sync into a C_sync in order to inter the PSOne LCD

The

PSOne LCD AV-connecotr has these signals

- video_R

- video_G

- video_B

- video_composite Sync

- LCD_enable

- sound_right

- sound_left

The V9958 could directly connected to the PSOne LCD, more work is required for the VHDL code.

BTW, about C_Sync, it seems it is derived from the following circuit

Re: VDU, V9958

Posted: Tue Jan 20, 2015 9:01 pm

by legacy

this page is teaching something about

we know that

- composite sync is a combination of horizontal sync and vertical sync

- horizontal sync is short, frequent pulses

- vertical sync is much less frequent, much longer pulses

- H_sync pulses still occur during the V_sync

It seems to me that, aside from getting things to the appropriate polarity, and apparently some pulse shaping/limiting

that's what the XOR in the diagram is doing

or not ?

what do you think, guys

Re: VDU, V9958

Posted: Wed Jan 21, 2015 8:51 pm

by legacy

hi

an other question: the DRAM

TMS4464 is 4 bit, so we need 2xTMS4464 (each DRAM is 64K word, each word is 4bit), and this means having a total of 4 chips (or 6 chip in the expansion memory schema)

is there a DRAM memory, compatible with the V9958, which is already 8bit ? just to reduce the number of chips on the PCB

edit:

i was wrong the HM4864P is 64Kbit, not Kbyte

Re: VDU, V9958

Posted: Thu Jan 22, 2015 5:57 am

by Rob Finch

just to reduce the number of chips on the PCB

I think one could use a higher density RAM like a 514256 (256k x4) and convert the CAS0/CAS1/CASX into another address line. One could get away with 2 RAM chips then plus a PLD of some sort.

Re: VDU, V9958

Posted: Thu Jan 22, 2015 6:03 am

by Rob Finch

Another possibility is to use static RAMs by latching the RAS/CAS addresses.

Re: VDU, V9958

Posted: Thu Jan 22, 2015 10:41 am

by legacy

Another possibility is to use static RAMs by latching the RAS/CAS addresses

it seems a good idea,

this document is telling me more details about cycles

Re: VDU, V9958

Posted: Thu Jan 22, 2015 11:07 am

by legacy

what do you think about using a 30-pin SIMM module ?

Code: Select all

30-pin SIMMS have 12 address lines, which can provide a total of 24 address bits. With an 8 bit data width, this leads to an absolute maximum capacity of 16 MB for both parity and non-parity modules (the additional redundancy bit chip usually does not contribute to the usable capacity).

30-pin SIMM Memory Module

Pin # Name Signal Description Pin # Name Signal Description

1 VCC +5 VDC 16 DQ4 Data 4

2 /CAS Column Address Strobe 17 A8 Address 8

3 DQ0 Data 0 18 A9 Address 9

4 A0 Address 0 19 A10 Address 10

5 A1 Address 1 20 DQ5 Data 5

6 DQ1 Data 1 21 /WE Write Enable

7 A2 Address 2 22 VSS Ground

8 A3 Address 3 23 DQ6 Data 6

9 VSS Ground 24 A11 Address 11

10 DQ2 Data 2 25 DQ7 Data 7

11 A4 Address 4 26 QP* Data parity out

12 A5 Address 5 27 /RAS Row Address Strobe

13 DQ3 Data 3 28 /CASP* Parity Column Address Strobe

14 A6 Address 6 29 DP* Data parity in

15 A7 Address 7 30 VCC +5 VDC

* Pins 26, 28 and 29 are not connected on non-parity SIMMs.

Re: VDU, V9958

Posted: Thu Jan 22, 2015 12:16 pm

by BigEd

For those following at home, there's a parallel discussion on the same lines starting around here:

http://anycpu.org/forum/viewtopic.php?f ... t=15#p1038

Re: VDU, V9958

Posted: Thu Jan 22, 2015 3:05 pm

by legacy

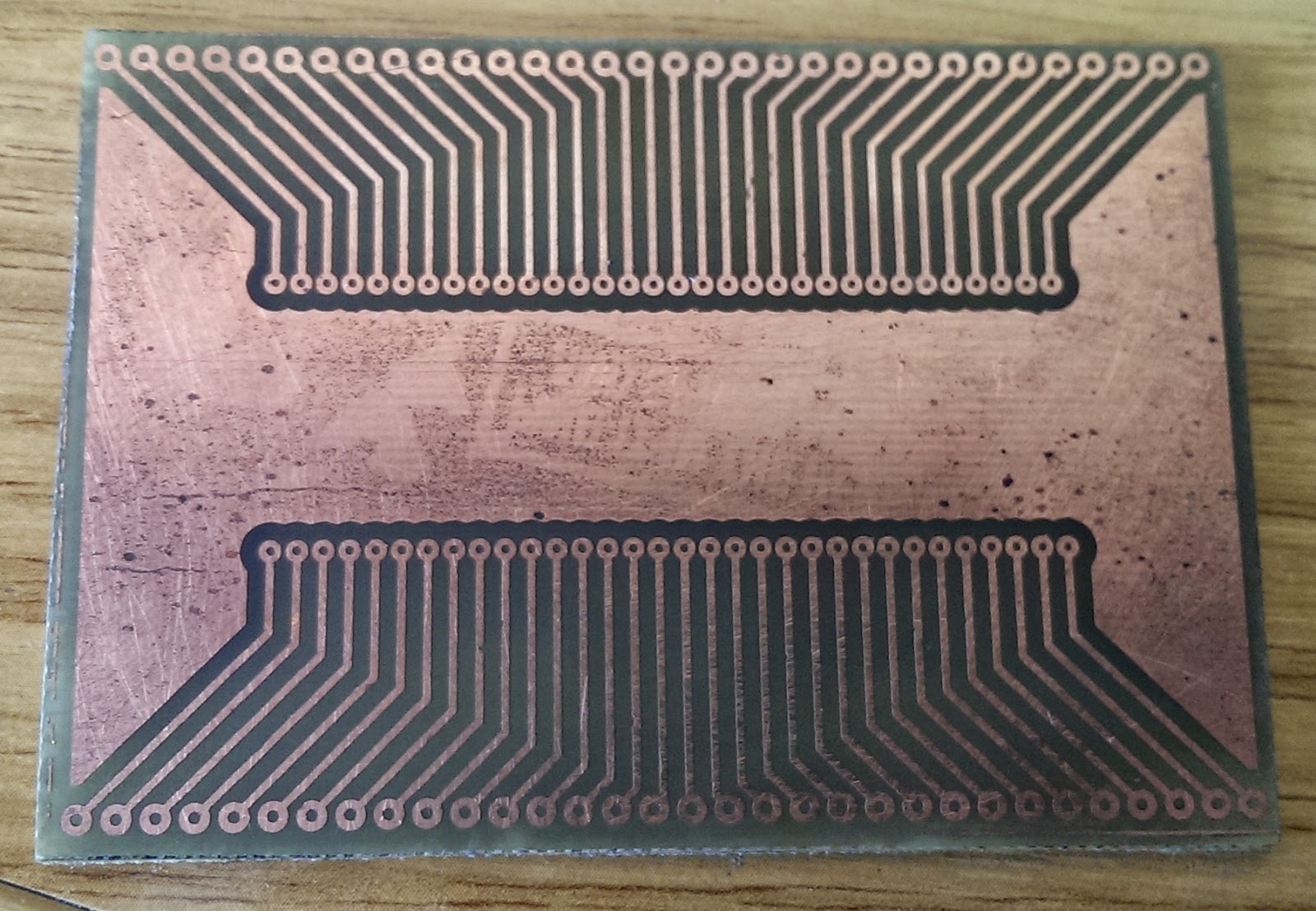

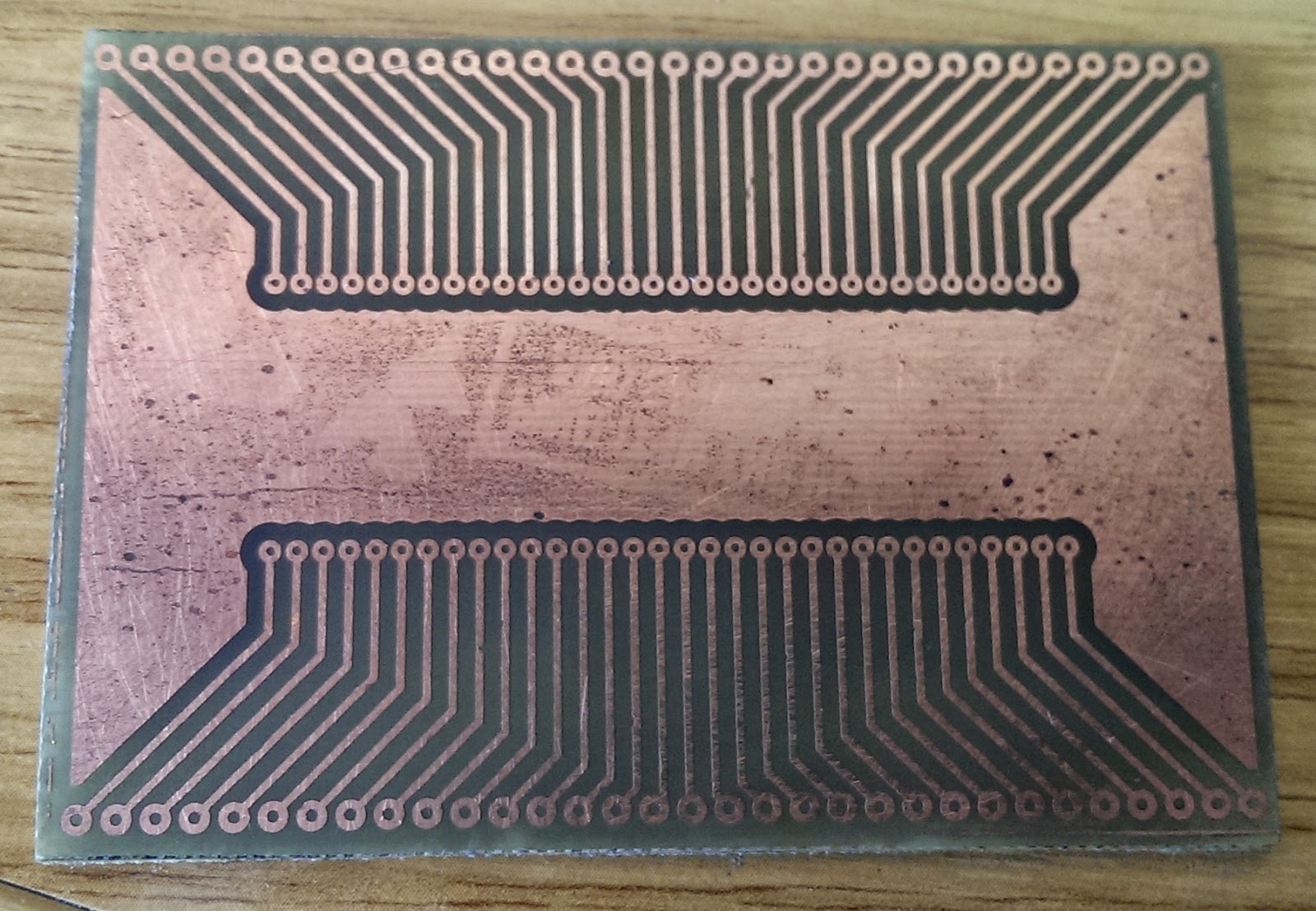

guys, a foolish question: where can i buy an adapter like to one in the figure ?

that guy has realized it to be home-made realized but i do not have the equipment to realize such a things, so … i could design it and ask a Service to realize it for me, or … buy it already done

it should be useful to "try & toy" with hardware configurations, e.g. try to use a SIM30, or a SIM72, or something like that