(The picture on the left is about twice actual size and only shows 10 positions, but the socket strips are available in much longer strips that can be cut to the needed size. I know there are WW ones too, but I can't find a picture of one right now.)

I envision the layout being something like:

Code: Select all

x x x x x x x x x x x x

x x x x x x x x x x x x x x x x x x x x x x

x x x x x x x x x x x x x x

x x x x x x x x x x x x x x

x x x x x x x x x x

x x x x x x OR x x x x

x x x x x x x x x x

x x x x x x x x x x

x x x x x x x x x x x x x x

x x x x x x x x x x x x x x

x x x x x x x x x x x x x x x x x x x x x x

x x x x x x x x x x x x

So I would hope the the FPGA gurus would make these special processors available to all who want to order them, and that the HDL be public domain so if one person doesn't feel like continuing the project, others are not orphaned.

I then realised that such a thing is called an FPGA breakout board. They exist, priced from $50 up. (It still might be worth designing one for our purposes and making a batch, or thinking of it as a business because existing breakout boards just don't have the right feature set.)

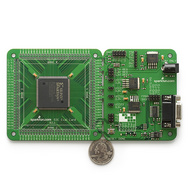

Here's an example. It's a two-part board - the left part has not quite enough and the right part adds a bit too much:

See also Pluto boards

Here are two more with around 50 I/Os, both of which have open source licenses, so could be a basis for a redesign:

- Papilio Arcade Megawing

skywired FPGA breakout board (thorough project write-up, for ham radio purposes)