My Mainboard Design

Posted: Mon Mar 14, 2011 6:55 pm

I've always wanted to build a computer. So lately I've been working on a design for a simple 6502 based machine. As I don't have a whole lot of electronics experience, I'm trying to keep things simple for now.

I've started working on a design, which you can download here. The generic logic gates are supposed to be high speed CMOS 74xx series chips. I didn't like the ones in gschem's default library, so I made my own. However, I've yet to properly set up the pin numbering and lables. (Just call me lazy.)

It's pretty basic at the moment, with 32K of SRAM at the bottom of the address space and 8K of FRAM at the top. The rest of the top half of the address space is currently unoccupied, but I plan to add IO space there (and possibly more RAM).

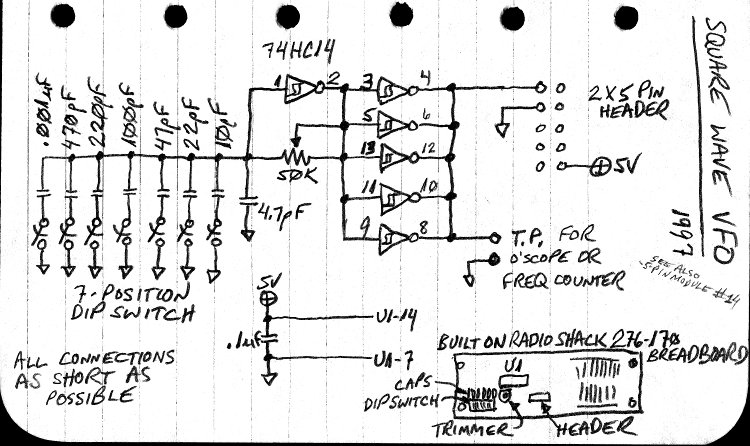

Clearly, there's some work still to be done. In particular, I cheated and black boxed the clock and reset circuits. Any pointers to resources on solid designs for them would be appreciated. I've noticed a lot of you start with a slower clock speed and then crank it up until it stops working. Do you just use a fixed clock and then swap out the crystals, or is you use a variable clock speed design? If the latter, how do you build one?

I'll appreciate any feedback you can give me, but I have a few specific questions.

Firstly, what should I do with the unused output pins? I know it's not a good idea to just let them float, but I don't know how to properly tie them off.

Secondly, the FRAM's datasheet says that, unlike an SRAM, /CE is edge triggered. On the falling edge, it latches /OE, /WE, and the address lines. So, to make sure /OE is in the proper state when latched, I used two AND gates in the FRAM's address decode. Is this proper design, or just overkill? I originally had one four input AND tied to both /CE and /OE, but then I changed it.

My current address decoding is pretty ad-hoc. I think it'll work alright, but as I start adding IO and stuff, it's sure to get more complicated. Is there a more systematic way of address decoding that's better, or should I just keep going with the random logic gate approach?

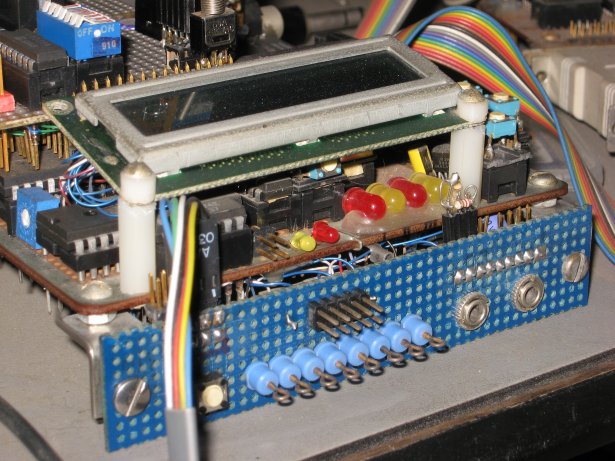

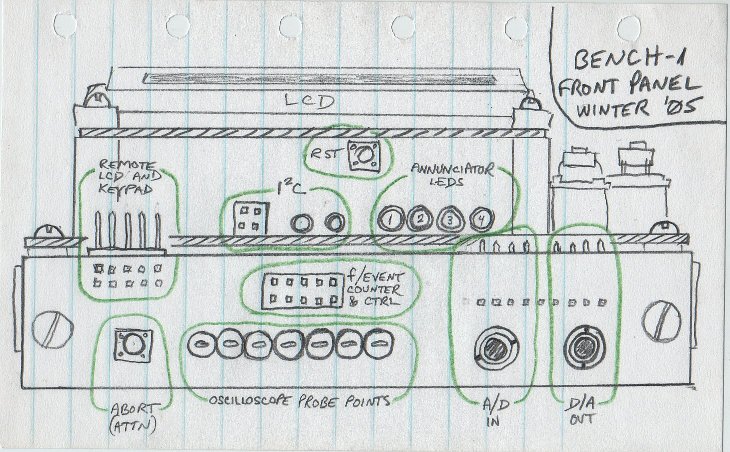

Finally, real computers have blikenlights. I want to add LEDs so you can see the state of the buses and stuff. (Probably more useful once I add a single stepping mode.) What's the proper way to do that and avoid causing problems?

Anyway, that's what I'm working on and wondering about. Any input you have would be greatly appreciated.

I've started working on a design, which you can download here. The generic logic gates are supposed to be high speed CMOS 74xx series chips. I didn't like the ones in gschem's default library, so I made my own. However, I've yet to properly set up the pin numbering and lables. (Just call me lazy.)

It's pretty basic at the moment, with 32K of SRAM at the bottom of the address space and 8K of FRAM at the top. The rest of the top half of the address space is currently unoccupied, but I plan to add IO space there (and possibly more RAM).

Clearly, there's some work still to be done. In particular, I cheated and black boxed the clock and reset circuits. Any pointers to resources on solid designs for them would be appreciated. I've noticed a lot of you start with a slower clock speed and then crank it up until it stops working. Do you just use a fixed clock and then swap out the crystals, or is you use a variable clock speed design? If the latter, how do you build one?

I'll appreciate any feedback you can give me, but I have a few specific questions.

Firstly, what should I do with the unused output pins? I know it's not a good idea to just let them float, but I don't know how to properly tie them off.

Secondly, the FRAM's datasheet says that, unlike an SRAM, /CE is edge triggered. On the falling edge, it latches /OE, /WE, and the address lines. So, to make sure /OE is in the proper state when latched, I used two AND gates in the FRAM's address decode. Is this proper design, or just overkill? I originally had one four input AND tied to both /CE and /OE, but then I changed it.

My current address decoding is pretty ad-hoc. I think it'll work alright, but as I start adding IO and stuff, it's sure to get more complicated. Is there a more systematic way of address decoding that's better, or should I just keep going with the random logic gate approach?

Finally, real computers have blikenlights. I want to add LEDs so you can see the state of the buses and stuff. (Probably more useful once I add a single stepping mode.) What's the proper way to do that and avoid causing problems?

Anyway, that's what I'm working on and wondering about. Any input you have would be greatly appreciated.