Page 7 of 15

Re: Breaking 6502 apart

Posted: Mon Aug 27, 2012 8:31 am

by BigEd

Switched Google code project to MIT License.

Thanks!

Ed

Re: Breaking 6502 apart

Posted: Fri Aug 31, 2012 3:30 pm

by org

Completed random logic at trans-level

Random logic interconnections with other 6502 parts:

Inputs

PHI1,PHI2: timing

Reset0: from RST pin

NMIG: from NMI pin logic

IRQP: from IRQ pin logic

/IR5: from instruction register, to determine CLC/SEC and others

SO: from SO pin, set V-flag

RDY: from RDY pin

BRKDONE, VEC: from interrupt priority logic

2 inputs from predecode logic.

129 lines from PLA.

AVR: overflow out from ALU

ACR: carry out from ALU

Outputs

TRES: reset T-counter

sync: shift T-counter, additionally output to SYNC pin

T0, T1X: first two steps of instruction decoding, to PLA

R/W: Goes to R/W pin and data latch

fetch: Force instruction register to load from Predecode Register

VEC0: to interrupt priority logic, when BRK detected

48 output drivers, to control bottom part.

Also random logic is connected with internal data bus (DB) to exchange status reg (flags).

Re: Breaking 6502 apart

Posted: Tue Sep 04, 2012 5:01 pm

by org

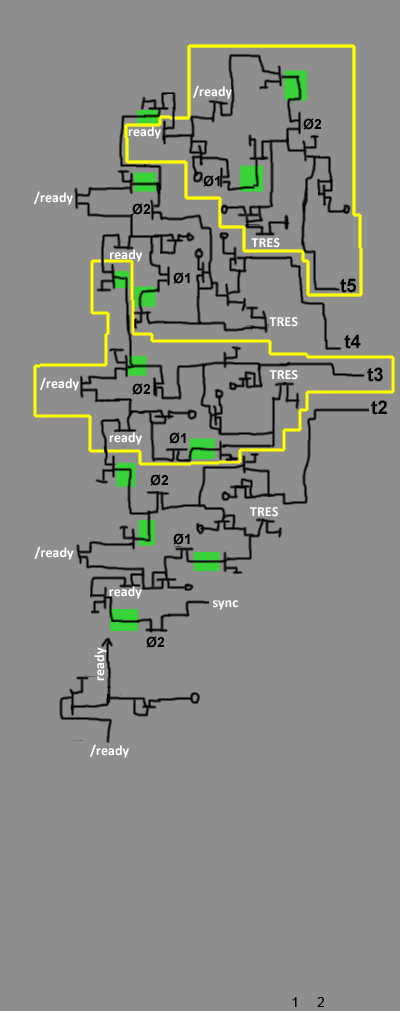

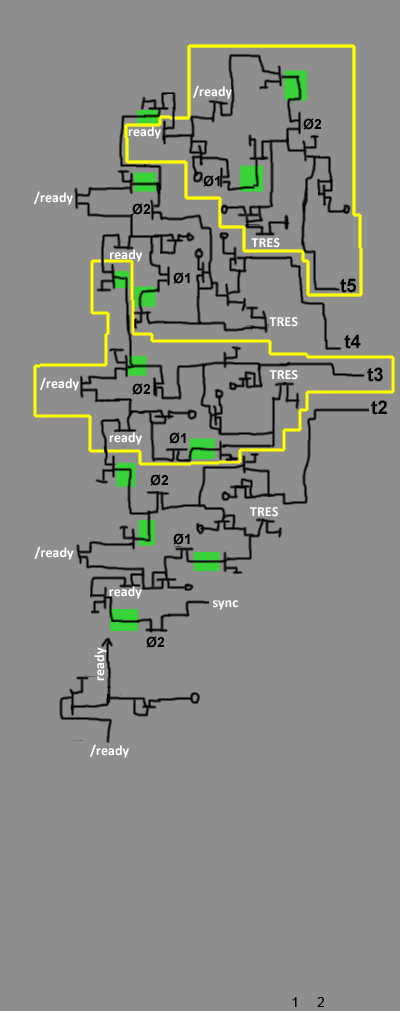

Fixed shortcut in T-step shift register:

Added C simulation:

http://code.google.com/p/breaks/source/ ... TIME_REG.c

+ modified first post.

Re: Breaking 6502 apart

Posted: Tue Sep 04, 2012 6:28 pm

by BigEd

All good! Please could you link to something like

http://code.google.com/p/breaks/source/ ... 6502%2FSRC

from the first post too?

Cheers

Ed

Re: Breaking 6502 apart

Posted: Wed Sep 05, 2012 12:29 pm

by org

Added address bus registers simulation + modified first post with direct links.

Re: Breaking 6502 apart

Posted: Thu Sep 06, 2012 5:59 am

by org

Added missing R/W distribution tri-state, which goes from random logic to data latch.

(attached)

- More clear picture of PLA for double-checking

- Started complete 6502 schematics (WIP)

- Complete PLA simulation here:

http://code.google.com/p/breaks/source/ ... /SRC/PLA.c

Re: Breaking 6502 apart

Posted: Mon Sep 10, 2012 11:29 am

by org

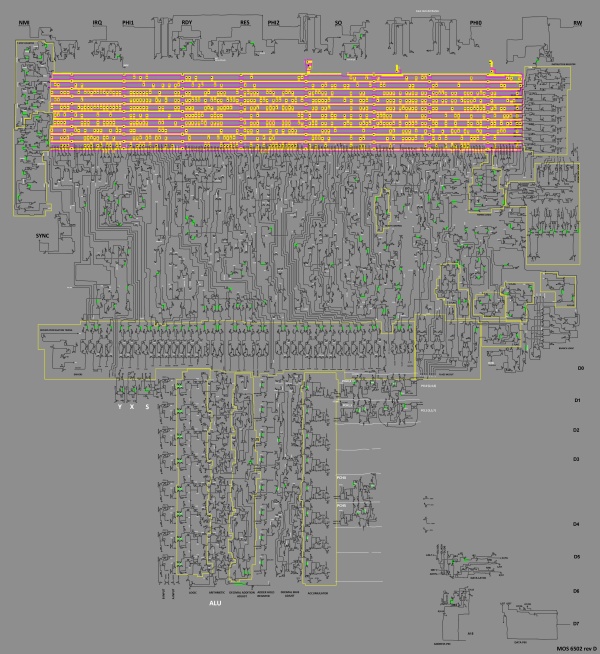

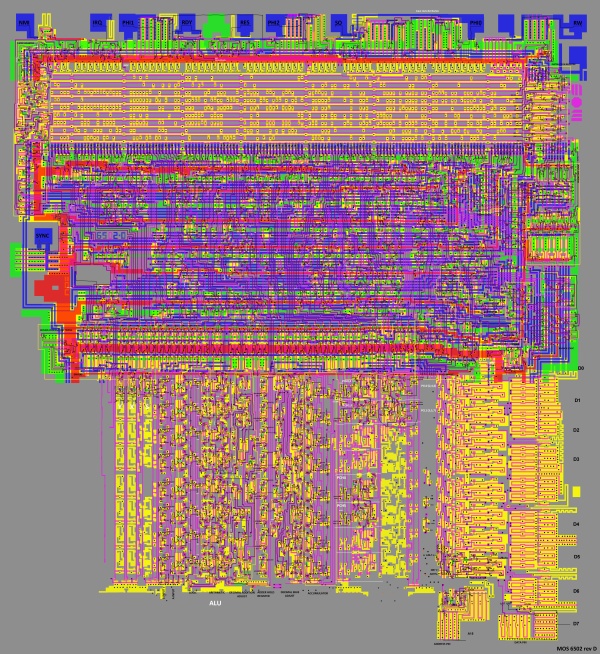

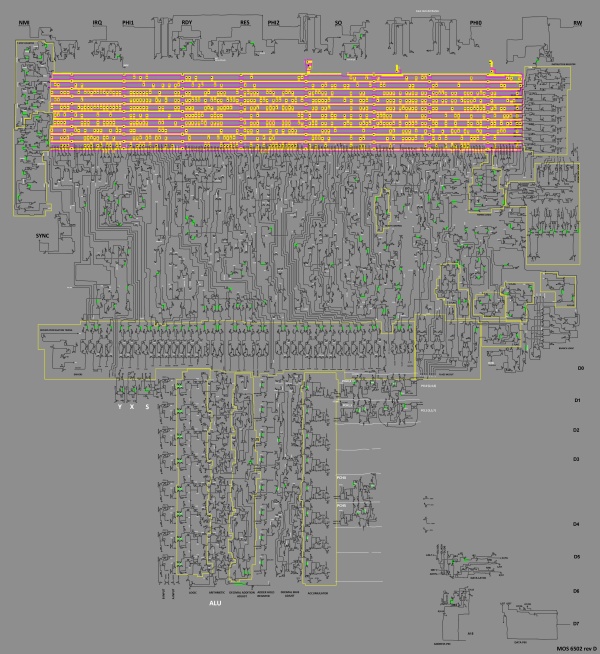

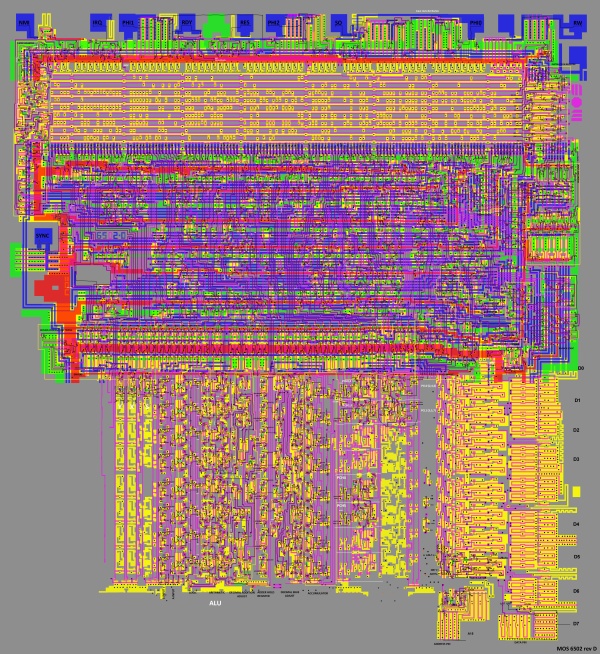

Almost complete 6502 schematics. Only left to add missing latches and fix small errors )

I decided not to draw PLA as transistors and left it just as color diagram.

Re: Breaking 6502 apart

Posted: Mon Sep 10, 2012 11:39 am

by BigEd

Nice progress! I've subscribed to the

RSS feed of your code project, and to

the feed for

your wiki.

Cheers

Ed

Re: Breaking 6502 apart

Posted: Mon Sep 17, 2012 12:55 pm

by org

I have a small break due to HDD failure, but thanks to Google Drive, I quickly restored all data.

Now I can present complete 6502 rev. D schematics. This part of my job is done here:

High-resoultion images can be found on google code project.

I uploaded photoshop sources here :

http://ogamespec.com/6502/sources.zip (~200 MB)

And updated most interesting parts (ALU and random logic) by recent changes:

http://ogamespec.com/6502/ALU.psd

http://ogamespec.com/6502/LOGIC.psd

(remember, this is not WIP anymore)

Re: Breaking 6502 apart

Posted: Mon Sep 17, 2012 1:31 pm

by BigEd

Very nicely done!

Re: Breaking 6502 apart

Posted: Mon Sep 24, 2012 4:51 pm

by org

Integrated simple assembler, to test 6502 operations in simulator.

ASM.c

ASMOPS.c

Re: Breaking 6502 apart

Posted: Thu Oct 04, 2012 10:38 am

by org

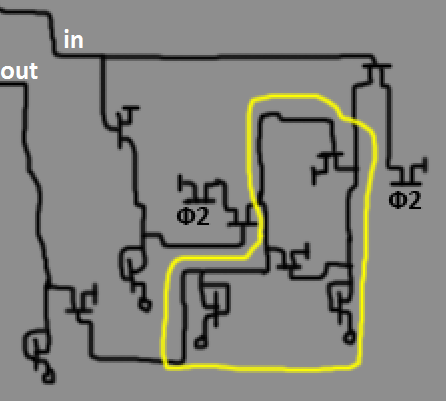

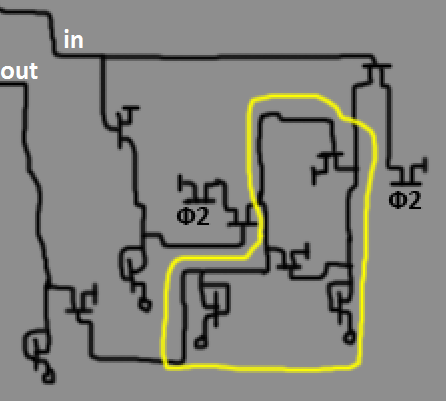

I started to simulate /NMI logic and I have problems, understanding a part of circuit.

Here:

I know, this is called bistable latch, but I dont understand it at all ))

The upper MOSFET is grounded at the same time, as bottom one.. Can you explain me what happen here )

EDIT: I found solution by myself

Code: Select all

static nout;

b = ~(~(in & Ф2) | nout);

nout = (~(~in & Ф2) | b);

out = ~nout;

Re: Breaking 6502 apart

Posted: Thu Oct 04, 2012 5:00 pm

by BigEd

I agree with the general form: it's a pair of NORs cross-coupled, with a final output inverter.

But I'm not completely sure about all the '~' operators.

I suppose you can see the result in simulation!

Cheers

Ed

Re: Breaking 6502 apart

Posted: Thu Oct 04, 2012 6:14 pm

by org

Simulation work badly ( And I cannot track the error...

Re: Breaking 6502 apart

Posted: Thu Oct 04, 2012 6:21 pm

by BigEd

How about

Code: Select all

static nout;

b = ~((in & Ф2) | nout);

nout = ~((~in & Ф2) | b);

out = ~nout;