Page 36 of 37

Re: POC VERSION TWO

Posted: Sun Jul 22, 2018 12:11 pm

by GaBuZoMeu

This looks very well!

It would be a tricky new(?) way to stretch the clock, one that should work even with a NMOS 6502 where RDY don't work for writes. I need to try to simulate that to be sure it works.

Thinking about that it just came to my mind if it would work to use GCLK to clock fast IO (like 65C22) having timers inside counting the clock. Then these counters and related timings would not disturbed by accessing slow IO.

Regards, Arne

Re: POC VERSION TWO POINT TWO: Wait-States

Posted: Sun Jul 22, 2018 3:13 pm

by Dr Jefyll

Green on a black background kinda sucks. (Oh! -- about the

circuit, you mean!

)

Don't forget the humble JK flipflop (below). I've drawn this using 'AC112, but with trivial changes the 'AC109 will also work. (With J and /K tied together the '109 can masquerade as a '74, which increases the potential utility of the other flipflop section in the package.) With this circuit it's better if your /STP signal becomes valid before the rise of Phi2 (but I assume that's already the case).

On another topic, I noticed the following portion of your schematic (below). Maybe eight of those nine jumpers can be omitted. Assuming the 'ACT541 is in a socket, it could, for testing purposes, be removed and replaced with a male header wired to simply bridge the inputs straight to the outputs (which is what the jumpers did). Of course the test would apply to all 8 of the signals -- IOW you can't pick & choose on an individual basis. That doesn't seem to me like a dealbreaker, though. If necessary you could use pullup resistors to alter the VOH of individual signals.

Re: POC VERSION TWO POINT TWO: Wait-States

Posted: Sun Jul 22, 2018 7:46 pm

by BigDumbDinosaur

The attachment clock_generator_2phase_modified.gif is no longer available

Green on a black background kinda sucks. (Oh! -- about the

circuit, you mean!

)

Picky, picky!

- Two-Phase Clock Generator w/Stop

Don't forget the humble JK flipflop (below). I've drawn this using 'AC112, but with trivial changes the 'AC109 will also work. (With J and /K tied together the '109 can masquerade as a '74, which increases the potential utility of the other flipflop section in the package.) With this circuit it's better if your /STP signal becomes valid before the rise of Phi2 (but I assume that's already the case).

Yes, that would work as well. Once advantage the 'AC74 has over the 'AC112 is the former is in a smaller package.

The CPLD logic is such that it would make a decision on wait-stating when

GCLK goes high. At that point, the effective address has settled and I have the whole of the

GCLK high phase in which to assert

/STP and stop everything. Similarly, when the wait-state expires,

/STP would be de-asserted during

GCLK high, keeping Ø2 in phase with

GCLK. In both case, so my thinking goes, the change of state of

/STP will always slightly lag the rise of

GCLK due to the CPLD's pin-to-pin delay (7-10ns), which should eliminate any glitches.

In any case, my main question is if my idea is even feasible.

On another topic, I noticed the following portion of your schematic (below). Maybe eight of those nine jumpers can be omitted. Assuming the 'ACT541 is in a socket...

The 'ACT541 is in an SOIC20 package, hence the jumper block.

Re: POC VERSION TWO

Posted: Sun Jul 22, 2018 7:55 pm

by BigDumbDinosaur

Thinking about that it just came to my mind if it would work to use GCLK to clock fast IO (like 65C22) having timers inside counting the clock. Then these counters and related timings would not disturbed by accessing slow IO.

Good observation.

POC VERSION TWO: V2.2 Update

Posted: Sat Aug 04, 2018 6:16 am

by BigDumbDinosaur

I added some circuitry to implement "clock stretching" to be used in lieu of RDY for generating wait-states. The clock control circuitry is arranged so I can isolate it with jumpers from the rest of the system for experimentation purposes. I also did some rearranging of the PCB in order to get a more favorable routing of the /IRQ line and some other traces. The updated schematic and PCB layout are attached. I will go over these once more in a day or two to double-check for errors, after which the Gerbers will be submitted to get boards made.

- Printed Circuit Board

Re: POC VERSION TWO

Posted: Sun Aug 05, 2018 10:21 pm

by GaBuZoMeu

Well, no response of anyone else so far.

I downloaded your schematic and take a glimpse on it - didn't find anything annoying

You have made no provisions for a (G)CLK signal on the expansion header - probably you intend no sort of extension that could benefit from that.

Regards.

Re: POC VERSION TWO

Posted: Sun Aug 05, 2018 10:49 pm

by BigDumbDinosaur

You have made no provisions for a (G)CLK signal on the expansion header - probably you intend no sort of extension that could benefit from that.

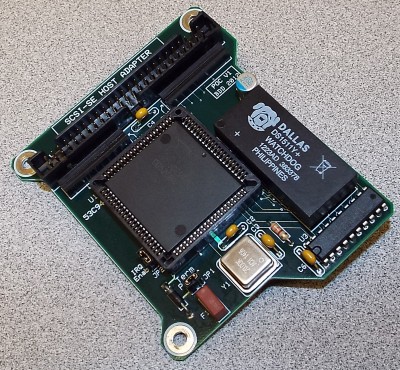

Anything that would be connected to the expansion socket would be using the Intel-style read/write circuitry and would not require reference to GCLK. The only peripheral I have built to date to plug into expansion is a SCSI host adapter, which has its own clock source.

- SCSI Host Adapter PCB

- SCSI-SE Host Adapter

Re: POC VERSION TWO

Posted: Wed Aug 21, 2019 9:56 pm

by BigDumbDinosaur

Like everything else, this project ended up on the back burner as I grappled with medical maladies. I was able to assemble the unit and do some preliminary testing before I ended up in the hospital. However, too much time has elapsed from then to now. So I need to start from scratch with testing—I have no recollection of how far I had gotten—and see if it will go or blow. Meanwhile, I'm in a race to catch up with client work I was doing when the hospital beckoned.

So I am not sure when I will be able to get back on this.

Meanwhile, here are some photos of POC V2.2 I had taken during and after assembly.

- POC V2.2 Bare PCB

- POC V2.2 PCB w/SMT Devices

- POC V2.2 Assembled

Re: POC VERSION TWO

Posted: Thu Aug 22, 2019 6:37 am

by drogon

Looks very nice. Good to see another '816 system going!

Cheers,

-Gordon

Re: POC VERSION TWO

Posted: Thu Aug 22, 2019 3:49 pm

by BigDumbDinosaur

Looks very nice. Good to see another '816 system going!

Cheers,

-Gordon

Thanks! Of course, I have no idea at this point if it will work.

POC VERSION TWO

Posted: Thu Aug 22, 2019 5:57 pm

by Guus Assmann

Hello,

Nice to know You're back.

And I'm still interested in putting the parts I already have to work.

BR/

Guus

Re: POC VERSION TWO

Posted: Sun Aug 25, 2019 4:31 am

by BigDumbDinosaur

Hello,

Nice to know You're back.

And I'm still interested in putting the parts I already have to work.

BR/

Guus

I hope to get back on this in a month or two. As I lost a fair amount of time while undergoing treatment and rehab, I have quite a bit of client work waiting for me. I best get to it, since I need to pay all those hospital and doctor bills.

Re: POC VERSION TWO

Posted: Thu Nov 07, 2019 7:20 am

by BigDumbDinosaur

I've given up for now on my homebrew computing escapades.

I cannot see well enough to do any close electronic work and writing code has gotten to be quite difficult thanks to damage to central vision in my left eye. I've tried, but I seem to routinely mix up instructions that are easily mixed up, e.g., TXA vs. TAX. I've been undergoing treatment for nearly two years in an attempt to mitigate the vision problems but am seeing little progress. I'd like to think that things will improve and I'll soon be back in the saddle writing code, etc. However, reality is what matters and that reality is I'm a curmudgeon with failing vision. So it seems my POC V2 project has become an orphan. It's been fun...

Re: POC VERSION TWO

Posted: Thu Nov 07, 2019 1:40 pm

by cbmeeks

BDD,

I'm so sorry to hear that! If you ever need help soldering stuff, let me know. I love doing it and I'm not too bad at it.

Anything I can do to help....

Re: POC VERSION TWO

Posted: Thu Nov 07, 2019 3:27 pm

by floobydust

Also very sorry to hear that your vision has prevented you from finishing up the hardware and from doing any programming. I'd also be willing to help out with anything on assembly, etc. if you like.