Page 4 of 4

Re: Looking for recommended 65C02/65C816 SBC for learning

Posted: Sat Apr 26, 2025 2:21 pm

by Dr Jefyll

[the clock oscillator is] from a Motorola CMOS design note

Yes, I thought that circuit looked familiar. And Neil reports that it's reliable in use, so I think it's fair to downplay BDD's concern in this regard.

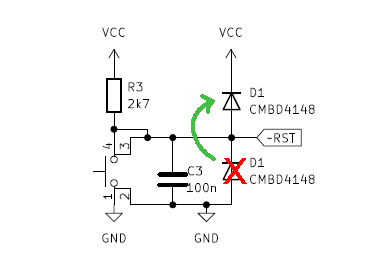

Regarding the reset circuit, the '4148 diode appears (due to a typo?) in an illogical place.

- reset circuit .png (8.69 KiB) Viewed 2719 times

As originally drawn (between ground and -Rst) the diode will never conduct, and may as well be omitted.

Instead I believe it ought to be between -Rst and Vcc. In the rare but dangerous circumstance of Vcc sharply dropping from 5 volts to zero (as when an accidental short occurs), the diode ensures that the voltage on the capacitor also gets pulled low. This addresses the very real risk of the CPU getting fried.

(I mean fried in the sense that the reset input of the CPU would get damaged by the voltage on the cap, which would momentarily exceed that of the CPU Vcc pin which is at zero. IOW, without the '4148 diode, the cap will get discharged by the CPU's reset input instead.)

-- Jeff

Re: Looking for recommended 65C02/65C816 SBC for learning

Posted: Sat Apr 26, 2025 4:40 pm

by GARTHWILSON

True, dat!

Are there any cheap and cheerful supervisor chips out there that monitor both incoming Vcc _and_ a system clock before releasing ~reset? It's possible that using a time-based supervisor may beat the clock to the reset.

Serial to parallel shift register? Will the ~reset get to the last output before the clock has been stable at least two cycles?

PIC microcontrollers, which I've put in a dozen products, have a couple of related timers onboard, one being the power-up timer which waits around 100ms (regardless of oscillator frequency) for the power supply to stabilize, and then when it times out, the oscillator start-up timer begins its count of 1024 oscillator periods before releasing the internal reset. I think the latter is bypassed if, in your configuration word which is implemented before the processor even comes out of reset, you've told it you're using an RxC clock rather than a crystal, since the RxC clock oscillator starts up in a single cycle.

Re: Looking for recommended 65C02/65C816 SBC for learning

Posted: Sat Apr 26, 2025 4:53 pm

by BruceRMcF

MCP130 is a cheap supervisor in TO92 package.

There you go.

True, dat!

Are there any cheap and cheerful supervisor chips out there that monitor both incoming Vcc _and_ a system clock before releasing ~reset? It's possible that using a time-based supervisor may beat the clock to the reset.

Neil

Datasheet says the MCP130 typically holds RESET low for 350ms, so IIUC, the clock should be settled without needing a clock pin for that particular supervisor.

Re: Looking for recommended 65C02/65C816 SBC for learning

Posted: Sat Apr 26, 2025 5:40 pm

by BigDumbDinosaur

MCP130 is a cheap supervisor in TO92 package.

Also, the Maxim DS1813, although not as inexpensive as the MCP130. However, the DS1813 will respond to the reset line being grounded and will initiate a timed cycle when that happens—Microchip’s part won’t do that. Instead, a little Mickey Mouseity is required to get a reliable manual reset with the MPC130.

Both the DS1813 and MPC130 have internal pullup resistors, which are around 5K. In my POC units, I use an external 3.3K pullup as well, as I feel 5K makes the reset circuit somewhat noise-sensitive.

A power-on reset circuit also can be fashioned from a spare Schmitt-triggered gate, resistor and capacitor. Or, you could use the ubiquitous 555 timer, which is what generated the reset in the Commodore 64.

In the olden days when the 65C02 had a Schmitt-triggered reset input, an R-C network was all that was needed to properly reset the MPU at power on. Alas, that level of simplicity is no longer possible with WDC parts.

Re: Looking for recommended 65C02/65C816 SBC for learning

Posted: Sat Apr 26, 2025 5:43 pm

by BigDumbDinosaur

Regarding the reset circuit, the '4148 diode appears (due to a typo?) in an illogical place...Instead I believe it ought to be between -Rst and Vcc...

Good catch! You must’ve been on your second cup of coffee when you spotted that.

Re: Looking for recommended 65C02/65C816 SBC for learning

Posted: Sat Apr 26, 2025 7:40 pm

by L0uis.m

Hello 0010 all,

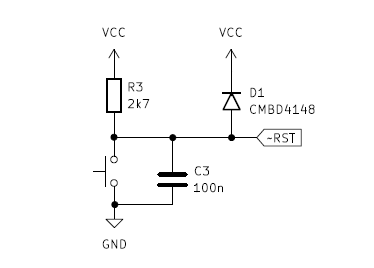

When I viewed the diagram above, for a moment I thought "Ehh?" so I boiled it down to its essence:

- Boiled down.png (5.08 KiB) Viewed 2691 times

I actually only did this for myself but when I saw the result I thought "Why not", so here it is.

Re: Looking for recommended 65C02/65C816 SBC for learning

Posted: Sat Apr 26, 2025 8:04 pm

by Michael

Speaking of reset circuits... I used a little 8-pin

PIC16F18313 chip (currently $1.16 single quantity at Mouser) awhile back to provide an econo' reset function as well as CPU and ACIA clock signals. With the least bit of encouragement I could create an Arduino 'sketch' to allow programming the PIC microcontroller with a relatively inexpensive Arduino Nano (or Uno) clone.

Here's an excerpt from the attached PIC microcontroller ASM source;

Code: Select all

;

; set 'CLKR_div' constant for desired 65C02 clock frequency.

;

; 6 -> 0.5-MHz (Fosc / 64)

; 5 -> 1.0-MHz (Fosc / 32)

; 4 -> 2.0-MHz (Fosc / 16)

; 3 -> 4.0-MHz (Fosc / 8)

; 2 -> 8.0-MHz (Fosc / 4)

; 1 -> 16.0-MHz (Fosc / 2)

;

CLKR_div equ 4 ; 2.0-MHz PHI0 CPU clock

;

; set 'NCO1_inc' constant for desired ACIA clock output.

;

; 2517 -> 38400-Hz ( 2400 * 16) @ 0.01659%

; 5033 -> 76800-Hz ( 4800 * 16) @ 0.00327%

; 10066 -> 153600-Hz ( 9600 * 16) @ 0.00327%

; 20133 -> 307200-Hz ( 19200 * 16) @ 0.00169%

; 40265 -> 614400-Hz ( 38400 * 16) @ 0.00079%

; 60398 -> 921600-Hz ( 57600 * 16) @ 0.00004%

; 120796 -> 1843200-Hz (115200 * 16) @ 0.00004%

; 241592 -> 3686400-Hz (230400 * 16) @ 0.00004%

;

NCO1_inc equ 120796 ; 1.8432-MHz (115200 * 16)

Re: Looking for recommended 65C02/65C816 SBC for learning

Posted: Mon Apr 28, 2025 4:02 pm

by enso1

Careful, Michael, you may start sounding like a PIC or Arduino salesman!