Page 4 of 6

Re: 65c816 "Core"

Posted: Wed Sep 08, 2021 5:56 pm

by BigDumbDinosaur

I took BDD's advice and changed the memory mapping a little. Here's the decoder circuit sheet.

Could you please post the new memory map? It may help with trying to figure out why you have enough gates in there to sink a small ship.

Also, I recommend you do not mix TTL logic with CMOS. 74HC devices will not see a valid logic 1 at their inputs if driven from TTL outputs. At best, the circuit will function, but likely be unstable. At worst, it won't work at all.

Re: 65c816 "Core"

Posted: Wed Sep 08, 2021 9:53 pm

by GamerFox

Re: 65c816 "Core"

Posted: Thu Sep 09, 2021 7:46 am

by BigDumbDinosaur

You do know you can attach things to your posts, right? I (and a few others around here) don't do Google for anything.

Re: 65c816 "Core"

Posted: Thu Sep 09, 2021 12:08 pm

by GamerFox

You do know you can attach things to your posts, right? I (and a few others around here) don't do Google for anything.

Re: 65c816 "Core"

Posted: Thu Sep 09, 2021 7:43 pm

by BigDumbDinosaur

You do know you can attach things to your posts, right? I (and a few others around here) don't do Google for anything.

Now, where have I seen that memory map before?

That memory map can be implemented with fewer gates than what you previously posted.

The above is an excerpt from my POC V1.3 unit's schematic. The unit has 128KB of RAM, of which 112KB is accessible.

Re: 65c816 "Core"

Posted: Thu Sep 09, 2021 8:06 pm

by GamerFox

You do know you can attach things to your posts, right? I (and a few others around here) don't do Google for anything.

Now, where have I seen that memory map before?

That memory map can be implemented with fewer gates than what you previously posted.

pocv130_glue.pdf

The above is an excerpt from my POC V1.3 unit's schematic. The unit has 128KB of RAM, of which 112KB is accessible.

What's that signal /WSE there?

Re: 65c816 "Core"

Posted: Thu Sep 09, 2021 8:21 pm

by barrym95838

What's that signal /WSE there?

My hardware chops are a bit limited, but it looks to me like it's an output that's low for any bank 0 address in [$C000 .. $FFFF]. What the name means is something BDD should be able to answer.

Re: 65c816 "Core"

Posted: Thu Sep 09, 2021 8:35 pm

by floobydust

I believe that's from his V2.0 design... it's Wait State Enable for anything in the I/O address block. Check out the full schematic under the Hardware Section:

viewtopic.php?f=4&t=6701#p85562

Re: 65c816 "Core"

Posted: Thu Sep 09, 2021 10:37 pm

by BigDumbDinosaur

What's that signal /WSE there?

Wait-State Enable.

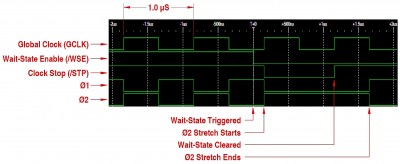

When /WSE is asserted Ø2 is stopped (aka "stretched") in the high phase, resulting in a wait-state. Stretching avoids problems that may arise in trying to wait-state the 65C816 by controlling RDY. The clock generator circuit is in the below attachment.

- Clock Generator w/Stretch Control

The generator circuit was derived from a prototype unit I built to prove the concept. The logic analyzer results for the prototype are below.

- Clock-Stretching Logic Traces

Of the three clock outputs picked off at RN1, GCLK ("global clock") is not stretched and can be used to drive 65xx peripherals, such as the WDC 65C22. In particular, if the 65C22 is driven from Ø2, its timers will gradually slow down with each I/O or ROM access. Driving the 65C22 from GCLK avoids this problem. Implied in this case is that wait-stating would not be applied if the selected device is a 65C22. As I don't use the 65C22 I didn't include that "rule" in the glue logic. Such a rule might be awkward to implement in discrete logic, but wouldn't be a problem with a PLD.

Jumper JP1 on the left selects one or two wait-states. I added that feature to POC V2.0's clock generator for experimentation purposes.

I believe that's from his V2.0 design...

...also used in V1.3.

My hardware chops are a bit limited, but it looks to me like it's an output that's low for any bank 0 address in [$C000 .. $FFFF].

Correct.

Re: 65c816 "Core"

Posted: Fri Sep 10, 2021 7:47 am

by GamerFox

So it's probably not going to be relevant to my design?

Re: 65c816 "Core"

Posted: Sat Sep 11, 2021 12:49 am

by BigDumbDinosaur

So it's probably not going to be relevant to my design?

That's something you will have to decide. The need for wait-stating will depend on how fast you want to run your system and the performance of the parts you use to build it.

Re: 65c816 "Core"

Posted: Sat Sep 11, 2021 5:21 am

by GamerFox

This is kind of a test bed for me right now so I'm thinking no more than 4 MHz.

Re: 65c816 "Core"

Posted: Sat Sep 11, 2021 5:43 am

by BigDumbDinosaur

This is kind of a test bed for me right now so I'm thinking no more than 4 MHz.

Unless you use some really slow stuff you won't need wait-states at 4 MHz. Just remember what I earlier said about mixing TTL and CMOS logic. There is no valid reason at this time to use TTL logic in a new design.

Re: 65c816 "Core"

Posted: Sun Sep 12, 2021 5:36 am

by GamerFox

I am a little bit angry right now. It seems like there are no DIP EPROM or EEPROMs that work on 3.3V, meaning I might have to jack up the main rail to 5V or add a PLCC32 socket for one of Atmel's 3.3V offerings (the OTP EPROM and the EEPROM are not pin compatible in PLCC32).

Re: 65c816 "Core"

Posted: Sun Sep 12, 2021 6:07 am

by barrym95838

I just did a brief search and found the

28LV010 which appears to have a DIP version ... is this not available or not applicable for some reason?

[Edit: might be for aerospace use, so rare and expensive?]