jmp(FFFA), to reply without quoting everything:

There's a performance comparison at

http://westerndesigncenter.com/wdc/AN-0 ... risons.cfm . The Sieve of Eratosthenes benchmark is blank for the 68K, but I remember seeing elsewhere that the '816 compared favorably to the 68K.

I know 68K enthusiasts definitely like the programmer's model. It is more suitable for certain compiled languages like C. The 6502's extended set of registers is of course zero page, and the 816's is the direct page which is like zero page but renamed because it can be relocated, and every task can have its own DP. (The '816 is much better suited to things like multitasking and relocatable code than the 6502 is.) BigEd

observed, "With 6502, I suspect more than one

beginner has wondered why they can't do arithmetic or logic operations on X or Y, or struggled to remember which addressing modes use which of the two. And then the

intermediate 6502 programmer will be loading and saving X and Y while the

expert always seems to have the right values already in place."

On the segmented memory, the 65Org32 (so-far-vaporware-only) all-32-bit 65816, the bank registers are 32-bit also, serving as offsets for various tasks' beginning addresses but eliminating the 64K boundaries. The 65816's bank boundaries are transparent in long addressing; but without using long addressing all the time, the key is to make the boundaries work

for you instead of

against you, just as one does with zero page (and on the '816, "direct page," since it can be relocated). The shorter addresses in operands and tables were a benefit especially when memory was far more expensive than it is today.

In the Apple IIgs, the '816 was definitely capable of more than 2.8MHz, but Steve Jobs wanted it held down because he didn't want the IIgs to make the Macs looks bad.

I believe the 68K took 46 clocks for the interrupt acknowledge and interrupt sequence. The 816's is 8 clocks, one more than the 6502's, because it pushes the program bank. Programming manuals usually show ISR examples that are much longer than normally needed, just to cover all their bases, since they don't know your particular situation and they want to make sure they push and initialize everything including things you won't need in many situations.

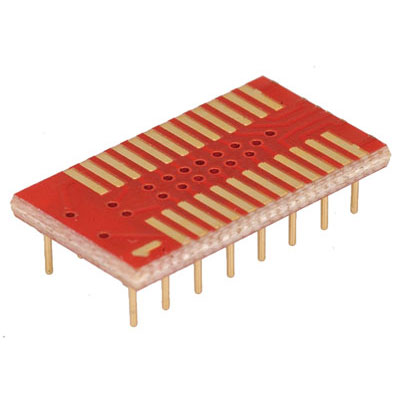

It is unfortunate that so many ICs are not available in DIP form; but fortunately we can get adapters that are easy to use, like this one from Jameco:

- DIP-SOIC_adapter.jpg (20.12 KiB) Viewed 2106 times

There are also thru-hole PLCC sockets, even wire-wrap ones (although the WW ones are expensive and hard to find):

- WW_PLCC_44.jpg (13.3 KiB) Viewed 2106 times

The 6522's shift register can only go one direction at a time, so you'd need two for full duplex SPI. I think all the SPI ICs I've used used only one direction at a time though, with dummy data going in the other direction. If you do use the SR, sending a byte is as simple as STA VIA_SR. 16 clocks later, you can do it again, if it's running at half the phase-2 rate. If you can get the next byte to send any sooner, you could check the status but it would be more efficient to just put in a NOP or something like that. If you were transferring a block of data like for an SPI serial memory, you might have for example:

Code: Select all

FOR_X 0, TO, <length>

LDA <array>, X

STA VIA1_SR

NOP ; (for delay to prevent overrun)

NEXT_X

and keep the SPI busy pretty much full time. If you were transferring data to and from an SPI-interfaced UART, you would of course have to add code to keep watching to make sure you don't overrun the transmit buffer or re-read already-read bytes from the receive buffer.

I do like the I²C protocol a lot. I think very few devices can handle 5MHz clock rate, and other devices on the bus will need the slower clock rate just so they don't foul things up by responding incorrectly to start and stop conditions and addresses.

I have only bit-banged both SPI and I²C myself. The

circuit potpourri page of my

6502 primer has circuits I've used, and links to accompanying source code, and also Jeff Laughton's tricks for fast (single-cycle) I/O with the 65c02. If you bit-bang with his tricks, producing a clock pulse, ie, a rising edge and a falling edge, takes a grand total of 2 cycles. Otherwise it takes usually 12, for INC, DEC, putting the clock line on a 6522's port's bit 0 so you can change just the one bit with these instructions. Put incoming data on bit 6 or 7 so you can test it with BIT without having to use AND.