Page 3 of 15

Re: Breaking 6502 apart

Posted: Mon Jul 09, 2012 2:21 pm

by org

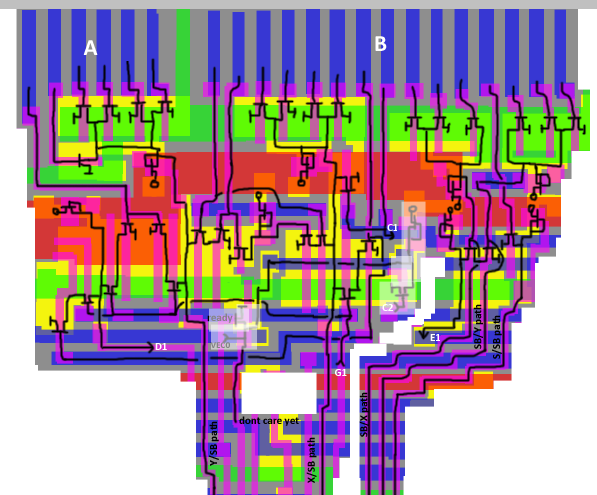

More progress on crazy logic :

Image no longer available: http://ogamespec.com/imgstore/whc4ffae6ac6ec5a.jpg

I began to understand how it works in general

PLA outputs are joined in "groups".

Groups on the left works with X,Y and S registers (resided underneath).

Groups on the middle are ALU related, which feed its inputs.

Groups on the right are branch/flag/compare and (possibly) interrupt/reset logic; instructions related to program counter (PC is resided on the bottom right side of the 6502).

Also there is intense metall layer crosspassing from the left to the right, for addressing calculations purposes.

Hope to crunch it fast, when I get full color schematics (good for LSD trips BTW

)

Re: Breaking 6502 apart

Posted: Mon Jul 09, 2012 5:05 pm

by org

In case someone interested, Visual6502 wiki has hidden section, which I found by poking Random page:

http://visual6502.org/wiki/index.php?ti ... atic_Notes

There is poor photos of 6502 blueprints.

Re: Breaking 6502 apart

Posted: Tue Jul 10, 2012 1:14 pm

by Unseen

There is poor photos of 6502 blueprints.

Actually it's not a photo but a size-reduced version of a scan of the blueprint. A photo would have no or different artifacts at the places where overlapping sections are merged.

Re: Breaking 6502 apart

Posted: Wed Jul 11, 2012 6:04 am

by org

I mean images ) Sorry my language )

Re: Breaking 6502 apart

Posted: Wed Jul 11, 2012 1:02 pm

by org

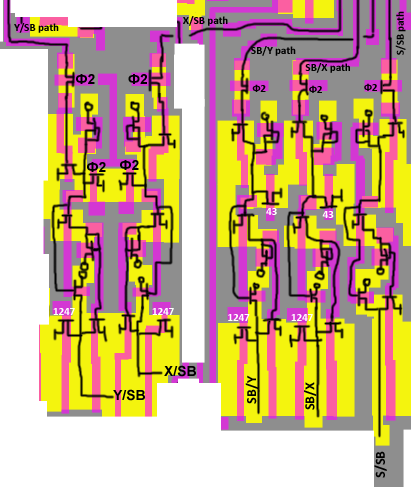

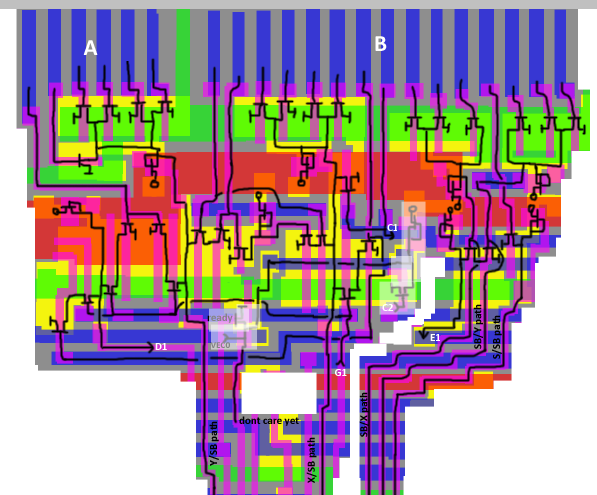

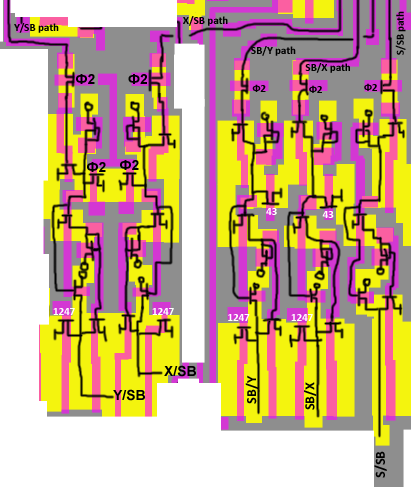

Todays speccy: Random logic A/B groups.

I separated PLA outputs on groups A,B,C,D,E,F,G,H and K.

Here is preview of below schematics :

Image no longer available: http://ogamespec.com/imgstore/whc4ffd765f41d7c.jpg

Top part:

Bottom part:

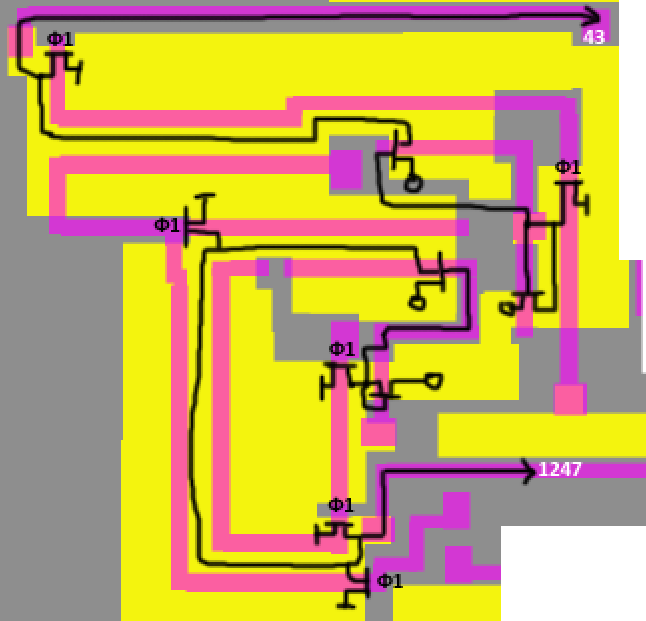

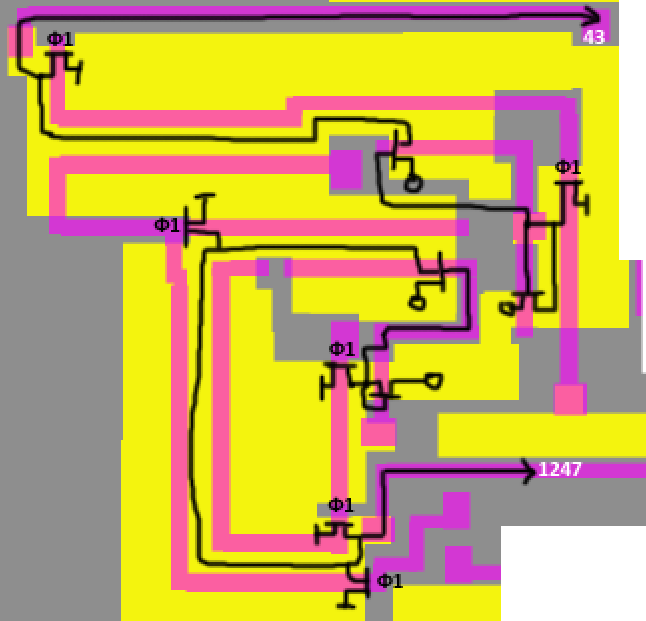

Also there is small logic to generate internal 43 and 1247 lines, which are used on bottom part:

(I do not understand wtf is it... some kind of /Ф1 power-up?)

I labeled interconnections between groups by white text.

Re: Breaking 6502 apart

Posted: Wed Jul 11, 2012 7:19 pm

by org

More progress on ALU:

Image no longer available: http://ogamespec.com/imgstore/whc4ffdd1751cca0.jpg

Re: Breaking 6502 apart

Posted: Thu Jul 12, 2012 12:42 pm

by org

I updated my PLA utility :

http://ogamespec.com/6502/decoder.htm

Now you can input raw bits from PLA lines and get IR mask as well as T-cycle on output.

msb bit in sequence is equal to bottom PLA line (t1).

A

000101100000100100000

000000010110001000100

000000011010001001000

010100011001100100000

010101011010100100000

010110000001100100000

B

000000100010000001000

000001000000100010000

000000010101001001000

010101011001100010000

010110011001100010000

011010000001100100000

000101000000100010000

010101011010100010000

011001000000100010000

000110011001100010000

001010011001100100000

011001011010100010000

000100011001100100000

011001100000100100000

011001000001100100000

C

011001010101010100000

000101010101010100001

010100011001010100000

001010010101010100010

001000011001010100100

000110010101010100001

001010000000010010000

000000000000000001000

010110000000011000000

000010101001010100000

000000101001000001000

010101000000011000000

000000000100000001000

010000000000000000000

000000010001010101000

000000000001010100100

D

000001010101010100010

000110010101010100010

000000010101001000100

000000010110001000010

000000010110001001000

...

K

000000011001010100000 ->

010010011010100100000

000001000000000000000

000000101001000000100

000000100101000001000

000000010100001000001

0000000010100?0000010 ? is actually 0, but strange.. supposed to be vias there

000000000000010000000

001001011010100100000

00000001100000000 <-

Re: Breaking 6502 apart

Posted: Fri Jul 13, 2012 9:29 am

by org

Completed random logic color schematics.

Also I choosed another strategy to reverse this whole crap. I start from T0 only PLA lines, then continue on T1 lines only and so on.

Re: Breaking 6502 apart

Posted: Fri Jul 13, 2012 7:21 pm

by org

Completed ALU color map.

Re: Breaking 6502 apart

Posted: Fri Jul 13, 2012 7:35 pm

by BigEd

quick progress! But you missed a horizontal run of poly - see pic.

Cheers

Ed

Re: Breaking 6502 apart

Posted: Fri Jul 13, 2012 7:52 pm

by org

Ehhehe, damn puzzle

I'll fix it in transistor level schematics )

EDIT: you don't need this poly line, it somes from from address latch )

EDIT2: ooops, or maybe need )

Re: Breaking 6502 apart

Posted: Sat Jul 14, 2012 11:18 am

by org

Todays speccy: ALU bit0

Pieces from left-to-right: B INPUT (BI), A INPUT (AI), LOGIC, ARITHMETIC, DECIMAL ADDER, ADDER HOLD REG (ADD), DECIMAL ADJUST, ACCUMULATOR (AC).

Re: Breaking 6502 apart

Posted: Sat Jul 14, 2012 11:36 am

by BigEd

Decimal adjust is a big random tangle! It's also not organised by bit slices. Joyful!

Re: Breaking 6502 apart

Posted: Sat Jul 14, 2012 11:38 am

by org

Re: Breaking 6502 apart

Posted: Mon Jul 16, 2012 9:27 am

by org

Todays speccy : PLA lines decoded!

Code: Select all

A

01: 000101100000100100000 100XX100 TX STY

02: 000000010110001000100 XXX100X1 T3 OP ind, Y

03: 000000011010001001000 XXX110X1 T2 OP abs, Y

04: 010100011001100100000 1X001000 T0 DEY INY

05: 010101011010100100000 10011000 T0 TYA

06: 010110000001100100000 1100XX00 T0 CPY INY

B

01: 000000100010000001000 XXX1X1XX T2 OP zpg, X/Y & OP abs, X/Y

02: 000001000000100010000 10XXXX1X TX LDX STX A<->X S<->X

03: 000000010101001001000 XXX000X1 T2 OP ind, X

04: 010101011001100010000 1000101X T0 TXA

05: 010110011001100010000 1100101X T0 DEX

06: 011010000001100100000 1110XX00 T0 CPX INX

07: 000101000000100010000 100XXX1X TX STX TXA TXS

08: 010101011010100010000 1001101X T0 TXS

09: 011001000000100010000 101XXX1X T0 LDX TAX TSX

10: 000110011001100010000 1100101X TX DEX

11: 001010011001100100000 11101000 TX INX

12: 011001011010100010000 1011101X T0 TSX

13: 000100011001100100000 1X001000 TX DEY INY

14: 011001100000100100000 101XX100 T0 LDY

15: 011001000001100100000 1010XX00 T0 LDY TAY

C

01: 011001010101010100000 00100000 T0 JSR

02: 000101010101010100001 00000000 T5 BRK

03: 010100011001010100000 0X001000 T0 Push

04: 001010010101010100010 01100000 T4 RTS

05: 001000011001010100100 0X101000 T3 Pull

06: 000110010101010100001 01000000 T5 RTI

07: 001010000000010010000 011XXX1X TX ROR

08: 000000000000000001000 XXXXXXXX T2 T2 ANY

09: 010110000000011000000 010XXXX1 T0 EOR

10: 000010101001010100000 01X01100 TX JMP

11: 000000101001000001000 XXX011XX T2 RIGHT R ODD

12: 010101000000011000000 000XXXX1 T0 ORA

13: 000000000100000001000 XXXX0XXX T2 LEFT ALL

14: 010000000000000000000 XXXXXXXX T0 T0 ANY

15: 000000010001010101000 0XX0X000 T2 BRK JSR RTI RTS Push/pull

16: 000000000001010100100 0XX0XX00 T3 BRK JSR RTI RTS Push/pull + BIT JMP

D

01: 000001010101010100010 00X00000 T4 BRK JSR

02: 000110010101010100010 01000000 T4 RTI

03: 000000010101001000100 XXX000X1 T3 OP X, ind

04: 000000010110001000010 XXX100X1 T4 OP ind, Y

05: 000000010110001001000 XXX100X1 T2 OP ind, Y

06: 000000001010000000100 XXX11XXX T3 RIGHT ODD

07: 001000011001010100000 0X101000 TX Pull

08: 001010000000100010000 111XXX1X TX INC NOP

09: 000000010101001000010 XXX000X1 T4 OP X, ind

10: 000000010110001000100 XXX100X1 T3 OP ind, Y

11: 000010010101010100000 01X00000 TX RTI RTS

12: 001001010101010101000 00100000 T2 JSR

13: 010010000001100100000 11X0XX00 T0 CPY CPX INY INX

14: 010110000000101000000 110XXXX1 T0 CMP

15: 011010000000101000000 111XXXX1 T0 SBC

16: 011010000000001000000 X11XXXX1 T0 ADC SBC

17: 001001000000010010000 001XXX1X TX ROL

E

01: 000010101001010100100 01X01100 T3 JMP

02: 000001000000010010000 00XXXX1X TX ASL ROL

03: 001001010101010100001 00100000 T5 JSR

04: 000000010001010101000 0XX0X000 T2 BRK JSR RTI RTS Push/pull

05: 010101011010100100000 10011000 T0 TYA

06: 100000000000011000000 0XXXXXX1 T1 UPPER ODD

07: 101010000000001000000 X11XXXX1 T1 ADC SBC

08: 100000011001010010000 0XX0101X T1 ASL ROL LSR ROR

09: 010101011001100010000 1000101X T0 TXA

10: 011010011001010100000 01101000 T0 PLA

11: 011001000000101000000 101XXXX1 T0 LDA

12: 010000000000001000000 XXXXXXX1 T0 ALL ODD

13: 011001011001100100000 10101000 T0 TAY

14: 010000011001010010000 0XX0101X T0 ASL ROL LSR ROR

15: 011001011001100010000 1010101X T0 TAX

16: 011001100001010100000 0010X100 T0 BIT

17: 011001000000011000000 001XXXX1 T0 AND

18: 000000001010000000010 XXX11XXX T4 RIGHT ODD

19: 000000010110001000001 XXX100X1 T5 OP ind, Y

F

01: 010000010110000100000 XXX10000 T0 <- Branch + BranchReady line

02: 000110011001010101000 01001000 T2 PHA

03: 010010011001010010000 01X0101X T0 LSR ROR

04: 000010000000010010000 01XXXX1X TX LSR ROR

05: 000101010101010101000 00000000 T2 BRK

06: 001001010101010100100 00100000 T3 JSR

07: 000101000000101000000 100XXXX1 TX STA

08: 000000010110000101000 XXX10000 T2 Branch

09: 000000100100000001000 XXXX01XX T2 zero page

10: 000000010100001001000 XXXX00X1 T2 ALU indirect

11: 000000001000000001000 XXXX1XXX T2 RIGHT ALL

12: 001010010101010100001 01100000 T5 RTS

13: 000000000000000000010 XXXXXXXX T4 T4 ANY

14: 000000000000000000100 XXXXXXXX T3 T3 ANY

15: 010100010101010100000 0X000000 T0 BRK RTI

16: 010010101001010100000 01X01100 T0 JMP

17: 000000010101001000001 XXX000X1 T5 OP X, ind

18: 000000001000000000100 XXXX1XXX T3 RIGHT ALL

G

01: 000000010110001000010 XXX100X1 T4 OP ind, Y

02: 000000001010000000100 XXX11XXX T3 RIGHT ODD

03: 000000010110000100100 XXX10000 T3 Branch

04: 000100010101010100000 0X000000 TX BRK RTI

05: 001001010101010100000 00100000 TX JSR

06: 000010101001010100000 01X01100 TX JMP

07: 000000011001010100000 0XX01000 TX Push/pull

08: 000101000000100000000 100XXXXX TX 80-9F

09: 000101010101010100010 00000000 T4 BRK

10: 000101011001010101000 00001000 T2 PHP

11: 000100011001010101000 0X001000 T2 Push

12: 000010101001010100010 01X01100 T4 JMP

13: 000010010101010100001 01X00000 T5 RTI RTS

14: 001001010101010100001 00100000 T5 JSR

H

01: 000110101001010101000 01001100 T2 JMP

02: 001000011001010100100 0X101000 T3 Pull

03: 000010000000000010000 X1XXXX1X TX LSR ROR DEC INC DEX NOP (4x4 bottom right)

04: 000001000000010010000 00XXXX1X TX ASL ROL

05: 010010011010010100000 01X11000 T0 CLI SEI

06: 101001100001010100000 0010X100 T1 BIT

07: 010001011010010100000 00X11000 T0 CLC SEC

08: 000000100110000000100 XXX101XX T3 OP zpg, X

09: 101010000000001000000 X11XXXX1 T1 ADC SBC

10: 011001100001010100000 0010X100 T0 BIT

11: 011001011001010100000 00101000 T0 PLP

12: 000110010101010100010 01000000 T4 RTI

13: 100110000000101000000 110XXXX1 T1 CMP

14: 100010101001100100000 11X01100 T1 CPY CPX

15: 100001011001010010000 00X0101X T1 ASL ROL

16: 100010000101100100000 11X00X00 T1 CPY CPX

K

KX: 000000011001010100000 0XX01000 TX Not actually line. Controls K09 to except push/pull opcodes --->

01: 010010011010100100000 11X11000 T0 CLD SED

02: 000001000000000000000 X0XXXXXX TX 00-3F 80-BF

03: 000000101001000000100 XXX011XX T3 RIGHT R EVEN

04: 000000100101000001000 XXX001XX T2 LEFT R EVEN

05: 000000010100001000001 XXXX00X1 T5 ALU indirect

06: 0000000010100?0000010 XXX11XXX T4 RIGHT ODD (? is actually 0, but strange.. 0XX11XXX T4 if supposed to be vias there)

07: 000000000000010000000 0XXXXXXX TX UPPER ALL

08: 001001011010100100000 10111000 TX CLV

09: 000000011000000...... XXXX10X0 TX All flags + DEY TAY INY INX - 0XX01000 <--- controlled by KX

Explanations:

A-K - line groups

01-09 - line number

000000001000000001000 - PLA bit assignment

X1XXXX1X TX - IR condition to fire line + T-step (T0-T5, TX mean "any")

+ short description which opcodes are affected by this line. "OP" mean any opcode.

PLA lines sorted by T-step:

Code: Select all

A04: 010100011001100100000 1X001000 T0 DEY INY

A05: 010101011010100100000 10011000 T0 TYA

A06: 010110000001100100000 1100XX00 T0 CPY INY

B04: 010101011001100010000 1000101X T0 TXA

B05: 010110011001100010000 1100101X T0 DEX

B06: 011010000001100100000 1110XX00 T0 CPX INX

B08: 010101011010100010000 1001101X T0 TXS

B09: 011001000000100010000 101XXX1X T0 LDX TAX TSX

B12: 011001011010100010000 1011101X T0 TSX

B14: 011001100000100100000 101XX100 T0 LDY

B15: 011001000001100100000 1010XX00 T0 LDY TAY

C01: 011001010101010100000 00100000 T0 JSR

C03: 010100011001010100000 0X001000 T0 Push

C09: 010110000000011000000 010XXXX1 T0 EOR

C12: 010101000000011000000 000XXXX1 T0 ORA

C14: 010000000000000000000 XXXXXXXX T0 T0 ANY

D13: 010010000001100100000 11X0XX00 T0 CPY CPX INY INX

D14: 010110000000101000000 110XXXX1 T0 CMP

D15: 011010000000101000000 111XXXX1 T0 SBC

D16: 011010000000001000000 X11XXXX1 T0 ADC SBC

E05: 010101011010100100000 10011000 T0 TYA

E09: 010101011001100010000 1000101X T0 TXA

E10: 011010011001010100000 01101000 T0 PLA

E11: 011001000000101000000 101XXXX1 T0 LDA

E12: 010000000000001000000 XXXXXXX1 T0 ALL ODD

E13: 011001011001100100000 10101000 T0 TAY

E14: 010000011001010010000 0XX0101X T0 ASL ROL LSR ROR

E15: 011001011001100010000 1010101X T0 TAX

E16: 011001100001010100000 0010X100 T0 BIT

E17: 011001000000011000000 001XXXX1 T0 AND

F01: 010000010110000100000 XXX10000 T0 <- Branch + BranchReady line

F03: 010010011001010010000 01X0101X T0 LSR ROR

F15: 010100010101010100000 0X000000 T0 BRK RTI

F16: 010010101001010100000 01X01100 T0 JMP

H05: 010010011010010100000 01X11000 T0 CLI SEI

H07: 010001011010010100000 00X11000 T0 CLC SEC

H10: 011001100001010100000 0010X100 T0 BIT

H11: 011001011001010100000 00101000 T0 PLP

K01: 010010011010100100000 11X11000 T0 CLD SED

E06: 100000000000011000000 0XXXXXX1 T1 UPPER ODD

E07: 101010000000001000000 X11XXXX1 T1 ADC SBC

E08: 100000011001010010000 0XX0101X T1 ASL ROL LSR ROR

H06: 101001100001010100000 0010X100 T1 BIT

H09: 101010000000001000000 X11XXXX1 T1 ADC SBC

H13: 100110000000101000000 110XXXX1 T1 CMP

H14: 100010101001100100000 11X01100 T1 CPY CPX

H15: 100001011001010010000 00X0101X T1 ASL ROL

H16: 100010000101100100000 11X00X00 T1 CPY CPX

A03: 000000011010001001000 XXX110X1 T2 OP abs, Y

B01: 000000100010000001000 XXX1X1XX T2 OP zpg, X/Y & OP abs, X/Y

B03: 000000010101001001000 XXX000X1 T2 OP ind, X

C08: 000000000000000001000 XXXXXXXX T2 T2 ANY

C11: 000000101001000001000 XXX011XX T2 RIGHT R ODD

C13: 000000000100000001000 XXXX0XXX T2 LEFT ALL

C15: 000000010001010101000 0XX0X000 T2 BRK JSR RTI RTS Push/pull

D05: 000000010110001001000 XXX100X1 T2 OP ind, Y

D12: 001001010101010101000 00100000 T2 JSR

E04: 000000010001010101000 0XX0X000 T2 BRK JSR RTI RTS Push/pull

F02: 000110011001010101000 01001000 T2 PHA

F05: 000101010101010101000 00000000 T2 BRK

F08: 000000010110000101000 XXX10000 T2 Branch

F09: 000000100100000001000 XXXX01XX T2 zero page

F10: 000000010100001001000 XXXX00X1 T2 ALU indirect

F11: 000000001000000001000 XXXX1XXX T2 RIGHT ALL

G10: 000101011001010101000 00001000 T2 PHP

G11: 000100011001010101000 0X001000 T2 Push

H01: 000110101001010101000 01001100 T2 JMP

K04: 000000100101000001000 XXX001XX T2 LEFT R EVEN

A02: 000000010110001000100 XXX100X1 T3 OP ind, Y

C05: 001000011001010100100 0X101000 T3 Pull

C16: 000000000001010100100 0XX0XX00 T3 BRK JSR RTI RTS Push/pull + BIT JMP

D03: 000000010101001000100 XXX000X1 T3 OP X, ind

D06: 000000001010000000100 XXX11XXX T3 RIGHT ODD

D10: 000000010110001000100 XXX100X1 T3 OP ind, Y

E01: 000010101001010100100 01X01100 T3 JMP

F06: 001001010101010100100 00100000 T3 JSR

F14: 000000000000000000100 XXXXXXXX T3 T3 ANY

F18: 000000001000000000100 XXXX1XXX T3 RIGHT ALL

G02: 000000001010000000100 XXX11XXX T3 RIGHT ODD

G03: 000000010110000100100 XXX10000 T3 Branch

H02: 001000011001010100100 0X101000 T3 Pull

H08: 000000100110000000100 XXX101XX T3 OP zpg, X

K03: 000000101001000000100 XXX011XX T3 RIGHT R EVEN

C04: 001010010101010100010 01100000 T4 RTS

D01: 000001010101010100010 00X00000 T4 BRK JSR

D02: 000110010101010100010 01000000 T4 RTI

D04: 000000010110001000010 XXX100X1 T4 OP ind, Y

D09: 000000010101001000010 XXX000X1 T4 OP X, ind

E18: 000000001010000000010 XXX11XXX T4 RIGHT ODD

F13: 000000000000000000010 XXXXXXXX T4 T4 ANY

G01: 000000010110001000010 XXX100X1 T4 OP ind, Y

G09: 000101010101010100010 00000000 T4 BRK

G12: 000010101001010100010 01X01100 T4 JMP

H12: 000110010101010100010 01000000 T4 RTI

K06: 0000000010100?0000010 XXX11XXX T4 RIGHT ODD (? is actually 0, but strange.. 0XX11XXX T4 if supposed to be vias there)

C02: 000101010101010100001 00000000 T5 BRK

C06: 000110010101010100001 01000000 T5 RTI

E03: 001001010101010100001 00100000 T5 JSR

E19: 000000010110001000001 XXX100X1 T5 OP ind, Y

F12: 001010010101010100001 01100000 T5 RTS

F17: 000000010101001000001 XXX000X1 T5 OP X, ind

G13: 000010010101010100001 01X00000 T5 RTI RTS

G14: 001001010101010100001 00100000 T5 JSR

K05: 000000010100001000001 XXXX00X1 T5 ALU indirect

A01: 000101100000100100000 100XX100 TX STY

B02: 000001000000100010000 10XXXX1X TX LDX STX A<->X S<->X

B07: 000101000000100010000 100XXX1X TX STX TXA TXS

B10: 000110011001100010000 1100101X TX DEX

B11: 001010011001100100000 11101000 TX INX

B13: 000100011001100100000 1X001000 TX DEY INY

C07: 001010000000010010000 011XXX1X TX ROR

C10: 000010101001010100000 01X01100 TX JMP

D07: 001000011001010100000 0X101000 TX Pull

D08: 001010000000100010000 111XXX1X TX INC NOP

D11: 000010010101010100000 01X00000 TX RTI RTS

D17: 001001000000010010000 001XXX1X TX ROL

E02: 000001000000010010000 00XXXX1X TX ASL ROL

F04: 000010000000010010000 01XXXX1X TX LSR ROR

F07: 000101000000101000000 100XXXX1 TX STA

G04: 000100010101010100000 0X000000 TX BRK RTI

G05: 001001010101010100000 00100000 TX JSR

G06: 000010101001010100000 01X01100 TX JMP

G07: 000000011001010100000 0XX01000 TX Push/pull

G08: 000101000000100000000 100XXXXX TX 80-9F

H03: 000010000000000010000 X1XXXX1X TX LSR ROR DEC INC DEX NOP (4x4 bottom right)

H04: 000001000000010010000 00XXXX1X TX ASL ROL

K02: 000001000000000000000 X0XXXXXX TX 00-3F 80-BF

K07: 000000000000010000000 0XXXXXXX TX UPPER ALL

K08: 001001011010100100000 10111000 TX CLV

K09: 000000011000000...... XXXX10X0 TX All flags + DEY TAY INY INX - 0XX01000 <--- controlled by KX

)

)