Page 3 of 4

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Wed Aug 21, 2024 6:31 pm

by hoglet

Fairly sure....

But please show me I am wrong -- I would absolutely love a dual ported BRAM!

OK, can you check in the Gowin device selection window that you have the "C" version of the part selected:

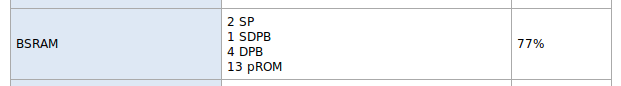

With this, in the Place & Route report I'm seeing this:

- Screenshot from 2024-08-21 19-20-05.png (5.58 KiB) Viewed 4105 times

There is a total of BSRAM 20 used out of 26 (77%)

SDBP is Semi Dual Port BSRAM (one write port and one read port)

DPB is true Dual Port BSRAM (two independant read/write ports)

This example is from AtomFPGA, where the true dual port RAM is the 8KB frame buffer, hence it using four BSRAMs (16Kbit each).

Now, it turns out in this case I ended up instantiating this using the DPB primitive, rather than inferring it:

https://github.com/hoglet67/AtomFpga/bl ... ram_8k.vhd

I don't remember why, but possibly because trying to infer it didn't work.

But anyway, I'm pretty convinced the device does have dual port BSRAMs, and it's the tools that are being problematic.

Dave

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Thu Aug 22, 2024 3:33 am

by enso1

I think yosys may not be up to date with the C devices and treat them as plain GW1NR9's. I haven't tried re-synthesising in the GOWIN IDE in a while, and I think i had bogus verilog early on, likely resulting in double BRAMS...

Thank you for clarifying.

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Thu Aug 22, 2024 6:10 pm

by enso1

Yes, confirmed that GOWIN IDE creates a dual-ported BRAM. I will double-check and open an issue at yosys as it appears that they are not aware of this GW1NR-9C capability.

P.S. My J1 synthesis report show fmax of 72MHz (vs 100MHz with Xilinx Spartan3), and 6% logic, 2% register, and 8 of 26 BRAMS. Not bad.

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Sat Aug 24, 2024 12:46 am

by dmsc

Hi!

Yes, confirmed that GOWIN IDE creates a dual-ported BRAM. I will double-check and open an issue at yosys as it appears that they are not aware of this GW1NR-9C capability.

P.S. My J1 synthesis report show fmax of 72MHz (vs 100MHz with Xilinx Spartan3), and 6% logic, 2% register, and 8 of 26 BRAMS. Not bad.

There is a footnote in the help:

https://github.com/YosysHQ/apicula?tab= ... 7301045f7a

Basically, you need to pass

Code: Select all

--device GW1NR-LV9QN88PC6/I5 --family GW1N-9C

to nextpnr, and use

for packing. There are examples that manually use dual-ported BRAM, seems it can also infer them.

Have Fun!

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Sat Aug 24, 2024 2:44 am

by enso1

I have a verilog J1 system that works when built in GOWIN IDE, but does not work (and shows double the BRAM count) in yosys. I don't like the IDE, but it is also much faster for this project, not to mention it works.

My makefile shows exactly the settings you mentioned, dmsc... Thanks for the link, I will do more digging.

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Tue Aug 27, 2024 2:57 pm

by enso1

https://tildegit.org/stack/Tangnano9K-j1

OK, my J1 system works at 50MHz built with GOWIN IDE. Build time is 17 seconds on my ancient I7-3620QM @2.2GHz and 4GB RAM.

Took a little twiddling to get the UART receiver to work, as J1 does everything in 1 cycle.

I'll be getting back to 6502 shortly, I hope. Much as I love stack machines, it can be painful.

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Mon Sep 02, 2024 3:08 pm

by enso1

Tugman CPU SOC

Since I am on an FPGA bender, I put together a curious 18-bit stack-machine CPU with complex instructions. Some may find the ISA quirkiness interesting, and the entire SOC with uart takes up 6% of the Nano 9K resources (and 9 BRAMS when configured for 8Kx18. Should really be 8 -- does the FPGA not support 18-bit BRAMS? I will find out.)

Apologies for being off-topic, and I will post on anycpu shortly.

https://tildegit.org/stack/Tugman

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Sat Sep 14, 2024 1:02 pm

by venomix

The Tang Nano-boards are really nice development platforms, especially for the price.

I have made a 65C02-based SoC for the Tang Nano 20K which boots CP/M-65 from the SD-card and has 80x30 text output on HDMI (at 640x480). It supports a USB keyboard with a carrier board, so it works quite well as a stand-alone computer (but text can also be input using the built in UART). It's available on github if anyone is interested:

https://github.com/venomix666/nano6502

I have only used the 20K myself, but I think it should be possible to adapt this design for running on the 9K without too many modifications. Perhaps the amount of RAM have to be reduced?

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Sat Sep 14, 2024 2:05 pm

by BigEd

(Welcome!)

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Sat Sep 14, 2024 2:25 pm

by venomix

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Sun Sep 15, 2024 1:11 pm

by enso1

venomix, that looks great!

I've been meaning to get the 20K. Should have done it earlier... Last time it was $30 on amazon prime, today it's only available as a kit with game controllers for $48 on prime. Otherwise it is shipped from China. Unsurprizingly, the US is experiencing a mini-hyper-inflation, with prices going up a little bit daily.

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Sun Sep 15, 2024 5:29 pm

by venomix

venomix, that looks great!

I've been meaning to get the 20K. Should have done it earlier... Last time it was $30 on amazon prime, today it's only available as a kit with game controllers for $48 on prime. Otherwise it is shipped from China. Unsurprizingly, the US is experiencing a mini-hyper-inflation, with prices going up a little bit daily.

Thanks!

Yeah, I got mine this spring and I ended up paying a bit more than I expected for it with shipping. The prices on AliExpress were almost suspiciously low, so I ended up getting it on Amazon even though the shipping to Sweden was rather pricy, and it was still shipped from China...

My main reason for getting the 20K (except for just more gates to play with) was the built in SDRAM, but I haven't managed to get the timing correct for it to play nicely with a 6502 core yet. It would be nice to have 8 Megs available and do bank switching, so it's still on my to-do list.

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Sun Sep 15, 2024 9:37 pm

by enso1

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Mon Sep 16, 2024 5:48 am

by venomix

enso1 - Yes, I've tried (so far unsuccessfully) to shoehorn that into my existing design but I have not gotten the timing with waitstates, refresh etc. correct yet.

The lack of simulation tools in the GoWin-toolchain does not help - I think I'll have to look at how they have made a Verilator model of the SDRAM in for instance NESTang and go from there in order to get it right.

Re: Tang Nano 9K - a (n almost) perfect 65(x)xx platform

Posted: Fri Sep 20, 2024 8:34 pm

by enso1

GoWin's IDE started crashing after I updated to Ubuntu 24.04 LTS!

I knew I shouldn't have upgraded, but couldn't help myself -- but what could possibly go wrong?

The solution was found after some googling around... There was a missing symbol in some fontconfig library that got updated. I downloaded libfontconfig.so.1.11.1 from someone's github repo, put it into my Gowin directory, and now start the IDE with:

Code: Select all

LD_PRELOAD=./libfontconfig.so.1.11.1 ./gw_ide

God help us all.