Page 3 of 5

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Tue Feb 25, 2025 10:30 pm

by BigDumbDinosaur

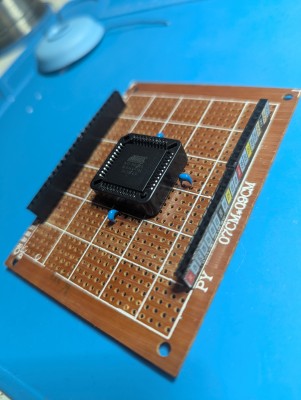

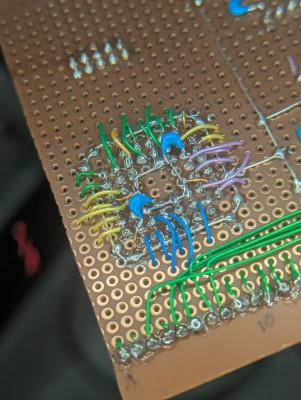

The "all those wires" project: just a breakout board with a PLCC socket and decoupling caps to test things. Still haven’t soldered all the wires, but enough for JTAG and power and clock and some outputs.

Be sure to use all VCC and ground connections on the PLD. Strange maladies can develop if one of these is not connected.

First experiment was to output the clock, as well as /2, /3 and /4 to four output pins. I did that in WinCUPL in a Windows VM, created a .svf file using ATMISP, and flashed that onto the chip using openocd on macOS. A mess of flying wires working up to 60MHz or so. Happy camper, despite the dolor de huevos.

If you can get through WinCUPL without a bunch of errors, the dolor isn’t too bad. The element of uncertainty is always in whether the in-circuit operation agrees with what the simulator is telling you.

P.S: I missed your answers because I didn’t get back to this page. Is it possible to get mail notifications when someone posts into a thread?

You can arrange to get E-mail notification by entering the user control panel and turning on that feature.

As for the Z80...

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Wed Feb 26, 2025 1:33 pm

by plasmo

You should convert “all those wires” project into pc boards. Somewhere on this forum are several PLCC-to-DIP boards for CPLD. I myself have something like 8 “all those wires” pcb designs and used them for various experiments.

CPLD is very powerful even with the modest 64-macrocell ATF1504. For an example, it can accommodate both a serial port and memory manager in one chip.

Bill

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Wed Feb 26, 2025 7:39 pm

by BigDumbDinosaur

CPLD is very powerful even with the modest 64-macrocell ATF1504. For an example, it can accommodate both a serial port and memory manager in one chip.

...and the ATF1508 is even more capable, with 128 MCs.

Somewhere in the back of my head has been brewing an idea on how to implement a blitter in the ATF1508 that would be capable of working in a 65C816 system with full 24-bit addressing. In such a role, the blitter would halt the 816 and become the bus master. The blitting operation would be able to complete a fetch-and-store cycle in two Ø2 clock cycles, disregarding any needed wait-states. With reliable 20 MHz operation being possible with the 816, the blitter would theoretically attain a speed of 10 MB/second.

A concern is the amount of registered logic that would be needed. A lot of I/O pins would be needed as well. Dunno if my idea is even possible in a CPLD of any size.

Another possibility would be to fashion an HMU (hardware management unit) in a 1508 (might be possible with the 1504). In a 65C816 system, the HMU would have overall glue logic “authority” and could create a user/supervisor environment to support protected operation, as well as police for verboten instructions, especially STP, whose effects cannot be prevented by any known means. It would also be cool for the HMU to be able to map the stack and direct page to any bank to relieve overcrowding in bank $00 and give each process a stack and direct page that cannot be accessed by any other process other than the kernel.

Lotsa wishful thinking!

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Thu Feb 27, 2025 9:31 pm

by martingi

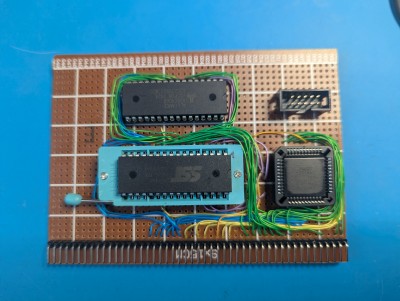

The pretty side:

- The pretty side

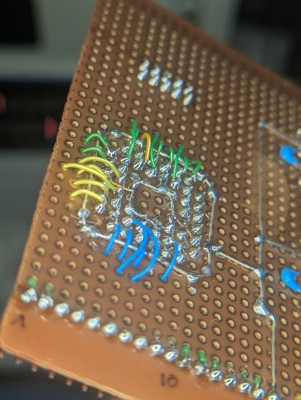

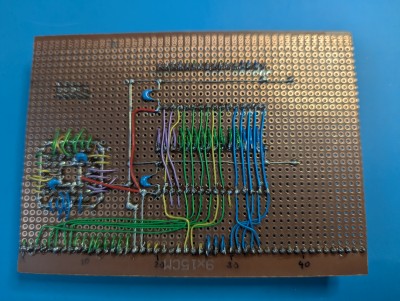

Wires:

I have indeed taken care to connect all Gnd and all Vcc pins. Each with a 100nF of its own. You may be able to see that I put a square wire around the PLCC for each of the rails. Don’t think I’ll do it like that next time, it really uses too much real estate like that.

PCBs… yeah, I’ll try that at some point I guess. I don’t feel like messing with chemicals myself, and waiting to get them in the mail also sounds annoying. And I

do enjoy some good old fashioned manual work.

Martin

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Thu Feb 27, 2025 9:49 pm

by martingi

Wishful thinking: I’m thinking about using a 1508 as a video controller. Maybe like the VGAtonic, with a separate video RAM, accessed by IO ports, MSX style.

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Thu Feb 27, 2025 9:56 pm

by plasmo

I think the wired side is the “pretty” side. I really like the power and ground rings, you should have no troubles with ground bounces. Brush it with isopropyl alcohol and the wired side will look like an art piece. I agree there are something therapeutic about soldering carefully one wire at a time.

Bill

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Thu Feb 27, 2025 10:02 pm

by plasmo

Wishful thinking: I’m thinking about using a 1508 as a video controller. Maybe like the VGAtonic, with a separate video RAM, accessed by IO ports, MSX style.

Not wishful thinking at all. With help of a dual port RAM, you can do video text display in VGA even with 1504.

Bill

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Tue Apr 22, 2025 12:56 pm

by martingi

I thought I might as well post an update on my CPLD adventures.

The first project was a programmable clock divider to control the baud rate of a SIO/2 dual serial IO. It just barely fits on a 1502 and uses the upper and lower nibbles of one IO port to select the two divider ratios. If I ever find I need more dividers (75 baud anyone?) then I can drop in a 1504 without changing the wiring. Nice!

I posted a picture of my "prototyping board" a few weeks ago with the two rings around the PLCC for ground and Vcc. I found this took up too much real estate on the perfboard, so for the SIO/2 board, I had two solder points in the centre leading to the 2x4 power supply pins. The decoupling caps were still on the outside. The result works but it’s pretty chaotic.

Yesterday I finished my take on the paged 512k RAM/512k Flash module. The page registers and logic around just barely

don’t fit on a 1502, so a 1504 it was.

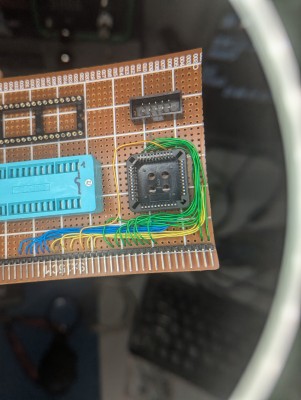

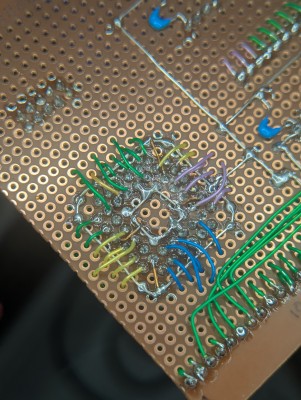

I’m a lot more happy with the wiring arrangement, let me share some pictures…

- Power ring in the centre, ground ring on the outside. Enamelled copper wire to the supply pins.

- All other wires PTFE coated and routed on the top side.

- Had to use a really fine soldering tip towards the end. The wires from the outer holes go to the inner pins, all of them arching over the ground ring.

- Finally, two 100nF decoupling caps between the Vcc ring in the centre and the two ground pins on the inner ring. I read in an Atmel app note that 220nF total are recommended, and that his is probably an overkill for most purposes. And they’re certainly hard to get closer to the pins than this!

- End result, top side.

- End result, wiring side.

Oh, there’s a 10 pin header for JTAG reprogramming of the CPLD. In the end I decided that I’d rather have fewer wires around and remove the chip from the socket if I ever need to change its programming.

Wouldn’t have gotten this far without the advice on this forum

Martin

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Tue Apr 22, 2025 4:52 pm

by enso1

Beautiful!

In fact, I would probably try to avoid bending all the green and blue wires at right angles, and just run the buses with shortest path.

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Tue Apr 22, 2025 9:50 pm

by plasmo

That's a good looking prototype board. The power and ground ring are best way of dealing with the relatively fast CPLD.

By the look of it, you are emulating RC2014's 512K RAM/ROM board. I do believe it is possible to fit the design in an ATF1502, but you need to have freedom in pin assignments for the fitter to pick the right fit.

Bill

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Wed Apr 23, 2025 8:15 am

by martingi

Glad you like it

In fact, I would probably try to avoid bending all the green and blue wires at right angles, and just run the buses with shortest path.

But… it’s a computer! They’re

meant to be all angular, no?

Kidding aside, there were several reasons for not using shortest paths here. 1. approaching pins with a minimum risk of shorting to neighbouring pins. In particular since many pins on the DIP sockets and the bus have two leads, above each other or opposite. 2. I want to avoid running wires over holes that I might need to thread another wire through later on. The latter issue can often be avoided by working in the right order, but that requires more premeditation.

But point taken, I wouldn’t have needed to make actual angles there.

That's a good looking prototype board. The power and ground ring are best way of dealing with the relatively fast CPLD.

The transients are terrible. You can see each edge of the clock signal on every output, even with twice as much decoupling

By the look of it, you are emulating RC2014's 512K RAM/ROM board.

You’re right. Spencer writes about his board "The circuit is largely a reproduction of the ROM/RAM part of Sergey Kiselevs Zeta 2, with some modifications inspired by Dr Scott Bakers ROM/RAM Module." Putting the MMU logic on a CPLD is not new either, I was inspired by

https://github.com/skiselev/Z80-512K/ but redid the coding in Verilog instead of VHDL. The main reason for using a CPLD (apart from having an excuse to learn about programmable logic) is to avoid the otherwise commonly used 74HCT670 register file ICs which you would need two of, at a cost about 11USD a piece

Little twist: the official pinout of the flash and the RAM are a bit different for the most significant couple of address bits. That would have led to some awkward wire crossings. I stuck to the correct pinout of the flash so I would be reading what my external programmer wrote. But the address bits of the RAM are permuted to simplify the wiring. The only wire that does not run parallel is the write enable.

I do believe it is possible to fit the design in an ATF1502, but you need to have freedom in pin assignments for the fitter to pick the right fit.

Yes, it fits exactly, using 32 of 32 macrocells. I went for the more wasteful 1504 out of pure laziness, to simplify the point to point wiring and continuity testing, and reduce the number of differently coloured wire coils flying around on the work bench simultaneously.

Martin

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Wed Apr 23, 2025 12:27 pm

by barnacle

Thanks, I've been trying to remember the part number for that register file. Mouser Europe have some in soic-16 (which suits me) for €1.50, or in dip16 for €2. Sadly, the part is way beyond not recommended for new designs; it's obsolete so while it's available, it won't be for long. (Digikey are plus the Rochester premium and probably minimum order as well).

I'm sure I've come across a 16x16 equivalent, though, once upon a time. Now that would be handy...

Neil

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Wed Apr 23, 2025 2:16 pm

by plasmo

Spencer’s 512K RAM/ROM board is quite expensive, driven by high cost of 74hct670. ATF1502 is around $3, so it can significantly lower the cost had he chosen to go with CPLD, although Spencer may not consider CPLD retro enough.

512K RAM/ROM is mainly used by RomWBW, but only as 32KB banks. The CPLD design simplifies tremendously for 32KB banks which can free it for other functions resulting in tighter integration of processor, memory and IO.

Bill

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Wed Apr 23, 2025 4:47 pm

by Dr Jefyll

Sadly, the part is way beyond not recommended for new designs

Are you referring to the '670 4x4 register file? Happily -- and somewhat surprisingly -- the HC version of this chip is still listed as

active and in stock at Digikey.

<sigh> And an utterly charming little chip it is!

Years ago I

posted about it. Too bad the AC version is no longer available...

-- Jeff

Re: ATF15xx Verilog/VHDL using Quartus 13.0 SP1

Posted: Wed Apr 23, 2025 5:00 pm

by enso1

I always try to match the 'official' address and data pinning designations (for debugging and the archeologists), but it really does not matter... Sometimes you can make the layout work much better by picking whatever works.