Page 3 of 4

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 12:14 pm

by ttlworks

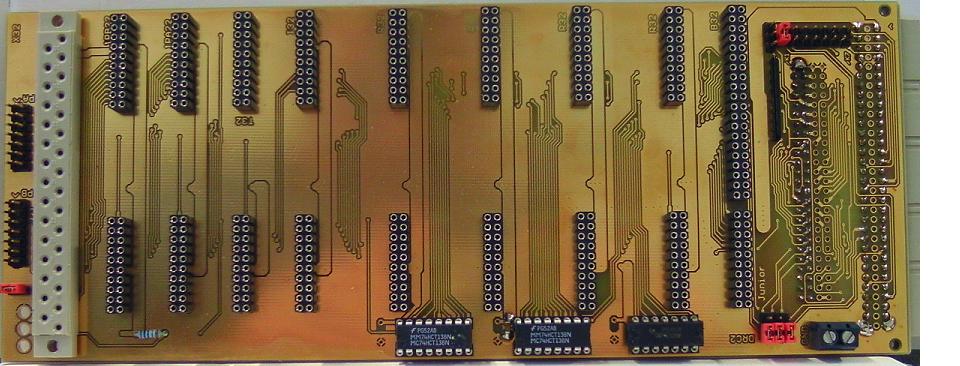

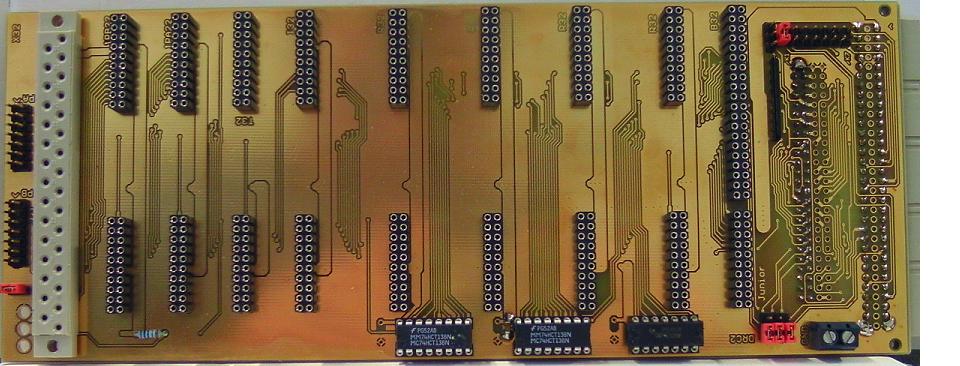

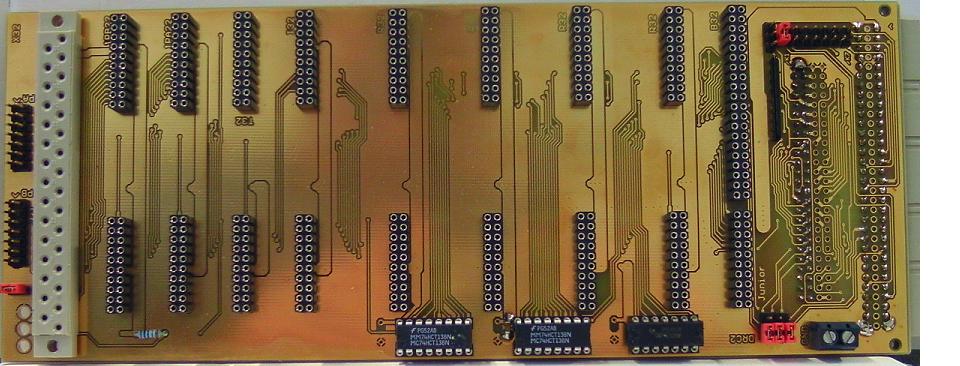

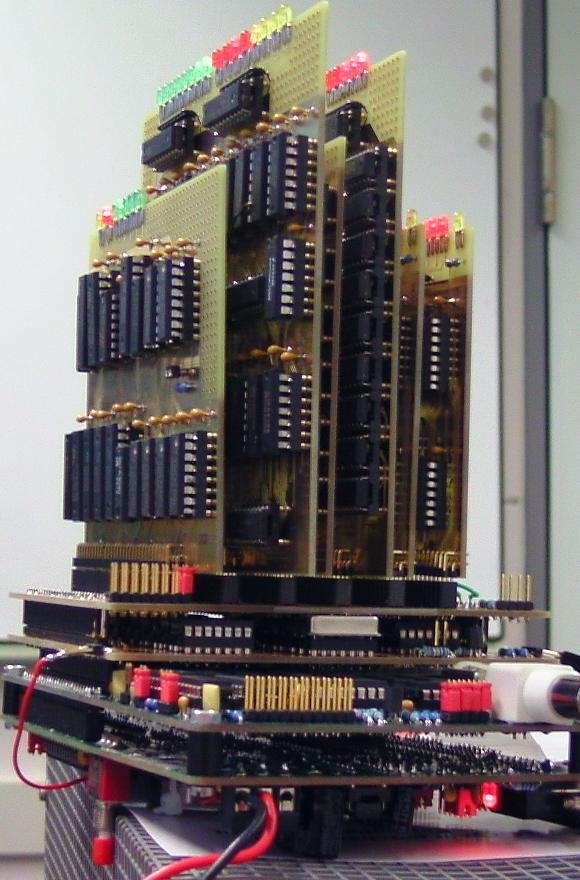

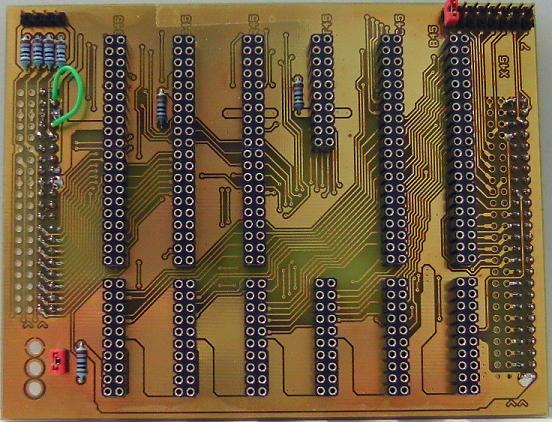

X32 backplane.

Something went wrong when making the Eagle device for that 31 pin connector at the left side of the PCB:

connector pinout seems to be reversed.

Also, one should be _very_ careful about that 64 pin Junior Computer bus connector,

because the EPROM inside the Junior Computer needs a +12V and a -5V supply voltage.

Making a mistake here could turn out to be quite expensive.

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 12:17 pm

by ttlworks

1PA22 and 1PB22 I\O ports already went described somewhere up in this thread.

;---

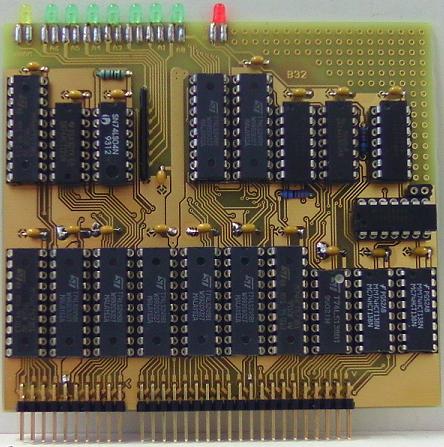

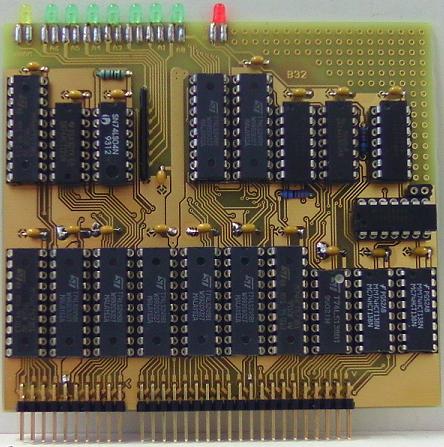

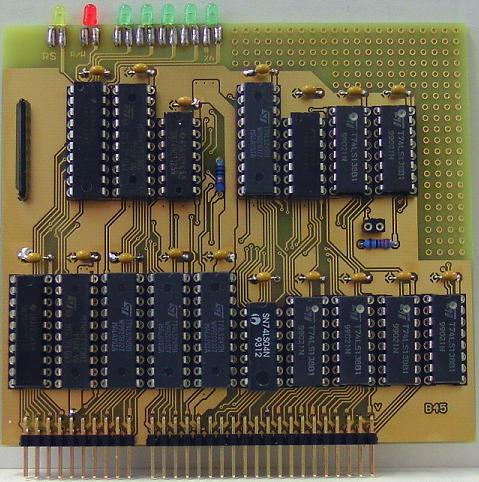

B32 bus interface.

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 12:24 pm

by ttlworks

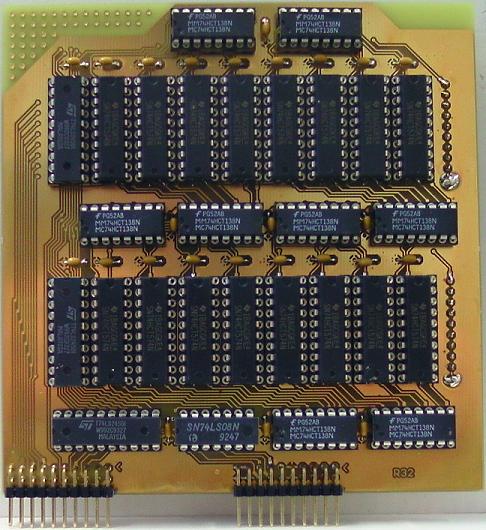

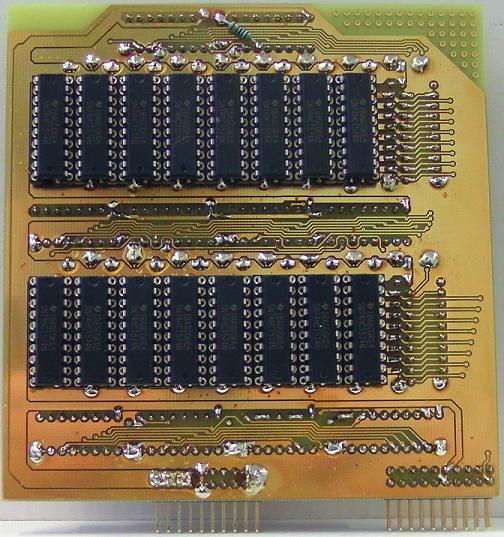

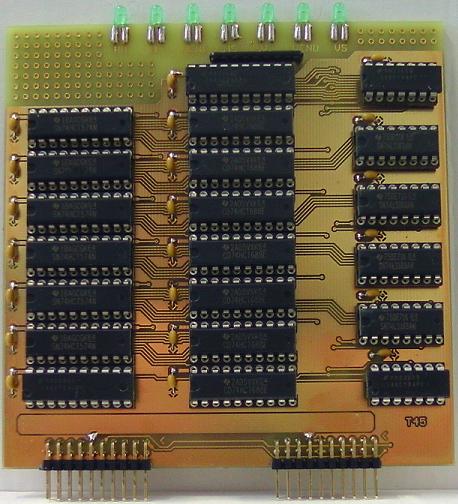

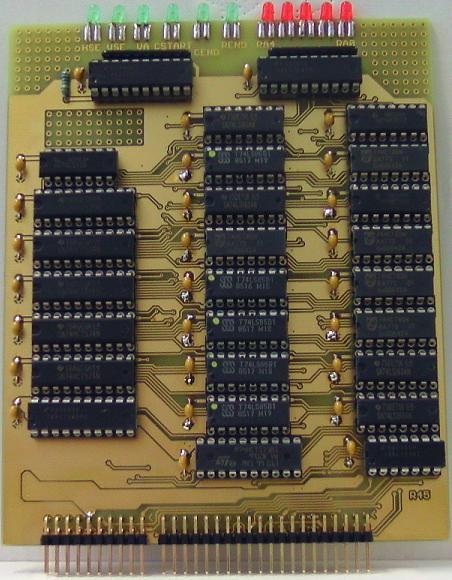

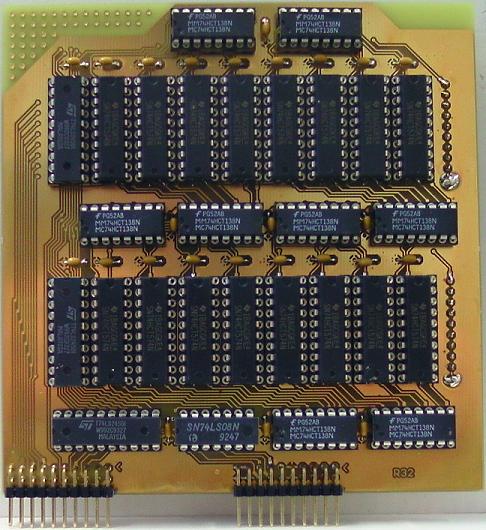

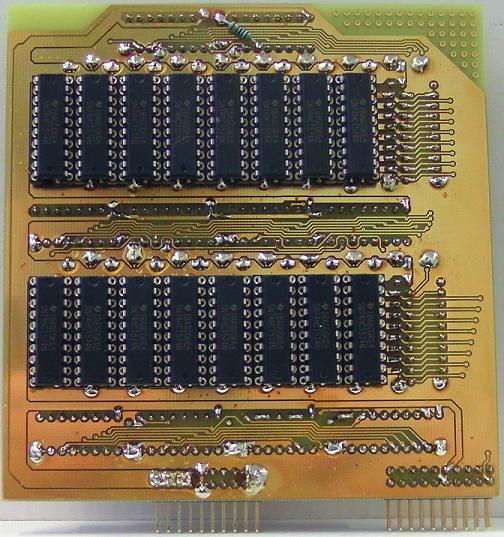

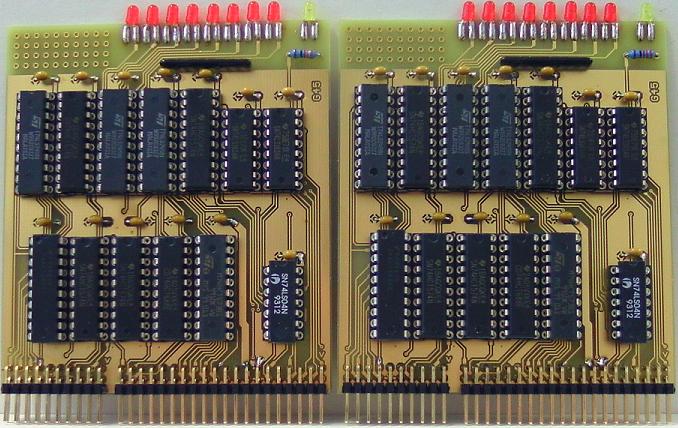

R32 module, 32 Bytes of TTL SRAM, 4 modules required (only one was built).

Top and bottom of _one_ module:

And yes, 44 chips on one PCB.

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 12:28 pm

by ttlworks

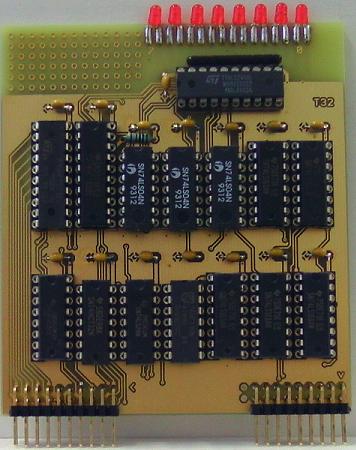

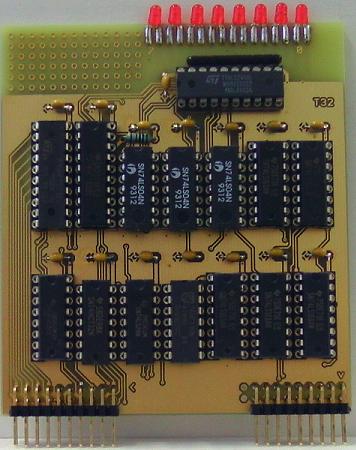

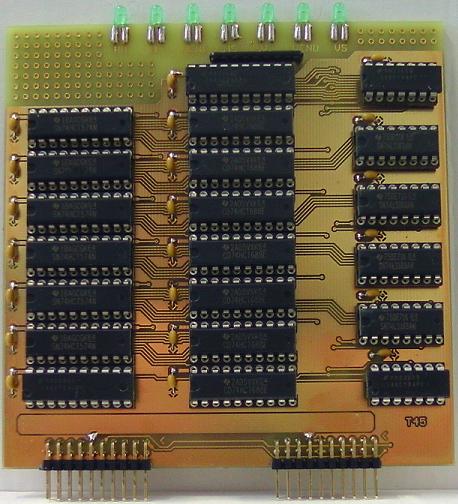

T32, 8 Bit timer with prescaler.

Bug warning: the prescaler is supposed to be set to :1 on timer overflow,

and IIRC this feature somehow is missing in T32.

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 12:31 pm

by ttlworks

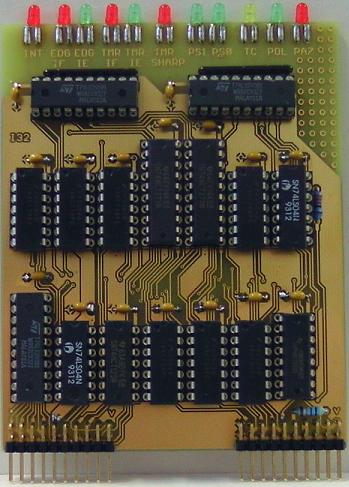

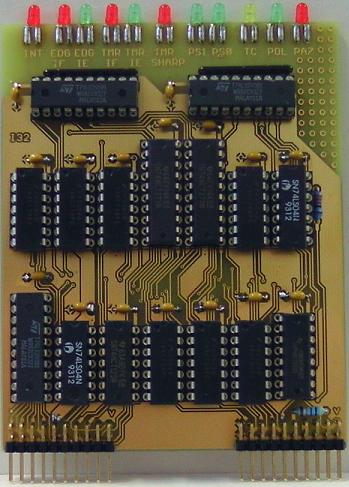

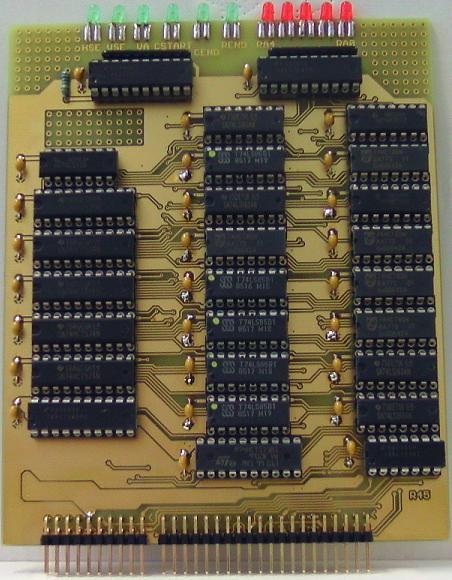

Last part: I32, timer control and interrupt module.

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 12:35 pm

by ttlworks

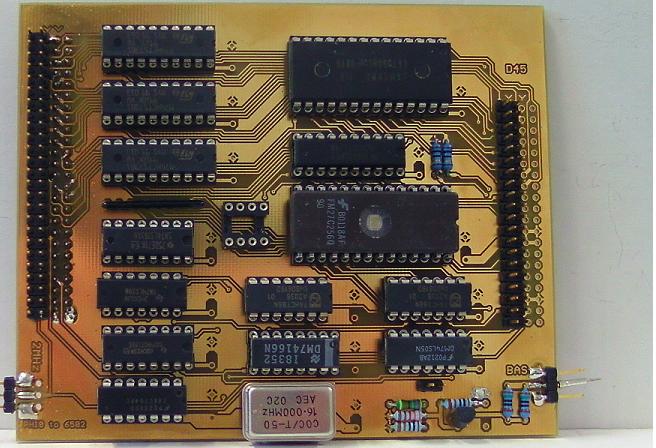

...And an obscure paper design for a 20MHz TTL 6532, which most likely won't work.

Don't ask me why the circuitry looks the way it looks, I fail to remember these details.

This design uses a real SRAM instead of TTL RAM.

So far, so good.

6545 will be next.

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 12:52 pm

by BigEd

Thanks for sharing all these ideas and details!

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 1:47 pm

by ttlworks

Thanks, Ed.

What now follows is the "Klendathu edition": plenty of bugs at a considerable size,

because it had been a work in progress... and it wasn't properly "unmounted".

Means the register settings for generating a picture might be a little bit different from the 6545.

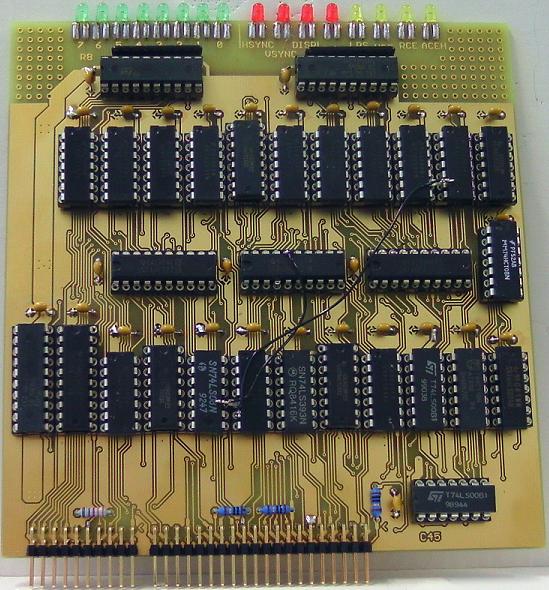

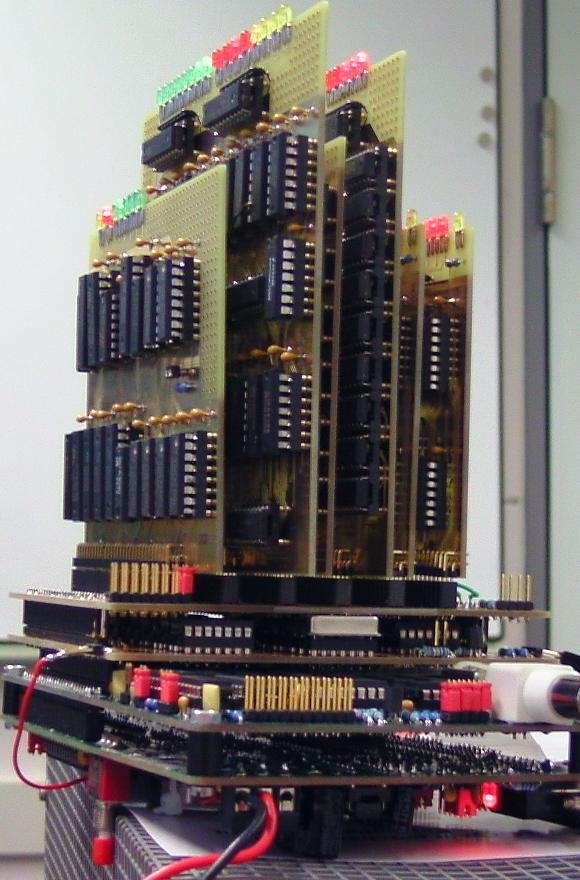

X45, experimental 6545 TTL implementation.

16 Bit video address output (instead of 14 Bit), transparent latches in the address output lines

for compensation of bus hold timing issues, and IIRC it was a three-state output.

Interlaced mode with some conceptual bugs, also sort of a horizontal scrolling mode where

one line of characters is 256 Bytes.

D45 demonstrator PCB (for generating a video signal) was plugged between the computer and the

X45 backplane.

Plugged into the X45 backplane, we have:

1* B45, bus interface

1* C45, the control module

1* T45, horizontal\vertical timing module

1* R45, raster timing module

2* G45, two video address generator modules

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 1:52 pm

by ttlworks

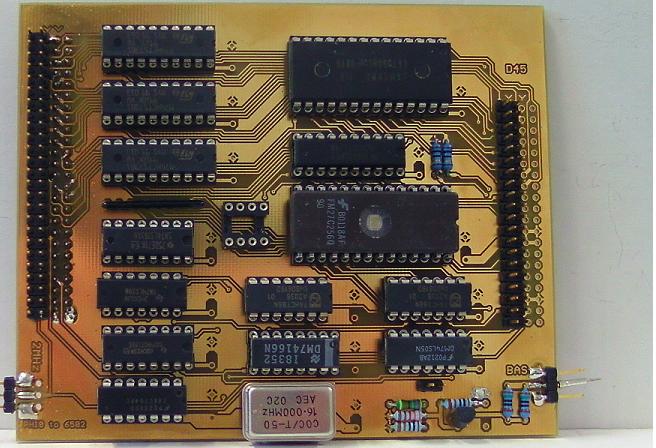

Let's start with D45, the demonstrator PCB containing the display RAM, the character ROM, the shift register etc.

80 characters per line (6502 has to run with a 2MHz clock generated by D45), monochrome analog video signal.

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 1:54 pm

by ttlworks

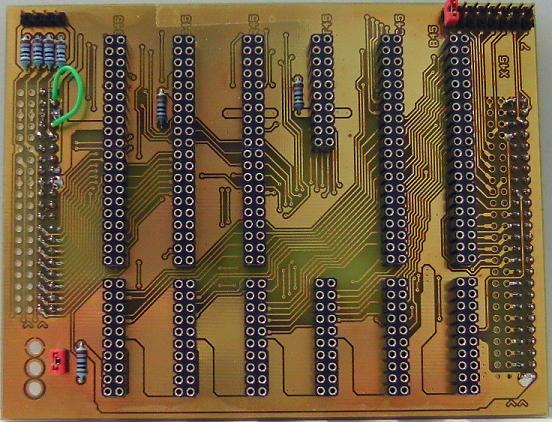

The X45 backplane.

IIRC the little green wire was added for testing the light pen registers.

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 1:57 pm

by ttlworks

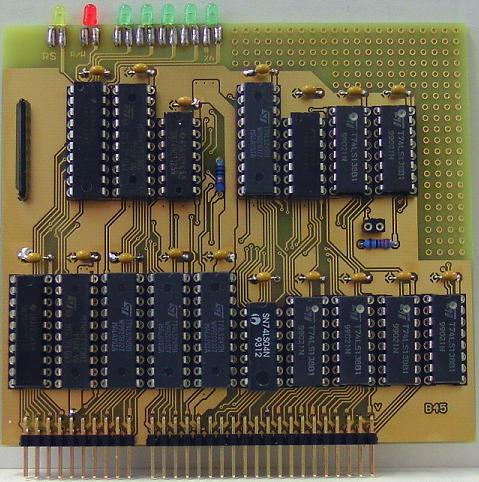

B45, the bus interface to the 6502.

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 1:59 pm

by ttlworks

T45, horizontal\vertical timing module

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 2:02 pm

by ttlworks

R45, raster timing module

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 2:04 pm

by ttlworks

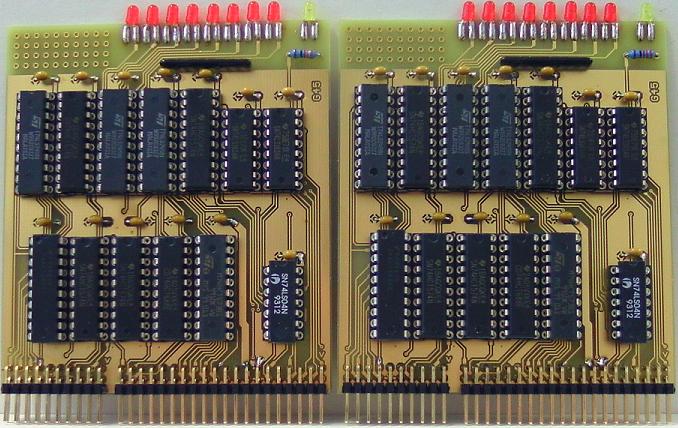

G45, video address generator module, two identical modules required

Re: Experimental TTL implementation of the 6522

Posted: Sat Apr 06, 2019 2:11 pm

by ttlworks

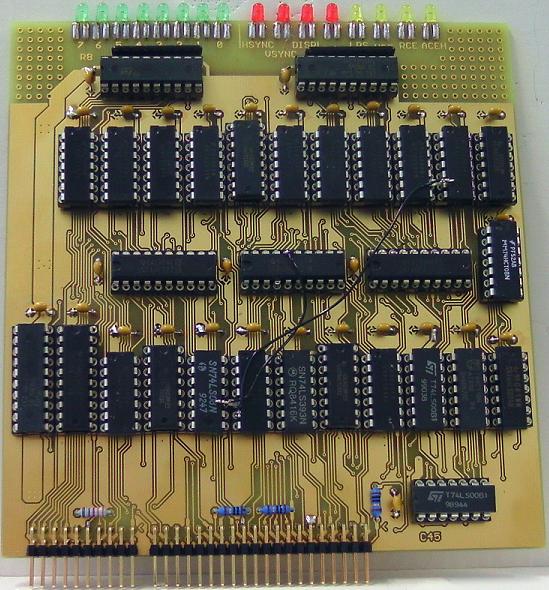

Now the last part:

C45, control module.

Unfinished work, has conceptual bugs, and you better design the whole thing again from scratch. I really mean it.

IIRC the intention was being able to run the video address generation circuitry at a higher frequency than the 6502 CPU,

with the idea in my backhead of porting the design to a CPLD someday, so I had decided to go with synchronous logic.

But this had bloated and complicated the logic design a lot, maybe it would better you go for another concept

like making creative use of RS flipflops at some places in the circuitry if you are trying to build something like that.