Page 14 of 37

Re: POC Version 2

Posted: Sat Aug 16, 2014 4:53 am

by BigDumbDinosaur

That seems to be the most sparsely populated area of your board, so it looks like you should be able to do it, at the expense of some bill-boarding and jumper-map real estate.

Mind-reader!

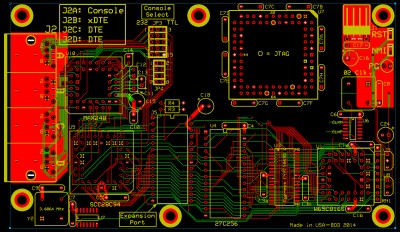

- Current POC V2 PCB layout with an Atmel ATF1504AS CPLD.

Above is the current layout.

- Partial POC V2 PCB layout using an Atmel ATF1508AS CPLD.

The above is the start of a new layout using the 1508AS. As you can see, the PLCC-84 package is like an elephant sitting on a toad in this design. Plus there are all those bypass caps. The top rows of pins won't be usable, because I can't get the connections out. Despite that, I'll actually have some usable spares, since only 36 I/O pins are used in the circuit and I figure 40-42 will be accessible.

The EWS jumper block you see on the small CPLD layout can be relocated, as it is a static DC circuit and thus isn't position-sensitive. Some silk screen artwork will have to go, which is no big deal. Otherwise, I think I can get everything hooked up. There's always a way...

Re: POC Version 2

Posted: Sat Aug 16, 2014 9:13 am

by BigEd

It's enormous!

Re: POC Version 2

Posted: Sat Aug 16, 2014 3:55 pm

by BigDumbDinosaur

Seems like it, eh, especially when compared to the PLCC-44 device it replaces. Hence my "elephant sitting on a toad" wisecrack. The 53CF94 ASIC on the SCSI host adapter is also PLCC-84 and accounts for about one half of the total PCB real estate. No wonder QFPs and such were developed.

BTW, the object representing the PLCC-84 package includes the socket. I could slightly shrink things by soldering the CPLD directly to the board, but that would mean I'd have to have a JTAG port to program it. I can live with the socket.

Re: POC Version 2

Posted: Mon Aug 18, 2014 11:33 am

by Aslak3

BDD,

Have you considered radically reworking the board, or are you keen to reuse as much of the existing layout as possible?

The reason I ask is I had a similar "change" in my 6809 project (going from discrete 74 glue to a PLCC84 CPLD) and in the end I concluded that the only thing to do was to scrap the entirety of the existing layout and start again.

In your case, how about a more square board with the PLC84 in the centre? I know you have some quite "tight" square area requirements for board costs, but it might be worth looking at? It would be a shame to not have the full set of CPLD pins available.

Also, do you have some documentation describing what your CPLD will do? I'm assuming from the number of pins and function blocks that it is a bit more then just glue logic?

EDIT: fixed PLCC pin count.

Re: POC Version 2

Posted: Mon Aug 18, 2014 3:14 pm

by barrym95838

Some of the description is too advanced for me to understand completely, but it looks like this is BDD's device:

http://www.atmel.com/Images/doc0784.pdf

Mike

Re: POC Version 2

Posted: Mon Aug 18, 2014 5:23 pm

by Aslak3

I'm curious to learn what BDD will be programming the device to do. The XC95108 in my micro (a comparable part I believe) serves as a couple of simple peripherals (sounder driver, bank switching latch, IDE high byte latch) as well as the traditional glue functions (address decoding, interrupt routing, etc). I'm interested to find out what BDDs PLD will be handling. Eg those unuseable pins could be useful for all kinds of things.

Re: POC Version 2

Posted: Mon Aug 18, 2014 9:11 pm

by BigDumbDinosaur

That's the animal. It's available in PLCC-84, TQFP-100, PQFP-100 and PQFP-160 packages. I'm not able to solder the PGFP and TQFP packages, so I stuck with the PLCC-84 for now.

Have you considered radically reworking the board...?

No. The west side of the board has to remain unchanged from POC V1 so the SCSI host adapter (HBA) will fit. Otherwise, I will be faced with redesigning the HBA as well and spending extra money to get new PCBs made. The HBA works very well, so I really don't want to tinker with it for now.

I'm curious to learn what BDD will be programming the device to do. The XC95108 in my micro (a comparable part I believe) serves as a couple of simple peripherals (sounder driver, bank switching latch, IDE high byte latch) as well as the traditional glue functions (address decoding, interrupt routing, etc). I'm interested to find out what BDDs PLD will be handling. Eg those unuseable pins could be useful for all kinds of things.

The ATF1504AS (the PLCC-44 device) was supposed to handle memory mapping, bank address capture, SCSI DMA logic, wait-state generation,

/RD and

/WD generation, and I/O device selection. The 1504 has 64 macro cells, so I also was planning on synthesizing a simple "hardware management unit" (HMU) to allow selective mapping out of low and high ROM, as well as write bleed-through when a ROM address is written. This would have allowed me to shadow the ROM in RAM and avoid wait-stating ROM accesses at high clock rates.

Since it appears I will have to make the switch to the 1508AS, the door will be opened to a more elaborate design. Here's the memory map:

- POC V2 Memory Map

Ultimately, the HMU would be as follows:

- Hardware Management Unit Assignments

The extra I/O pins on the 1508 can be connected to

ABORTB,

IRQB,

NIMB and

VPB. With 128 macrocells, I'll have adequate resources to implement some memory protection, user and supervisor modes, bank $00 remapping and other features that I've hashed out in older posts.

Re: POC Version 2

Posted: Wed Aug 20, 2014 6:47 pm

by cbscpe

Hi BDD,

what tools (hardware and software) do you use to program the ATF1508.. PLD and is there a USB programmer for this baby?

Regards

Peter

Re: POC Version 2

Posted: Wed Aug 20, 2014 7:49 pm

by BigDumbDinosaur

what tools (hardware and software) do you use to program the ATF1508.. PLD and is there a USB programmer for this baby?

I use Atmel's WinCUPL and ISP software and their ATF15XX-DK3 programming/test rig to program the device. I believe Atmel has a USB JTAG gadget but am not sure. The ATF15XX-DK3 runs from a parallel port.

Re: POC Version 2

Posted: Thu Aug 21, 2014 8:27 am

by BitWise

Re: POC Version 2

Posted: Thu Aug 21, 2014 3:06 pm

by BigDumbDinosaur

I have everything in the kit excepting the ATDH1150USB USB-to-JTAG cable. The ATDH1150USB must be a relatively new product, as I didn't see any such thing available from Atmel two years ago when I obtained the ATDH1150USB kit. We now have the answer to Peter's question about a USB adapter.

POC Version 2 w/Big CPLD

Posted: Sat Aug 23, 2014 4:57 am

by BigDumbDinosaur

It took some doing, but I concocted a PCB layout for POC V2 that uses the PLCC-84 version of Atmel's ATF1508AS CPLD. It's fairly tight—definitely a case of stuffing a bushel of apples into a picnic basket.

I even managed to preserve some of the silkscreen artwork. I'll probably fiddle with it some more to see how tight I can get it. Also, I spotted some minor boo-boos after I created the GIF you see below.

- POC V2 w/Atmel ATF1508AS CPLD in PLCC-84 Package

Re: POC Version 2 w/Big CPLD

Posted: Sat Aug 23, 2014 10:35 am

by Aslak3

BDD,

It took some doing, but I concocted a PCB layout for POC V2 that uses the PLCC-84 version of Atmel's ATF1508AS CPLD. It's fairly tight—definitely a case of stuffing a bushel of apples into a picnic basket.

I even managed to preserve some of the silkscreen artwork. I'll probably fiddle with it some more to see how tight I can get it. Also, I spotted some minor boo-boos after I created the GIF you see below.

The entire board is a piece of art in itself.

What's your smallest track width and via size? My boards - comparable to yours in complexity - are 2 layer, use 10 mil tracks, 10 mil via tracks with a 20 mil hole and pass a 10 mil DRC just because I like to be extra safe. But it's a hell of a lot of work hand routing this stuff. I really need to start on 4 layer boards, with smaller features.

Manual routing PCBs is a strange activity. Sometimes frustrating yet immensely satisfying.

Re: POC Version 2 w/Big CPLD

Posted: Sat Aug 23, 2014 6:15 pm

by BigDumbDinosaur

The entire board is a piece of art in itself.

Thanks! However, don't expect to see it in the Louvre anytime soon.

What's your smallest track width and via size?

6 mil traces and 26 mil via with 8 mil holes. The board is four-layer, with internal ground and power planes.

I really need to start on 4 layer boards, with smaller features.

Four-layer boards definitely simplify the layout, as well as allow you to pack things together more closely. You also get better noise immunity and avoid ground bounce problems. It's worth the slight extra cost over a comparable two-layer board.

Manual routing PCBs is a strange activity. Sometimes frustrating yet immensely satisfying.

I liken PCB layout to playing chess with an inscrutable master.

BTW, I said I would try to tighten things up a little more with the new PCB layout. I was able to crowd the CPLD a little closer to the rest of the parts, achieving a slight reduction in trace length. I'll let it sit for a day or two and then review it again to see if there's anything else that can be shrunk.

- POC V2 w/Atmel ATF1508AS CPLD in PLCC-84 Package

——————————————————————————————————————————————

Edit: Accidentally uploaded the wrong image. The above is the correct one.

Re: POC Version 2 w/Big CPLD

Posted: Mon Sep 29, 2014 5:58 pm

by BigDumbDinosaur

I'll let it sit for a day or two and then review it again to see if there's anything else that can be shrunk.

Well, it sat for more than a day or two as other matters used up my time (see first picture), but I did review the PCB layout and couldn't find anything else to do to refine it. I believe I have a "production" version (see second picture).

- EMD F7 Diesel-Electric Locomotive

- POC V2 "Production" PCB