Posted: Fri Aug 27, 2010 5:15 am

(cross-thread from the "oscilloscope as a Logic Analyzer" topic:)

SYNC went dead after the SRAM was enabled? If there's no activity on SYNC then the cpu simply isn't running. It may have somehow executed a WAI or STP (Wait or Stop -- new WDC instructions). That wasn't your intention but if the system has crashed for some reason, it'll end up executing garbage (data, inappropriate code or the contents of uninitialized memory). Running amok that way it may have swallowed a WAI or STP op-code, and that would squelch the signal on SYNC.

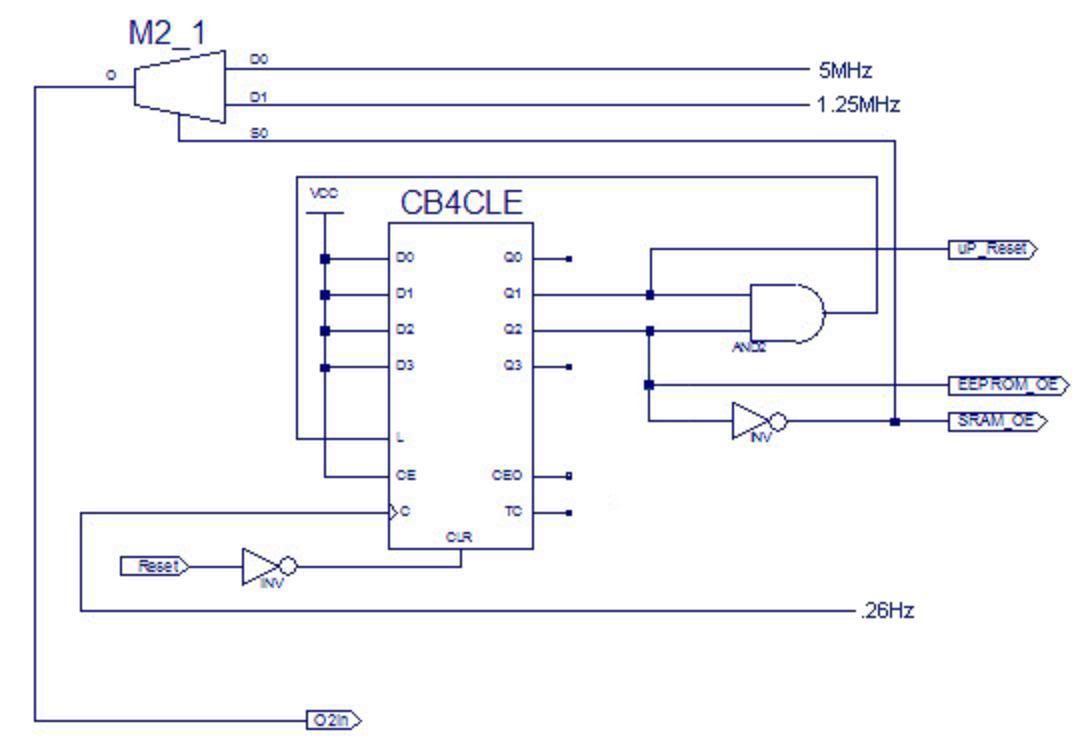

Another possibility is that the cpu has lost its clock signal or some other basic requirement. Hence no SYNC. Is the Phase2 signal OK? Isn't your clock mux associated with the same reset logic that enables the SRAM? Smells like a clue to me... Trouble with the mux? I could be wrong...

Probably a good idea. There's no need to go beyond 1.25 MHz at present. And the EEPROM to SRAM copy is kinduva handful -- lots that could go wrong.

Is the schematic on page 11 of this thread still current with respect to the Reset logic and clock mux?

-- Jeff

ElEctric_EyE wrote:

I tried to jump ahead and do the EEPROM to SRAM copy @1.25MHz and run the system @5MHz. SYNC went dead after the SRAM was enabled and the CPU reset meaning either: 1) I am not giving the software enough time to copy $C000-$FFFF from EEPROM to SRAM, (unlikely) or 2) There is a problem with the bank switching hardware controlling addresses to the SRAM. Since I am using zero page for indirect indexed to copy 16K, the bank hardware is constantly flipping from upper 16K, where the copy program resides, to the lower 16K where zero page is...

Before I do tackle this problem however, I think I should focus back onto initializing the display, which is just LDA/STA, running from the EEPROM @1.25MHz.

Garth I used to use a '374 as a test port as well for an initial test to make sure everything was wired correctly etc. on my first iteration of the PWA. I actually did think of trying to put it inside the FPGA, but never got around to it... Testing SYNC seems to be an even more "bare bones" approach to initial startup, because you're testing right at the CPU itself.

Before I do tackle this problem however, I think I should focus back onto initializing the display, which is just LDA/STA, running from the EEPROM @1.25MHz.

Garth I used to use a '374 as a test port as well for an initial test to make sure everything was wired correctly etc. on my first iteration of the PWA. I actually did think of trying to put it inside the FPGA, but never got around to it... Testing SYNC seems to be an even more "bare bones" approach to initial startup, because you're testing right at the CPU itself.

SYNC went dead after the SRAM was enabled? If there's no activity on SYNC then the cpu simply isn't running. It may have somehow executed a WAI or STP (Wait or Stop -- new WDC instructions). That wasn't your intention but if the system has crashed for some reason, it'll end up executing garbage (data, inappropriate code or the contents of uninitialized memory). Running amok that way it may have swallowed a WAI or STP op-code, and that would squelch the signal on SYNC.

Another possibility is that the cpu has lost its clock signal or some other basic requirement. Hence no SYNC. Is the Phase2 signal OK? Isn't your clock mux associated with the same reset logic that enables the SRAM? Smells like a clue to me... Trouble with the mux? I could be wrong...

Quote:

I think I should focus back onto initializing the display, which is just LDA/STA, running from the EEPROM @1.25MHz.

Is the schematic on page 11 of this thread still current with respect to the Reset logic and clock mux?

-- Jeff