Thanks for the kind words and the appreciation.

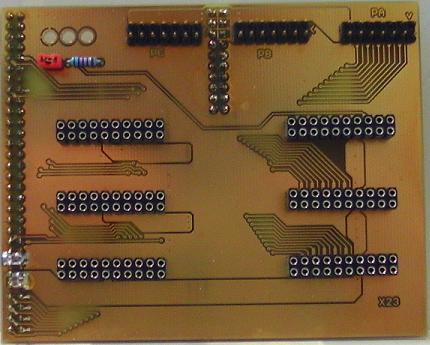

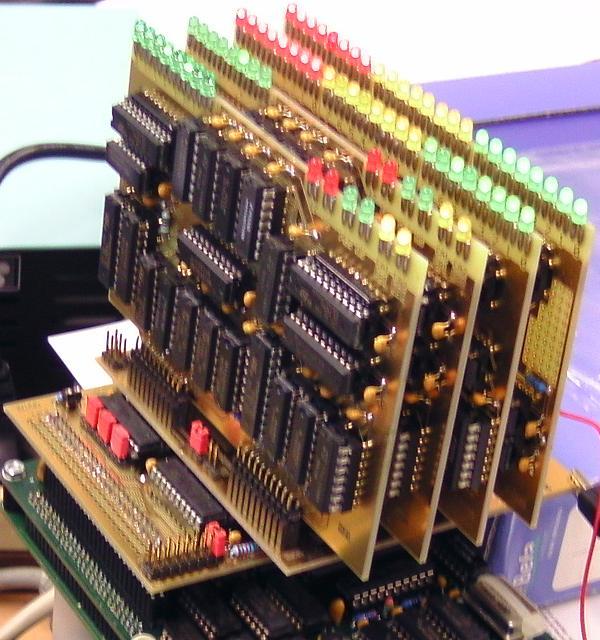

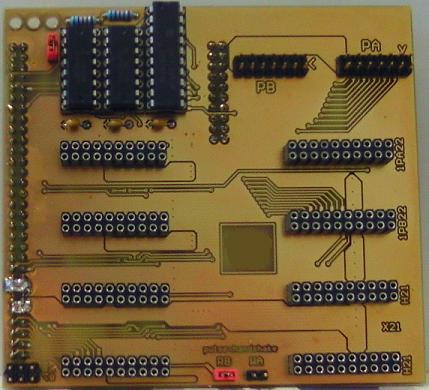

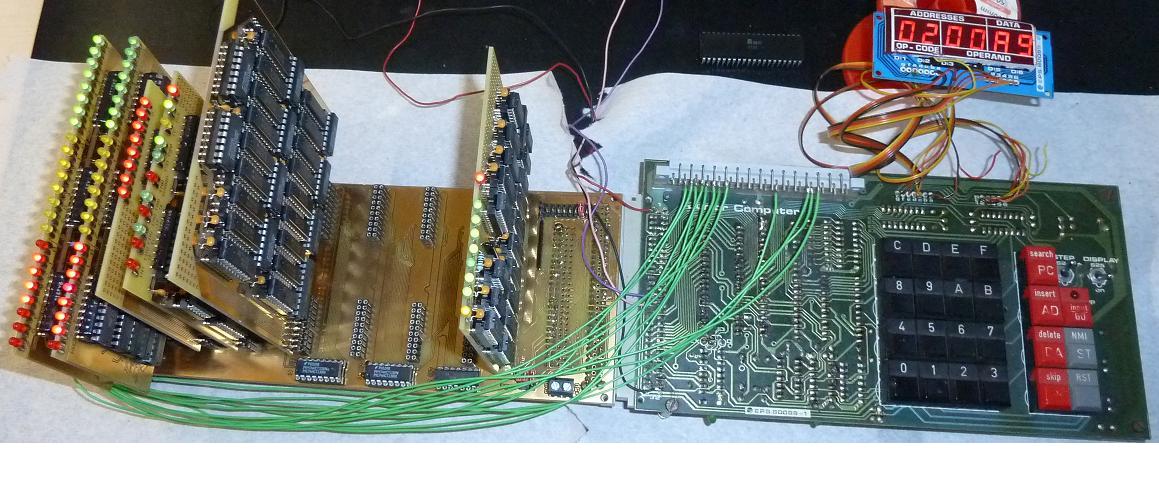

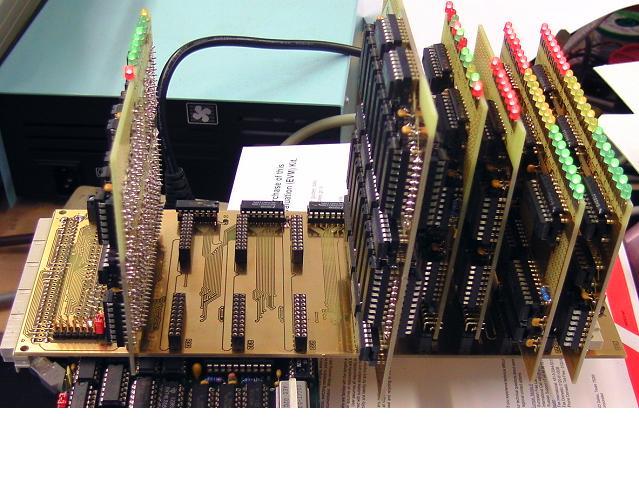

I also had an experimental 6521\6821 TTL implementation,

the experimental 6545\6845 TTL implementation had some serious issues (but at least it had generated a picture),

and the experimental 6551\6850 TTL implementation had failed (having three different clock domains in one design wasn't fun).

Hey, you recognize the pioneer by the arrows in his back.

;---

But back on topic:

The problem with the C64 timing is, that the 6510 address\data pins are in high impedance during PHI2 = LOW,

and that it takes some time until the 6510 puts the address on the bus after the rising edge of PHI2.

When taking a closer look at the bus timing in the 6526 and NMOS 6522 datasheets,

it appears that the 6526 needs a stable address on the bus before the falling edge of PHI2,

but the 6522 needs a stable address on the bus before the rising edge of PHI2.

So when looking into old schematics which show a 6522 on the C64 expansion port,

I think it isn't unusual to see something like PHI2 delayed with two flipflops clocked by the dot clock

for generating PHI2' for the 6522.

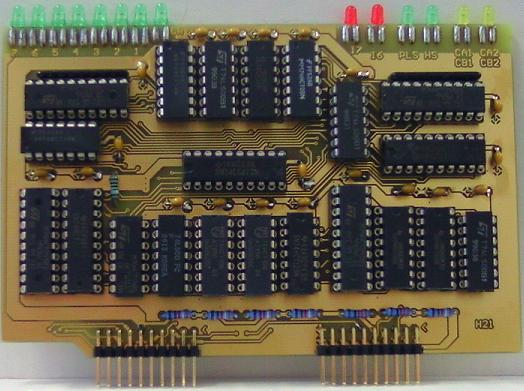

For building a 6526 TTL implementation, the TTL 6522 only might be "half of the rent", of course,

because in the 6526 a few things are quite different.

I see two main problems when trying to build a 20MHz TTL 6526:

First, the two 16 Bit timers could be "chained", so we need to keep an eye on that propagation delay for the TTL counters.

Second, that odd BCD clock... counter propagation delay might be getting an issue there, too.