Code: Select all

NET "O2" TNM_NET = O2;

TIMESPEC TS_O2 = PERIOD "O2" 20.5 ns HIGH 50% INPUT_JITTER 100 ps;

NET "O2Out" OFFSET = OUT 5.5 ns AFTER "O2" RISING;

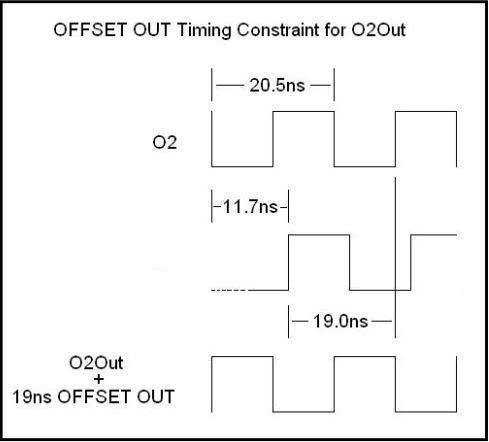

I was abit premature in my declaration of success 7 hrs ago. I later realized I had a timing constraint error because my 5.5ns "estimated" delay is shorter than the internal delay (as spec'd by ISE), from O2 to pad, of 11.7ns. Although the circuit still worked the best I had so far, it was locking up after some time (<1min)...

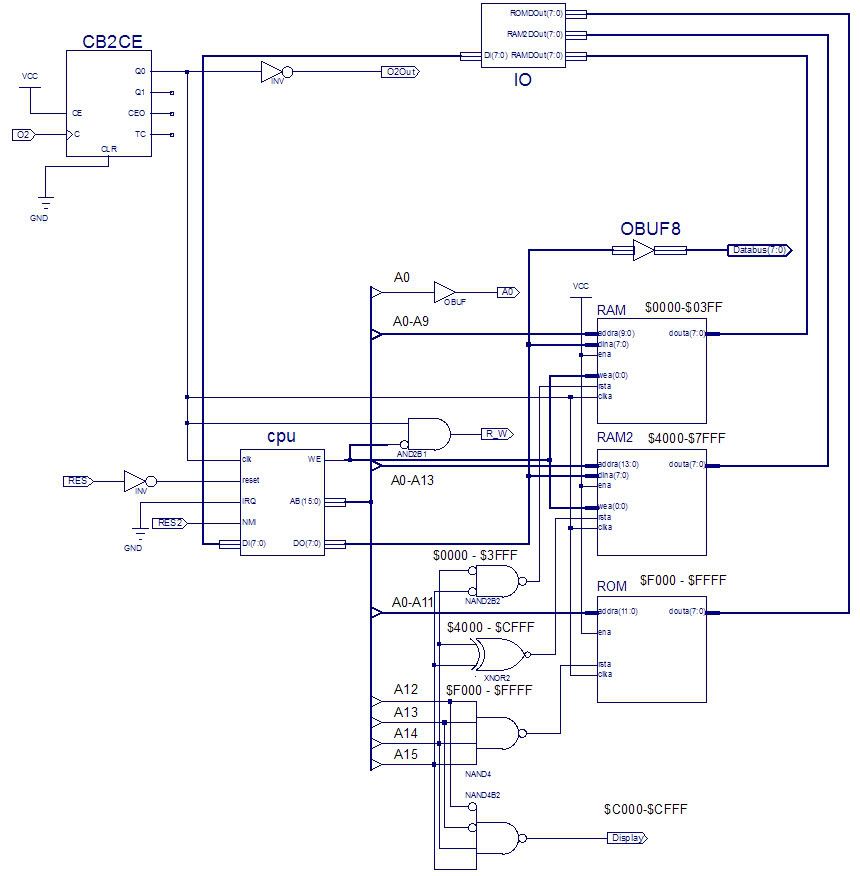

After looking over some of my old schematics from the PWA project, I decided to qualify WE from Arlet's 6502 core with O2/2. In addition, instead of an arbitrary 5.5ns, I calculated the actual time I needed to put O2Out in sync with O2, although the display likes an inverted version of O2.

The 6502SoC has been running now for over an hour with no problems @24MHz using this constraint with the schematic below:

Code: Select all

NET "O2" TNM_NET = O2;

TIMESPEC TS_O2 = PERIOD "O2" 20.5 ns HIGH 50% INPUT_JITTER 100 ps;

NET "O2Out" OFFSET = OUT 19.0 ns AFTER "O2" RISING;

Updated schematic:

Note(s) to self: After reading this post on my 2nd favorite forum, Xilinx forums, Austin Lesea (their principle engineer) comments on jitter value ranges. "...100ps for synchronous design with single clock...", and "...1000ps for... poor bypassing...".

A video about switch debouncing an FPGA.

A video about someone with similar ideas to mine using an XC3S400, T65 core, PS/2 interface, and an SDCard interface. Darn I though I would've been the only one, heh!, I'm always behind the power curve... I asked on his video what speed he is running the T65 core. Waiting for response, doubt I'll get any, been posted a year ago...