Page 8 of 15

Re: Breaking 6502 apart

Posted: Thu Oct 04, 2012 7:28 pm

by org

I try to explain my simulation of whole /NMI pin logic.

Overview:

Image no longer available: http://ogamespec.com/imgstore/whc506de23b60f71.jpg

So I simulate output as follow:

Code: Select all

b = NOR ( NAND(NOT(NMI_PAD), PHI2), NMI_LATCH);

NMI_LATCH = NOR ( NAND(NMI_PAD, PHI2), b );

OUTPUT_LINE = NOT(NMI_LATCH);

(

b is temporary value)

I drawn NAND/NOR counterpart of trigger on picture. So I think we need those "~".

As output I'm getting following data:

Code: Select all

L N Ф L*O

0 0 0 | 0 1

0 0 1 | 0 1

0 1 0 | 0 1

0 1 1 | 1 0

1 0 0 | 0 1

1 0 1 | 0 1

1 1 0 | 0 1

1 1 1 | 1 0

Where :

L - latch value before iteration

N - NMI pin level

Ф - PHI2

L* - latch value after iteration

O - output line

And it even worse, if you try to simulate /IRQ. It has additional PHI1 transfer gate + latch as output. In that case I'm getting only '1's on out.

Re: Breaking 6502 apart

Posted: Thu Oct 04, 2012 7:52 pm

by BigEd

It's not a nor of a NAND: it's a nor of an and.

Re: Breaking 6502 apart

Posted: Fri Oct 05, 2012 6:17 am

by org

Indeed, this is NOR of ANDs, I just checked truth table, thanks ))) Now everything works good )

Transition states of /NMI output line:

Code: Select all

L I Ф |L* O

0 0 0 | 0 1

0 0 1 | 1 0

0 1 0 | 0 1

0 1 1 | 0 1

1 0 0 | 1 0

1 0 1 | 1 0

1 1 0 | 1 0

1 1 1 | 0 1

Transition stated of /IRQ and RES lines (both have additional output static latch):

Code: Select all

L I P |L* O

0 0 0 | 0 1

0 0 1 | 0 1

0 1 0 | 0 1

0 1 1 | 1 1

1 0 0 | 1 0

1 0 1 | 0 0

1 1 0 | 1 0

1 1 1 | 1 0

Simulation can be found here:

http://code.google.com/p/breaks/source/ ... SRC/MISC.c

(I added some convenient macros like NAND / NOR, to increase source code readability)

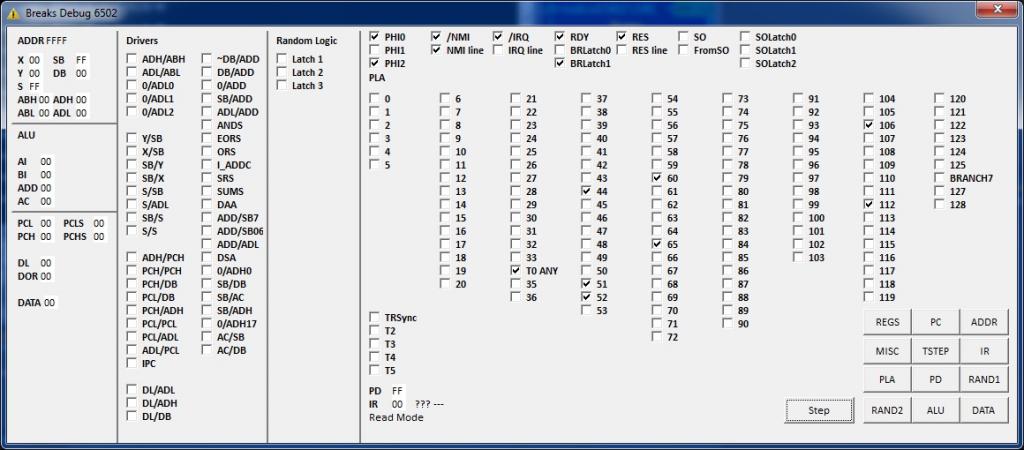

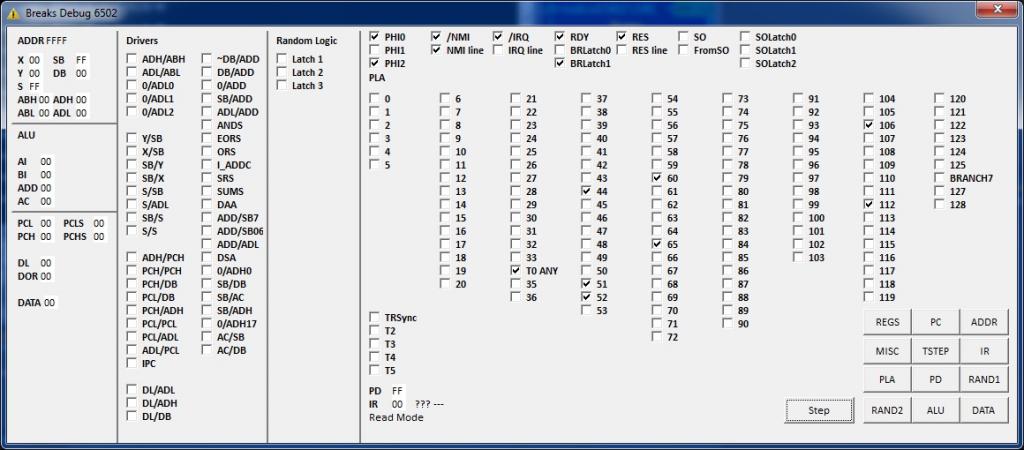

Also I started my 6502 debugger:

It may look more complicated, than other 6502 debuggers you've seen before

Re: Breaking 6502 apart

Posted: Fri Oct 05, 2012 6:31 am

by org

And another thing I want to show you:

http://ogamespec.com/6502/PLA.htm

This is tracing of PLA lines for every opcode on each cycle.

Re: Breaking 6502 apart

Posted: Fri Oct 05, 2012 6:35 am

by BigEd

Great stuff!

Have you tried to run your Breaks6502.exe on Linux using WINE? I'm willing to try it if you make the exe available (maybe in a zip file)

Cheers

Ed

Re: Breaking 6502 apart

Posted: Fri Oct 05, 2012 6:39 am

by org

It should run under WINE without any trouble. I'm using plain winapi.

Here:

http://code.google.com/p/breaks/source/ ... runk/Build

Re: Breaking 6502 apart

Posted: Fri Oct 05, 2012 7:00 am

by BigEd

Thanks - it does open the front panel and another window! Some but not all checkboxes work, and the Step button causes the clocks to toggle and produces some output on the console. (I don't see anything in the second window)

Code: Select all

$ ./Breaks.exe

Debug console opened

IR unchanged: PHI1=0 / fetch=0

IR unchanged: PHI1=1 / fetch=0

IR unchanged: PHI1=0 / fetch=0

IR unchanged: PHI1=1 / fetch=0

This is a good sign, I think, for Linux users.

Cheers

Ed

Re: Breaking 6502 apart

Posted: Fri Oct 05, 2012 7:08 am

by org

Some but not all checkboxes work

Its not ready yet

I'm going to start simulate random logic soon. Most interesting part of my research )

Re: Breaking 6502 apart

Posted: Fri Oct 05, 2012 7:21 am

by BigEd

Its not ready yet

I'm going to start simulate random logic soon. Most interesting part of my research )

Understood - look forward to more updates!

Re: Breaking 6502 apart

Posted: Thu Oct 11, 2012 10:20 am

by org

Fixed some errors in PCL circuit and completed Program Counter increment logic.

I do not know why PCHS/PCLS registers are get inverted after every PC increment.

For example when PCHS/PCLS=0x1234 incremented, it become 0xEDCA (inverted 0x1235). So if you try to increment it again, without altering PCHS/PCLS it become again 0x1234 (inverted 0xEDCB)

I guess PCHS/PCLS is additionally inverted somewhere through ADH/ADL bus for example (since PC is connected to ADx bus via some drivers)

PC get incremented when IPC driver become low.

Re: Breaking 6502 apart

Posted: Fri Oct 12, 2012 12:29 pm

by org

Completed Predecode logic simulation.

Predecode has two outputs : /TWOCYCLE and /IMPLIED.

Predecode determine whenever instruction takes 2 cycles to execute or it has no operands (implied).

Two-cycles instructions are actually all implied (except push/pull) + ALU operations with immediate operand.

I attached screenshots with list of 2-cycle and implied 6502 instructions.

Re: Breaking 6502 apart

Posted: Fri Oct 12, 2012 12:43 pm

by BigEd

Do you still have the inverting PC problem? I think it must be a bug - I'm pretty sure I've never seen it on visual6502.

Re: Breaking 6502 apart

Posted: Fri Oct 12, 2012 12:55 pm

by org

I'm going to research reset sequence, to know more details on PC updating, so it must be fixed.

I cannot detect bug, by looking from inside of PC logic.

Re: Breaking 6502 apart

Posted: Wed Nov 14, 2012 11:21 pm

by org

In case you guys remember me, I started my own site for Breaks project:

http://breaknes.com/

And I'm gonna return to 6502 soon, I have some progress to show you )

Re: Breaking 6502 apart

Posted: Thu Nov 15, 2012 7:05 am

by BigEd

Very nice - I'm surprised that Icc isn't the best compiler for Intel.

How much 6502 simulation is working now? Can you run short instruction sequences?

Cheers

Ed