The last part to optimize was the 6502 IO section, as my old system only ran the CPU at 10MHz.

I did manage to get 14.318MHz several times, but after the IO decoding was added, it became a bit unstable.

So.... I learned a few new tricks!

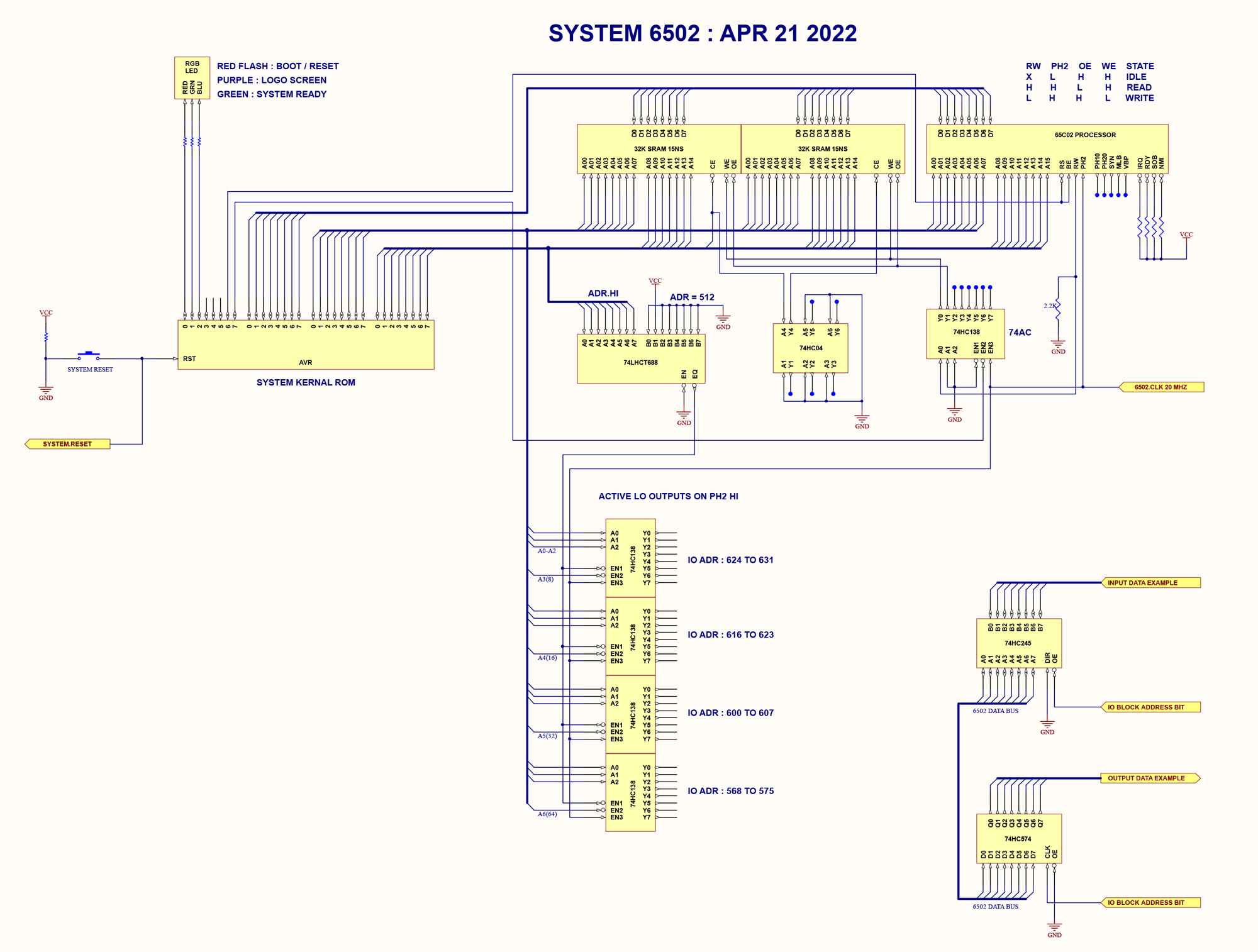

First, have a look at this...

I used to gate RW and PH2 using the usual NAND schematic that seems to be the accepted standard. This works well, and only adds the propagation delay of 2 NAND gates at most, so let's just say it has about 16 nanoseconds of delay.

I wasn't satisfied with that, so I tried a ton of different schemes to finally come up with the one shown above that only introduces 4 nanoseconds total!

This is of course using AC logic, but even with plan old HC (8 ns delay) logic, 18 MHz was stable.

The secret sauce : using a single 138 as the RW/PH2 gating.

I call this setup stable at 20MHz because it will actually do 25MHz, and breaks down around 28MHz. This is my margin of safety.

My IO decode logic is also greatly simplified, feeding the address and select line of the four 138s directly form the lower address bus after triggering the chain from the higher bus at address 512. This is working perfectly on my massive board, and the 65C02 is a real performer now!

Also not that this is the WesternDesgin 65C02, not the TTL version, and I am running fully from 15ns SRAM that has been boot loaded with my Kernal.

A system kludged down with ancient ROM would probably never achieve this level of speed without some serious variable clocking magic.

I am also using my slowest (15ns) SRAM with an inverter to tie the 32K together. I bet 25 MHz or better is possible with 10ns SRAM!

That's it for now, just wanted to share my discovery.... 20MHz 6502 Baby!

Will post some eye candy soon, Vulcan-74 is now 100% logic based and pushing our 360x240 NTSC with 16384 colors.

Blitter performance is just smokin' fast now (10 million pixels per second on a 16 bit video databus!), I am kind of laughing at my previous works now.

Later!

Brad