I see no reason you can't just make TEXT_START point to $2000.

As for the zero page addresses, if you use your KIM functions for your keyboard/screen I/O then you may need to watch for clashes with my own definitions. $C0 onwards is free as far as I am concerned, so you could juggle things around if needed. For example if your KIM routines use $00 to $1F then just start mine at $20 by putting an ORG directive in zp_variables.inc. Or, move individual ones around.

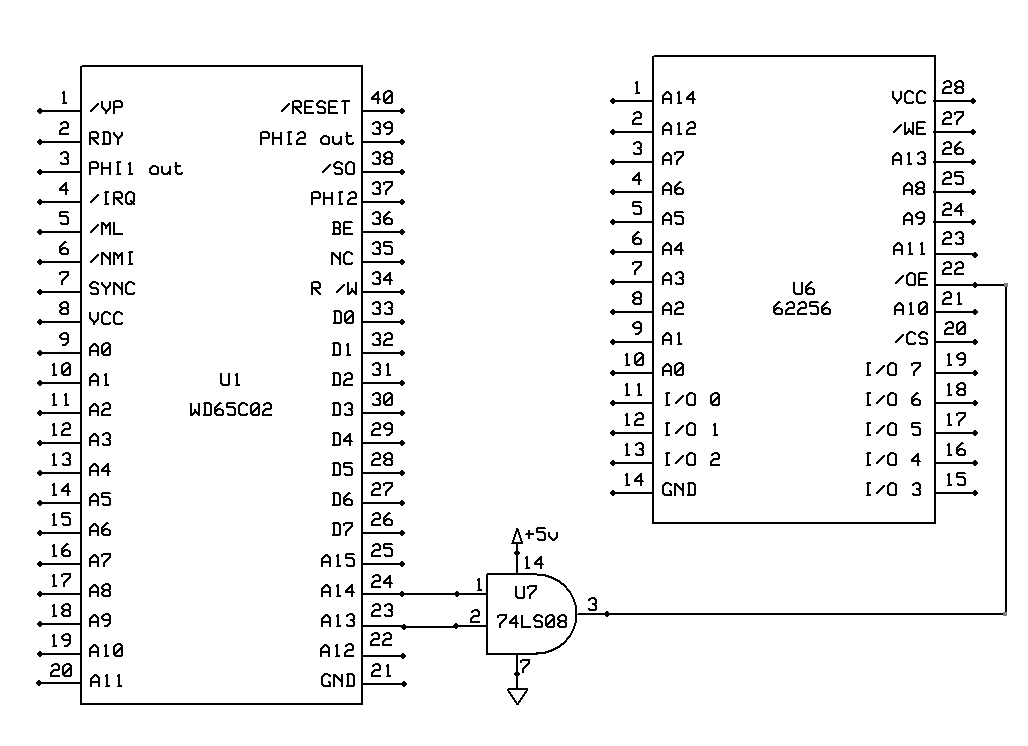

You would indeed need to look at hardware.inc, as well as interrupts.inc, in particular from "here for a hardware IRQ" onward.

If the KIM has ROM at $FFFA onwards (for the hardware reset vector etc.) then you will need to somehow hook into my code somewhere.

At the start of ROM I have two jumps:

Code: Select all

JMP START ; where RESET takes us - a cold start

JMP RESTART ; where NMI takes us - a warm start

Is this a standard layout? If so I can put in conditional directives to make it work for other people with minimal effort on their part.