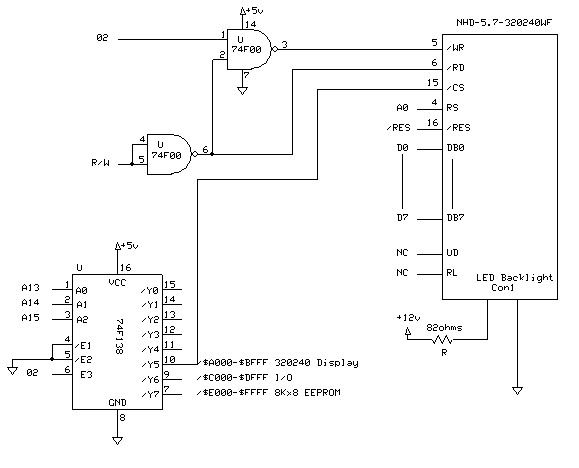

I'll check on the VSYNC value... I have tried to change many settings, The one a had to modify is the rotate register because I unknowingly mounted it upside down when I made the mounts and connections. Without the init routine the screen starts out with multicolored static, so I know all the reg's are being written.

75% of the time the display will boot up properly after a power up. Once in awhile I'll have to reset it a couple times for it to work.

I'll try your suggestion on the write/read from some registers.

There's no mention on the New Haven datasheet about the display being 5V tolerant, however the FSA506 datasheet does say this in chapter 6.1:

"6.1 DC characteristics

DC Characteristics of 3.3V with 5V Tolerance I/O Cells"

Since the circuit board only contains that one chip I assumed that it is 5V tolerant, except the /res. But that is only pulsed quickly so I'm not worried about overloading that line.

Well if we can't figure out this problem, I will have to assume there was a problem inherent in the design and that is why they stopped selling it right after I bought it.

A few other notes though. They still have an app note for the 8 bit version. I don't know the language it is written in but I see there is a delay definition in the code, which is why I started experimenting with delays in the first place. Here's the link:

http://www.newhavendisplay.com/app_note ... 6_8bit.txt

Maybe someone can interpret it.

Also, this display is supposed to have 256K colors, which is 18bit data, which means I would have to send 3 consecutive 8bit data. When I try that it looks screwy.

It seems I have only 65K colors, sending 2 consecutive 8bit data works.