TTL Compatible... NOT! ( modern WDC CPU's )

In this thread I'd like to talk about the practice of using modern WDC CPU's in conjunction with RAM's, ROM's or PLD's etc whose output specifications only guarantee TTL voltage levels. Can the inputs of WDC processors be reliably driven by TTL voltage levels, or is it better to include pullups or level shifters? Are WDC's inputs "TTL compatible"?

We will see they are not. It's true that some RAM's, ROM's and PLD's have a limited degree of

WDC compatibility

in the sense that they exceed TTL specs. But WDC's inputs are not TTL compatible. WDC inputs are markedly different from Rockwell's, for example. A comparison of Rockwell and WDC input specs reveals this, and the info is confirmed by my actual testing, reported below. Rockwell CPU's

can reliably be driven by TTL voltage levels, but

WDC chips are TTL Compatible only in the anecdotal sense. People have reported success using them in a TTL setting -- it's not uncommon. But this is not a robust combination, nor one that's even guaranteed to work.

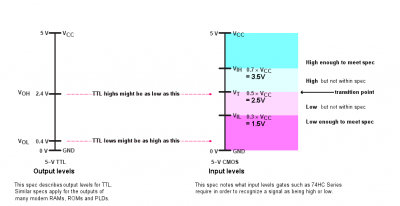

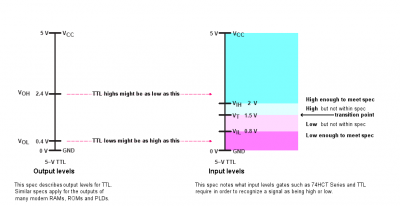

Datasheets specifications can be hard to interpret, so I've prepared two sets of graphics. The first set is slightly OT because it discusses gates, not CPUs. But that's a good analogy, because most of us already know it's an iffy proposition to have TTL outputs driving CMOS inputs such as those of the 74HC series. (The situation with gates is well known, and my graphics are based on a diagram excerpted from page 4 of the attached document from Texas Instruments.)

This doesn't mean a 74HC device is guaranteed to fail.... but if it works it'll be for reasons that can't be relied upon:

- The output may come from a chip whose highs are higher than spec and whose lows are lower than spec. And,

- on the input side, you'll notice that the specs call for highs that are above the actual transition point and lows that are below that transition point. So, the specs call for some extra margin. But cutting corners with that margin won't necessarily result in failure.

What I hope will jump out at you is the fact that a TTL high

which merely satisfies spec (ie, doesn't exceed spec) will fail to drive a 74HC input high, because the transition point won't be achieved. It is actually imperative for the TTL chip to exceed the VOH spec. Indeed, you'll even want it to exceed the transition point somewhat; that's so you'll have a little bit of noise immunity (imperative to avoid flaky operation).

- TTL output voltages are a poor match for CMOS inputs such as those of the 74HC series.

- TTL output voltages are a good match for TTL inputs (also inputs of TTL-compatible CMOS such as 74HCT series).

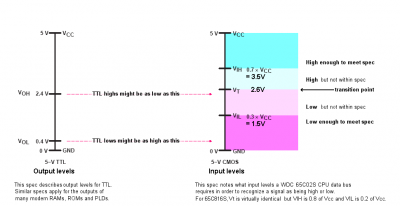

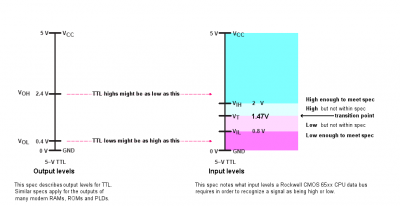

Here's the other set of graphics, and now it's CPU inputs I'm illustrating. It's much the same story.

- TTL output voltages are a poor match for the inputs of WDC CPU's.

- TTL output voltages are a good match for the inputs of TTL compatible CPU's such as Rockwell.

My reference for logic family voltage levels is the TI document attached. Unlike datasheets, it mentions the actual transition voltage -- something which datasheets typically omit, for various reasons. (Manufacturers want to reserve themselves some leeway. And the customer supposedly doesn't need to know the transition point anyway; their job is simply to adhere to the max and min specs.)

For 65xx CPUs I found it necessary to do my own research.

I measured the data bus input transition voltage for three 65xx CPUs, as follows. (I haven't tested WDC microcontrollers, but I see no reason to expect them to be different.)

- Rockwell R65C02P4: 1.47V

WDC 'C02: 2.6V

WDC '816: 2.57V

From this we see that driving a Rockwell CPU is like driving 74HC

T series CMOS. And driving a WDC CPU is like driving 74HC series CMOS... which is to say, for reliable operation you'll need pullups or a level converter IC if the driving IC only guarantees TTL levels.

In a subsequent post I'll share the test circuit I cooked up -- I'm rather proud of its simplicity.

And I have plans to verify the input transitions for other inputs such as IRQ and BE. But with summer coming on I'm not sure how soon I'll get around to doing that...

-- Jeff

PS: mug shots of the suspects:

TTL