Part 1: https://www.youtube.com/watch?v=idUfXag8pQo

Part 2: https://www.youtube.com/watch?v=VJFIvmkbCA4

Part 3: https://www.youtube.com/watch?v=HzgjMjqpOC8

I know a number of other cores have been written to reproduce the VIC-II but I don't think there are any projects that can actually plug into a real C64. (Copperdragon and Beamracer still require a real VICII). My core will be open source when it's done and the hardware design will be open as well. I'm aware that this is going to be many times more expensive that just buying a genuine chip. This project isn't for money, it's for interest and the challenge. It also makes for some other interesting projects possible (like adding a new graphics mode, more sprites, custom palette, math co-processor, etc.). Of course, all just for interest's sake for hobbyests.

A similar project was started by Rob Finch a few years ago but his project was never finished. (He is also a member of this forum). He posted an issue he was having re: noise on this forum

https://forum.digilentinc.com/topic/194 ... gnd-noise/

The project has been quite successful so far. I have a working prototype that is functioning well enough to play games. I can leave it on overnight and it's still running in the morning. It is fairly accurate at reproducing the VICII as I've been validating behavior using VICE and a custom IPC bridge to my verilated simulator executable. I've also tested it against 280 VICE VICII test programs and they are all now matching what VICE produces pixel for pixel.

Unfortunately, I am also running into a noise issue and I think it's the same issue Rob described in his post. So I'm reaching out to the experts in this forum for some advice on how to proceed from here.

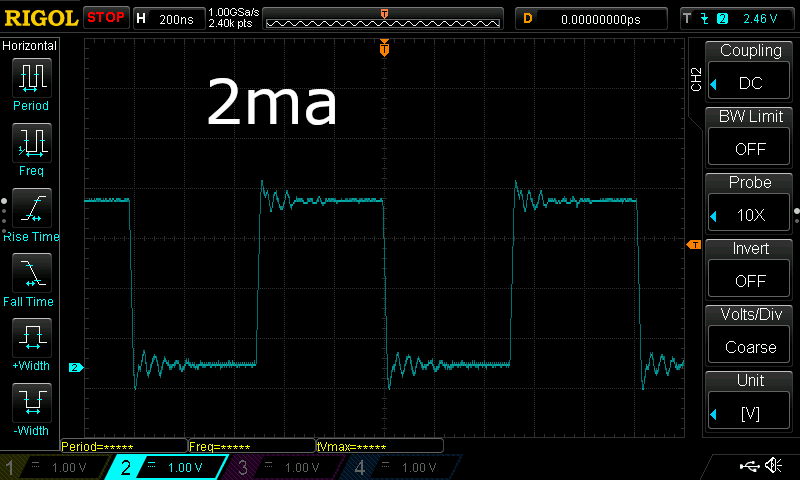

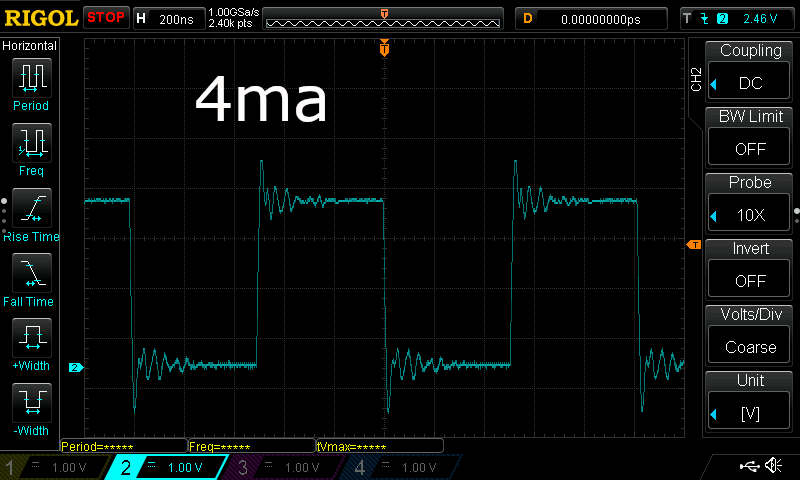

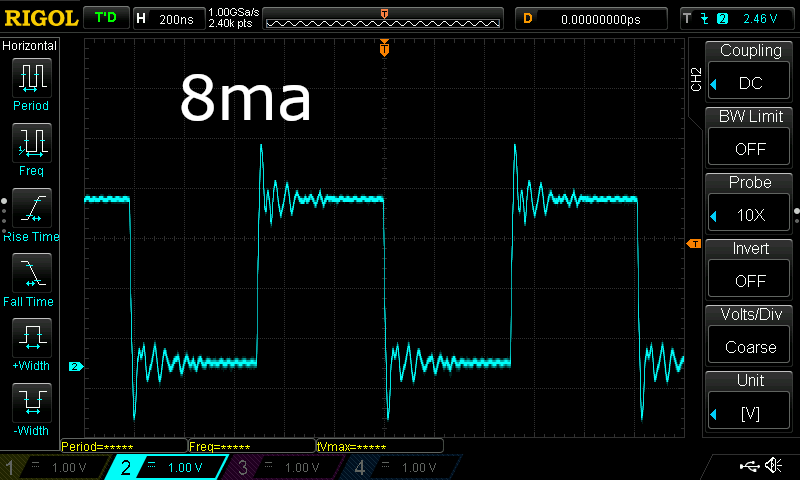

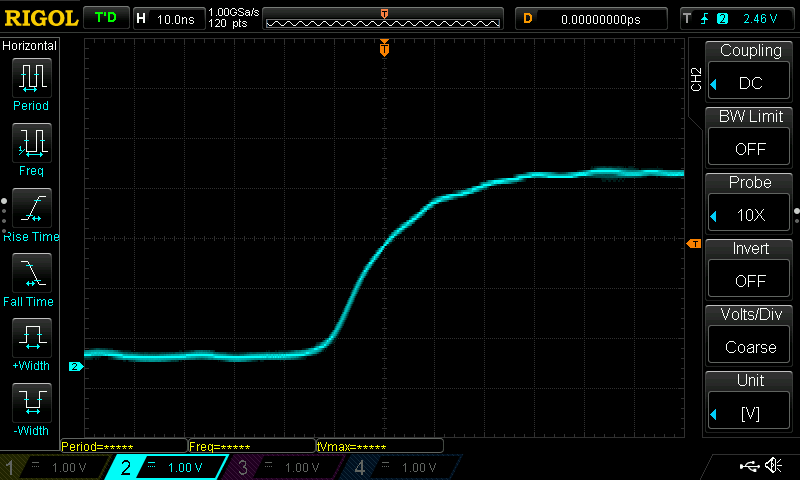

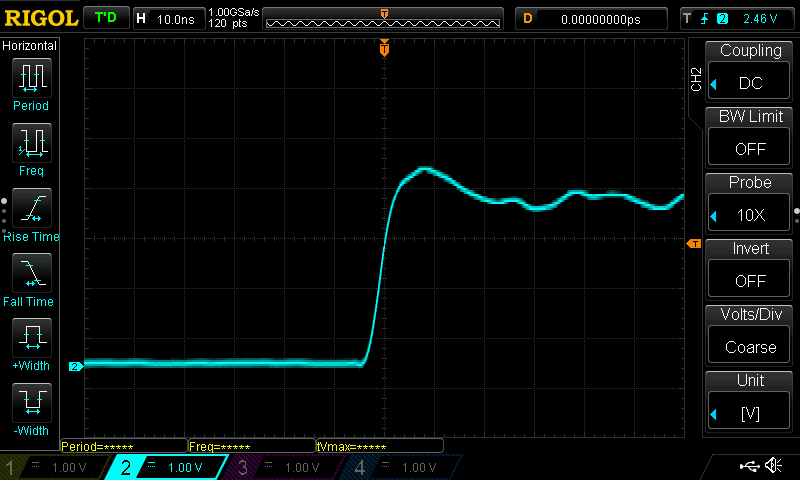

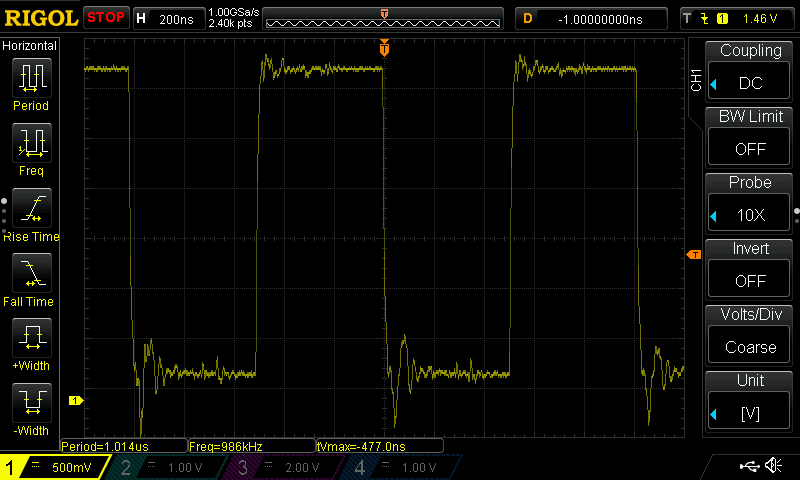

In a nutshell, this picture illustrates my issue:

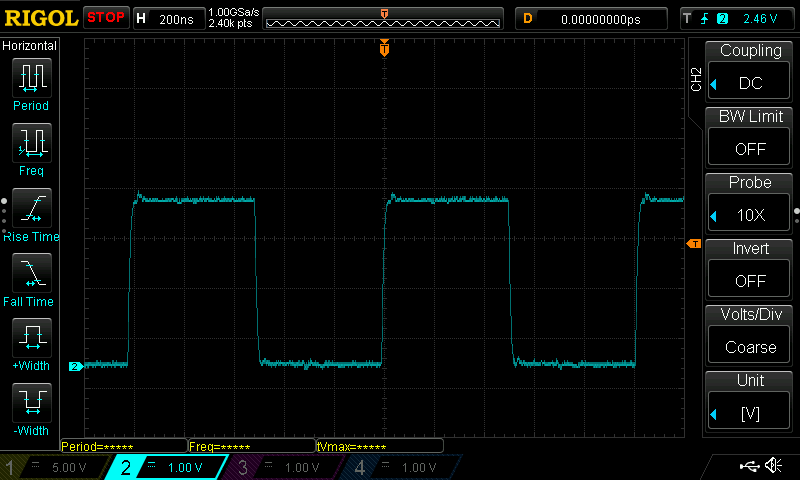

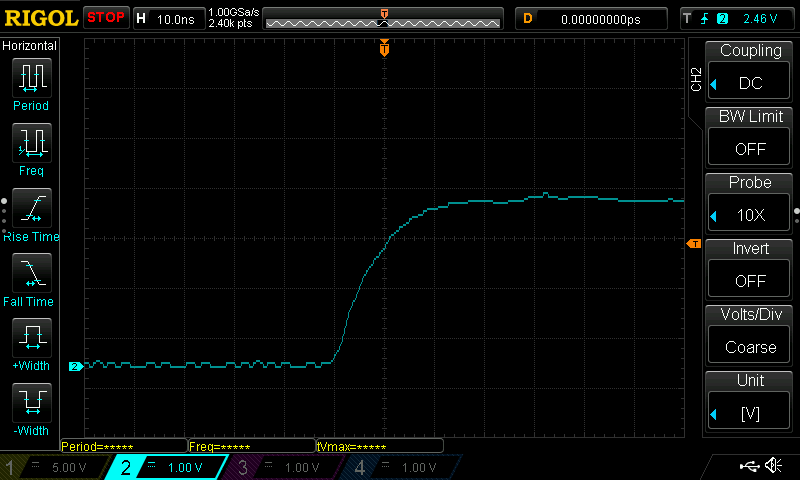

This is the PHI clock signal measured from the input pin of the 6510. When I measure the clock on the corresponding FPGA pin (on the FPGA side of the transceiver), there is no noise. The signal is quite clean.

I am using five 74LVC4245 bus tranceivers between the C64 VICII socket and the FPGA. One is for dedicated read signals, one for dedicated write signals and 3 for bi-directional data and address buses. I have .1uF capacitors at every Vcc pin on each of the transceivers.

The C64 seems to deal with the noise for the most part as I can play games and run most demos with no problems. I do get the occasional CPU JAM when I run the more complex demos though. I'm hoping if I can address this last issue, that problem will be solved (hoping).

The noise in the image happens when I switch the address tranceiver's direction from input to output. On the LOW phase of the PHI clock cycles, the VIC owns the address bus and sets the address to read char and pixel data from ROM or RAM. I've run some experiments and the noise disappears if I keep the address bus transceivers to read direction only. The switch happens on AEC edges which is slightly delayed wrt to PHI.

Also, if I unplug the device from the C64 socket and measure the clock output pin, even with the direction switches in place, there is little noise.

Anyway, there is probably a lot more info you would need to diagnose so I'll leave it at that for now. I'm basically at the end of my abilities for this project and was hoping an EE could help me with trying to fix this. If anyone has any ideas I can try, please let me know. Thanks!