Hello again, all, and sorry for the delay. (And no worries, BDD.) apoloval, does the correction I offered regarding your BE post seem appropriate? I get that you want to avoid bus contention during the time of the first hazard (roughly when Phi2 rises) by forcing one of the contending parties to desist. (By parties I mean the '816 CPU and whatever device is attached to it on the motherboard.)

Your most recent post describes a more familiar and more effective setup. Instead of controlling the CPU's BE you're controlling

a transceiver aka tristate buffer that separates the CPU data bus and the memory data bus. ( Separate data buses linked by a transceiver is a typical configuration, suggested in the WDC '816 datasheet. )

I'll begin by reviewing the second half of the cycle. This is the handoff from the CPU to the buffer. The buffer (which will be delivering read data) remains disabled until...

- D: 10ns before PHI2 fall edge. The memory controller activates the buffer that drives the CPU data bus from the Memory data bus. [...]

- E: PHI2 fall edge. The CPU reads the data from its data bus.

Alright, that makes sense, but what allows you to drive the data bus at exactly the time you mention? In real life, the buffer takes some inexactly known amount of time to begin driving. Rather than giving an exact figure, the datasheet for the buffer states the minimum and maximum enable time (the time from when the buffer is told to begin driving until it actually does so).

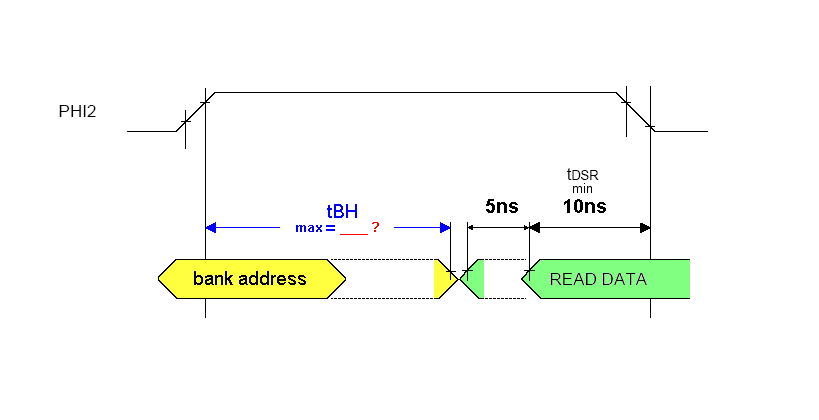

For ease of discussion, let's say the buffer-enable delay is listed as min 0 to max 5 ns. And in the diagram below, tDSR from the '816 datasheet tells us the deadline by which the read data needs to be valid -- there needs to be at least 10 ns of setup time before Phi2 falls. Assuming, as I said, between zero and 5 ns of buffer-enable delay, that means for reliable operation the buffer needs to be told to enable 15 ns before Phi2 falls.

Trouble is, we have no explicit assurance the CPU will have

stopped driving by then.

- handoff from the CPU to the transceiver

- 65816 timing01.png (6.44 KiB) Viewed 5107 times

Because we know how long the Phi2-high pulse lasts, all it takes is some simple math to reveal what's the largest tBH figure we can tolerate. But the '816 datasheet

fails to specify a max figure for tBH; only a min figure appears. As far as I can tell, the omission of a max tBH figure scuttles any attempt at a rigorous solution for avoiding contention. WDC's omission forces us to use seat of the pants solutions rather than real engineering.

( I can think of factors that lessen the bad news about contention, and I can think of factors that make it worse. But for the moment let me stay on focus. And to be clear: I'm

not saying seat of the pants solutions are ineffective -- I'm just saying we shouldn't be forced to work that way. )

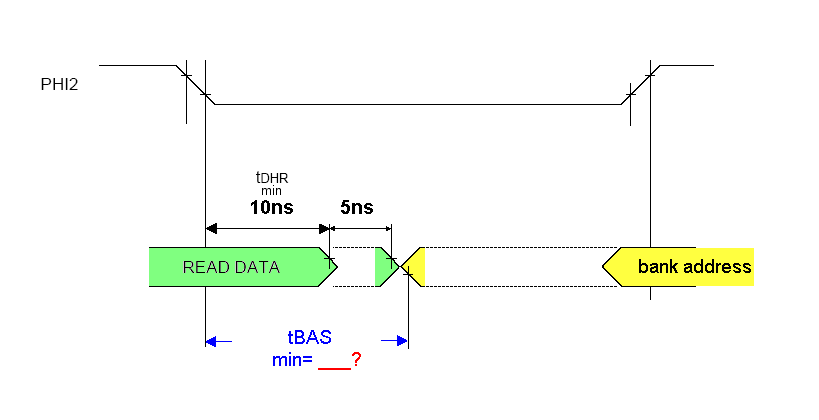

Now here's the other handoff, this one from the buffer to the CPU. It's a similar situation, unfortunately.

- handoff from the transceiver to the CPU

- 65816 timing02.png (6.2 KiB) Viewed 5107 times

The '816 datasheet tells us data on the bus must remain valid for at least 10 ns after the fall of Phi2 -- this is tDHR -- and let's assume the buffer has a 0 to 5 ns disable delay. If the buffer is told to disable 10 ns after the fall of Phi2 then in total it may drive as late as 15 ns past the fall of Phi2.

Now we have a figure (15 ns) for the smallest tBAS figure we can tolerate before a collision occurs. We don't want the Bank Address to appear too soon. But the '816 datasheet doesn't offer any warning or reassurance about the possibility of tBAS being smaller than 15 ns. No min figure for tBAS is specified; only a max figure is provided!!

I think we all realize bus capacitance can

usually be relied upon to maintain the state of the bus for a short time, and thus the command to disable the buffer needn't be as late as I suggested (ie, it can be earlier than 10 ns after the fall of Phi2). But you mustn't disable it

too early or it'll fail to establish valid levels in the first place.

Instead I wish WDC had simply provided a min figure for tBAS and a max figure for tBH as they ought to have done -- that's what I'm mainly saying.

- A: PHI2 raise edge. This is the strobe signal for address and bank address. The memory controller latches the bank address in a register. And MA (Memory Address) is driven with the 24 bits of the address obtained from A and D.

- B: 10ns after PHI2 raise edge. The MAS (Memory Address Strobe) signal is asserted. This will be used by the selected SRAM chip to read (specific chip selection by address range is not included in the diagram).

There's maybe something you're missing here, which I'll deal with quickly as it doesn't affect what I had to say above. It's necessary for the system to acquire the entire 24-bit address before Phi2 rises. That's so there'll be enough time for the memory decoder to select the appropriate RAM, ROM, or peripheral. Note that 65xx peripherals such as the 65C22 VIA require their chip-select inputs to be valid before Phi2 rises. Although it may be said that the Bank Address "is latched" when Phi2 rises, remember it's a transparent latch that's presumed -- ie, a '573, not a '574. Thus the Bank Address will already be flowing through the latch before Phi2 rises. When Phi2 rises it then

stops flowing, freezing the state established before.

Hoping all that's clear... whew!

Jeff

[edit: better diagrams, tweaked text]