Welcome to the world of 6502!

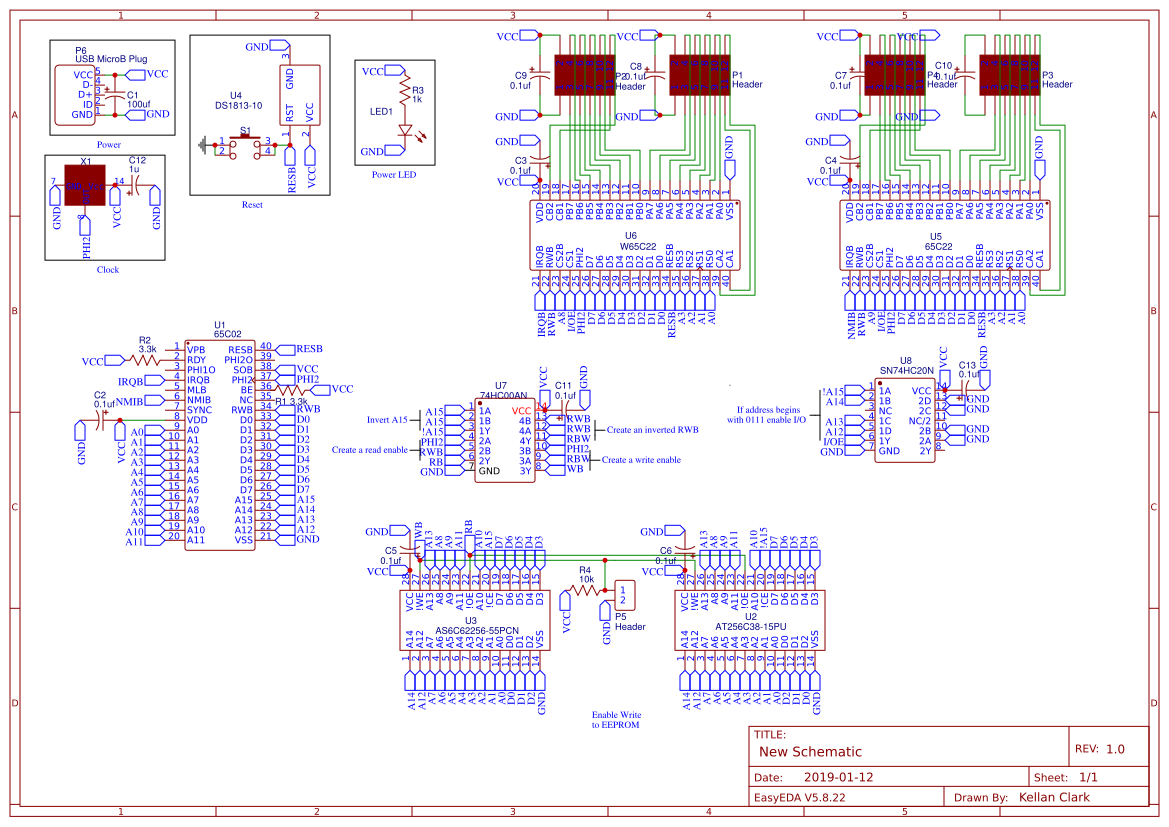

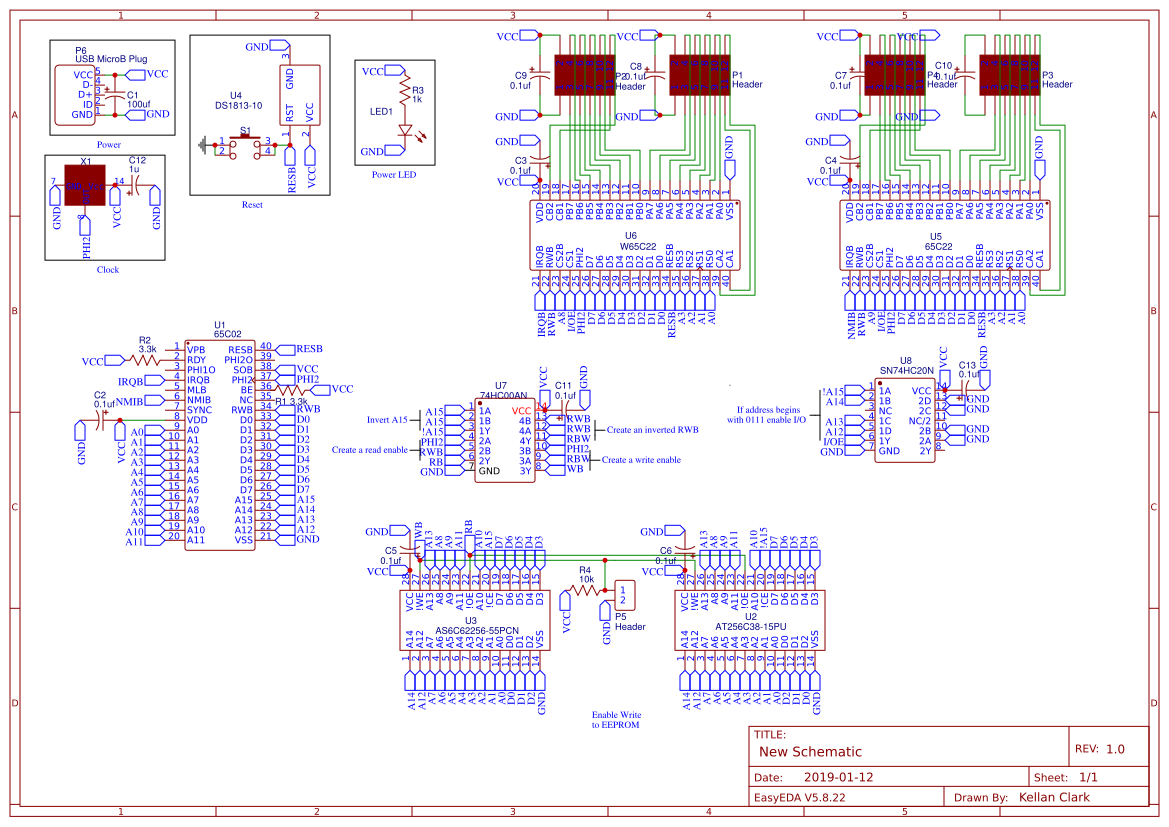

For future reference, when you post a schematic here, it's a good idea to post them in black and white. There are some people here who are colourblind, at least one of whom is very knowledgeable.

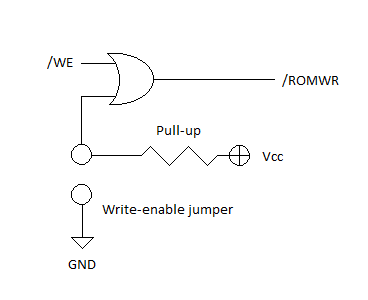

For the EEPROM write-enable jumper, I'd recommend using something like this(I use this in my own design):

- Write-enable jumper.png (3.55 KiB) Viewed 1010 times

This will ensure that your EEPROMs /WE input is deasserted(high) when the jumper is removed, and when inserted, /WE will be asserted when /WR is.

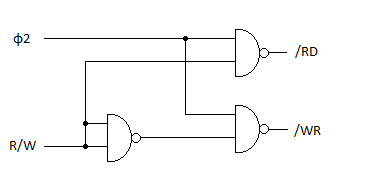

Your /RD and /WR generation isn't quite there. As it sits, you are generating /RD correctly(You've called it RWEB), but your /WR(RBWE) isn't correct, because it will be true whenever /RD is false, and that goes false when phase 2 is low. This will generate spurious writes(if those hit the EEPROM, your SBC will probably crash). I'd use a circuit like this, using gates from your 74HC00:

- RD and WR generation.png (2.63 KiB) Viewed 1010 times

I also notice a complete lack of serial I/O. You may want a UART to make getting a display a bit easier(It's not necessary to it, though).

If you do choose to include a UART, I recommend staying away from the 65c51. It has a hardware bug that means it always reports as if it's completed transmitting a character, even when it's right in the middle of doing so. You can't use interrupts, and you can't poll it, so you have to time it somehow.

I would recommend the NXP 28L91 or 28L92 if you want a UART. You could also probably include a USB-to-UART chip there, as well, using the USB port that's already there.