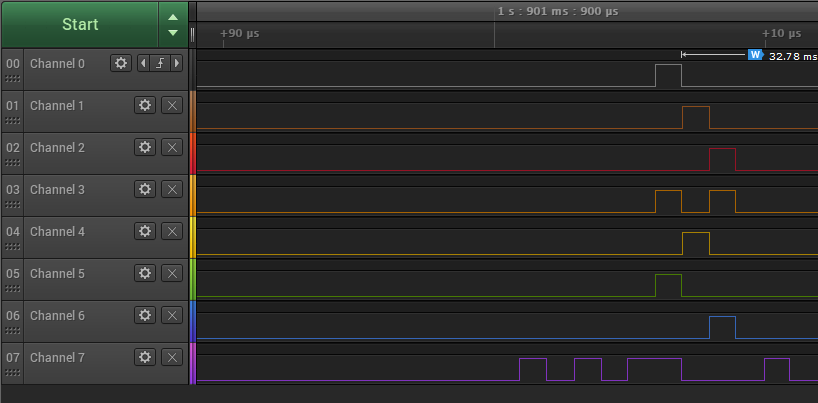

The question of memory address became much clearer. But now I'm stuck at another point. I picked up my logic analyzer (8 channels) and plugged it into the ROM data bus (D0-D7).

My ROM is as follows:

0x0000 A9 (LDA)

0x0001 12 (# $ 12)

0x0002 4C (JMP)

0x0003 00

0x0004 80 (here it comes back from the 0x00)

....

0x077A 00 (NMI lo)

0x077B 80 (NMI hi)

0x077C 00 (RESET lo)

0x077D 80 (RESET hi)

0x077E 00 (IRQ)

0x077F 80 (IRQ hi)

Looking at the logic analyzer, let's say this is the time moment "t":

If you look at the bus, it will:

80 (NMI hi)

00 (reset lo)

80 (reset hi)

00 (irq lo)

80 (irq hi)

A9 (lda)

12 ($12)

4C (loop)

00

80

So far I believe that everything is ok. At time "t + 1" time, it executes everything again, passing through the vectors. Should not it after the loop (8000) go back to the A9?

I do not know if my explanation was clear .. thanks!