I have decided to start a new lofty project I call “Anvil-6502”, or just A65 for short. There are several reasons for the name I have chosen…

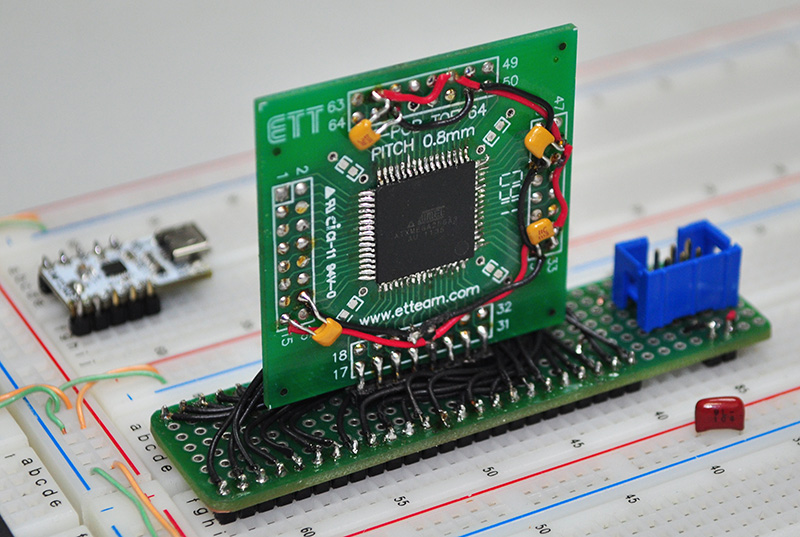

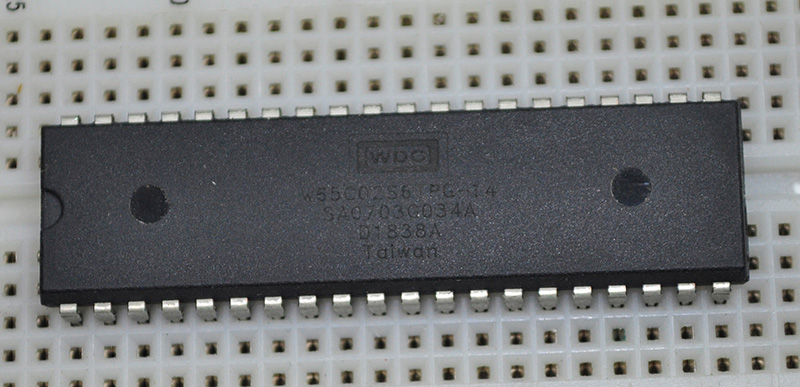

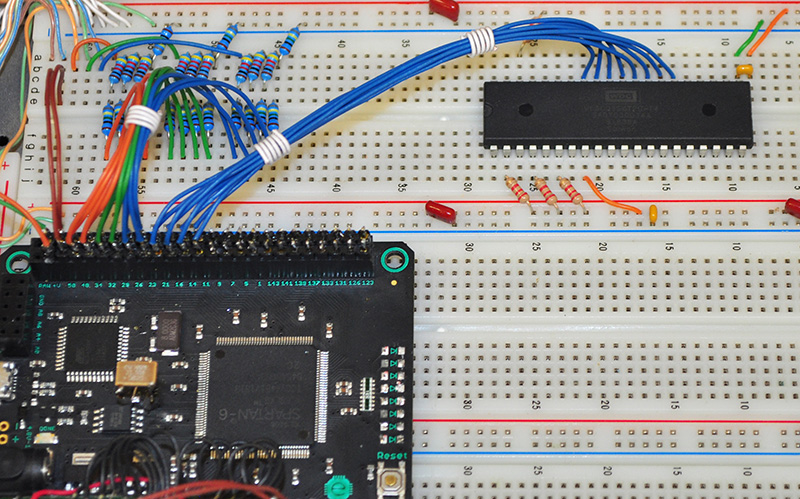

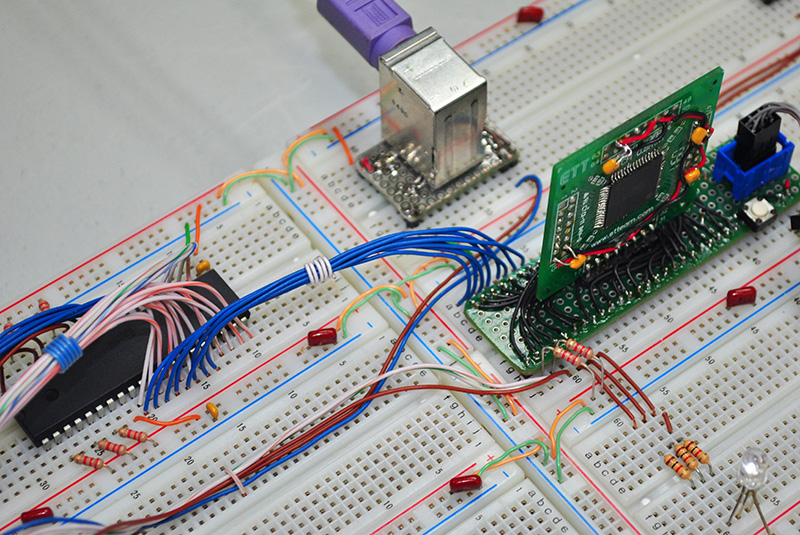

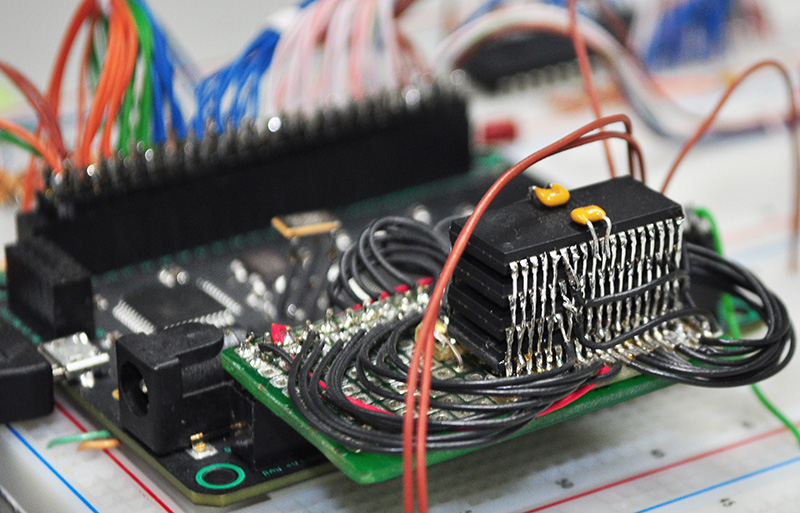

1) The system uses a real 65C02 DIP, like my favorite computers of the 1980s.

2) The 6502 does all of the work, talking directly to the hardware (Bare Metal Model).

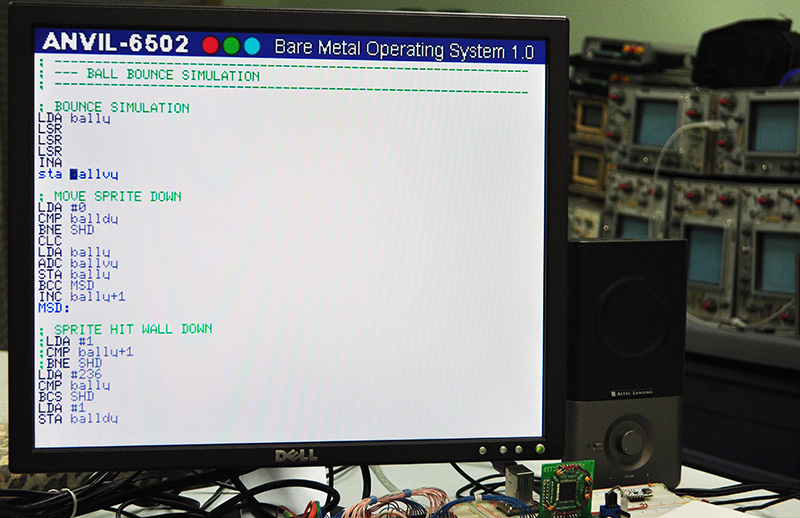

3) BMOS - The Operating System (Bare Metal Operating System) includes an assembler.

So, much like using an Anvil, you have to “Hit The Bare Metal” to write code for The A65!

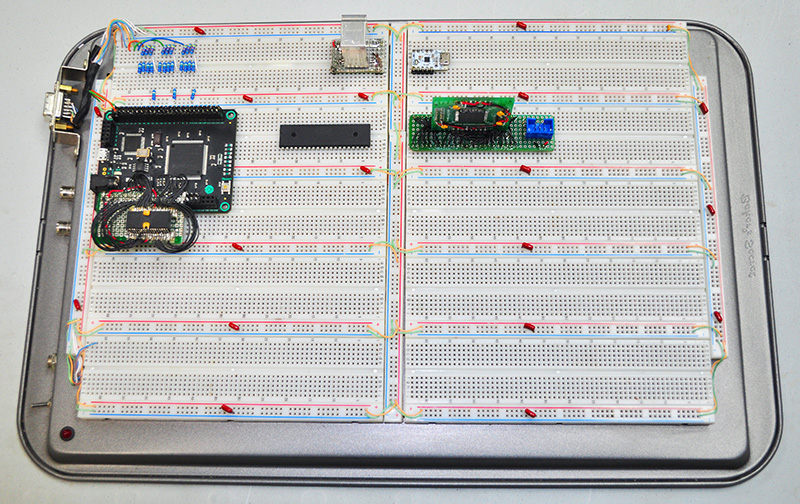

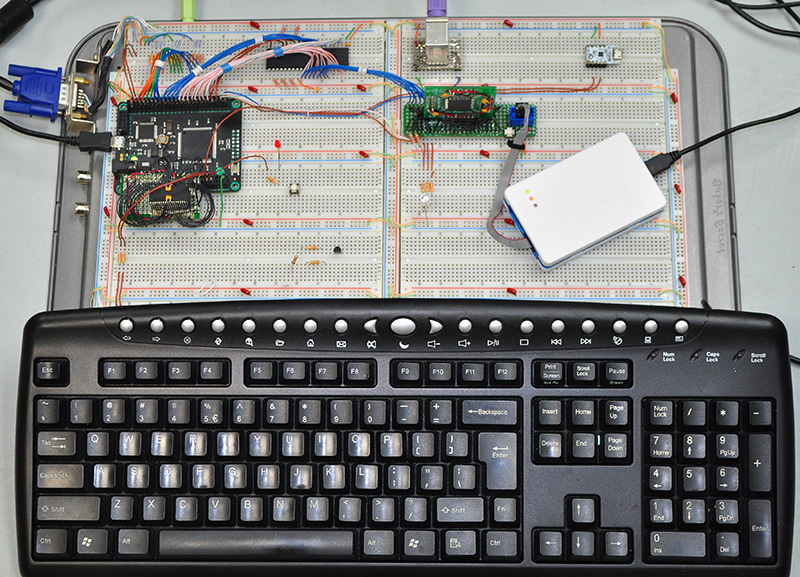

Anvil-6502 will also be fully self-contained, and not rely on any outside input other than what is entered by the user on the attached keyboard. This is a fully working 6502 based computer that will include an IDE and several programming tools directly in the Operating System, which will all be running on the single onboard 65C02 Processor.

The reason for the existence of A65 is so that I can temporarily escape from the current world of bloated code, IP cores, code wizards, high level fluff, and “Duino” flavored spoon-feeding technologies that try to make it so that a stoned monkey could create a working program by randomly hammering on a keyboard, even if half the keys were broken. (whoa... I know!).

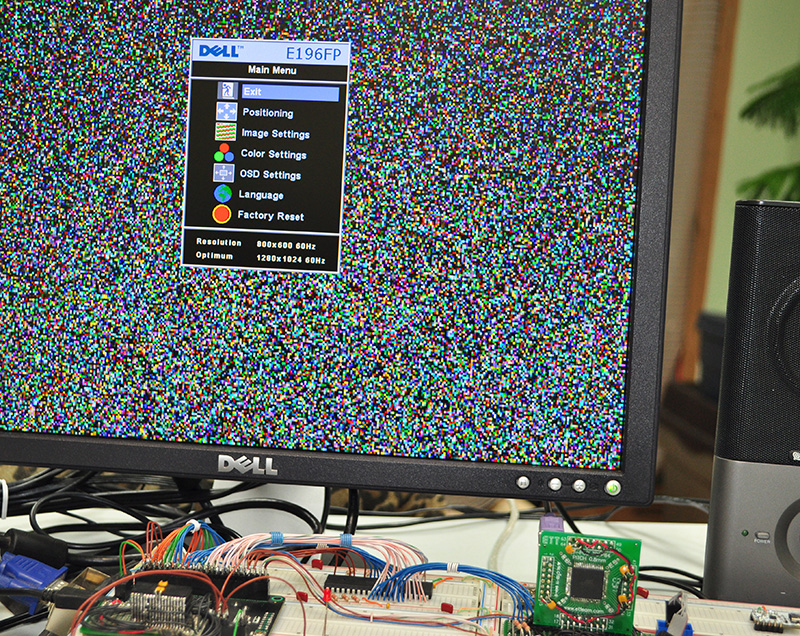

Another reason for A65 is so that my addiction to 6502 assembly programming can become portable. I do have other 6502 based projects on the go, but lately I have not had the time to sit relax in my basement lab and work on them. Since A65 will be about half the size of a C64, and simply plug into any standard VGA Monitor, Keyboard and Speaker System, I can move it around and use when I have some spare time.

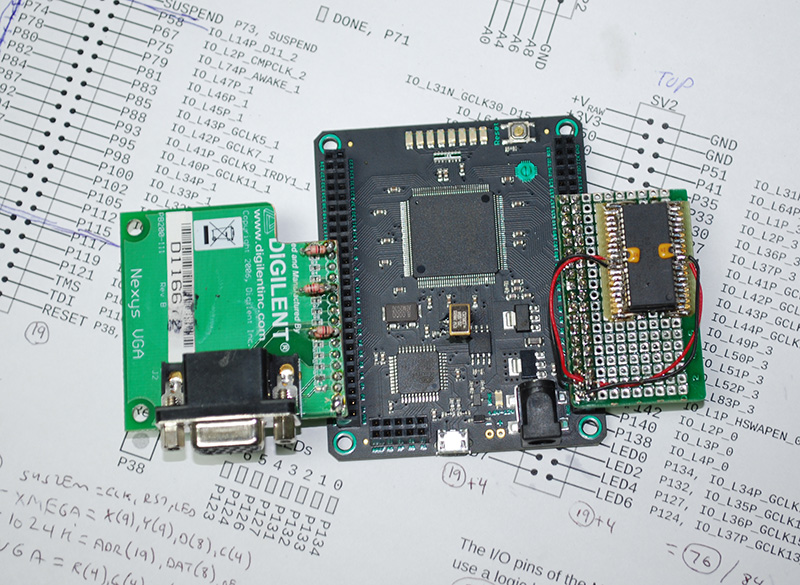

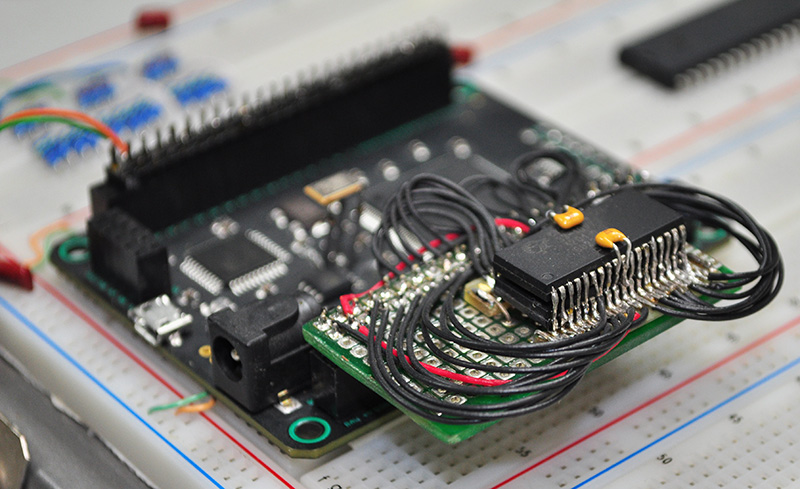

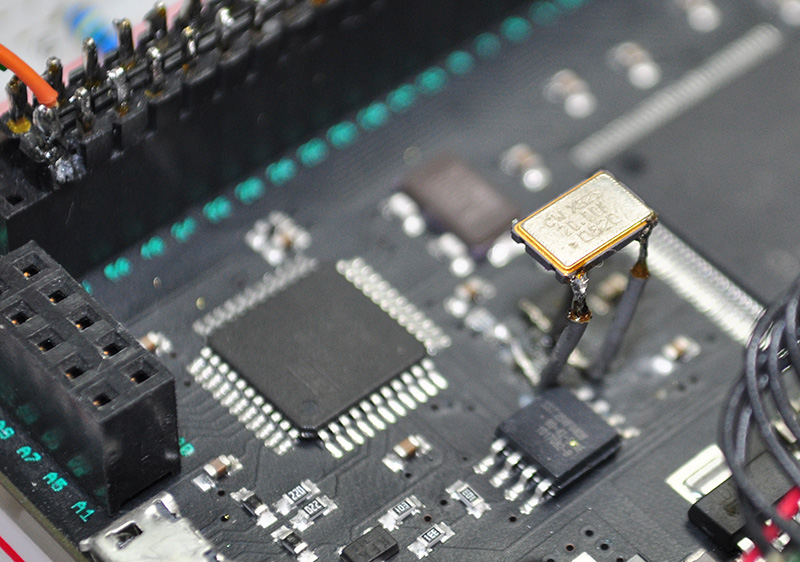

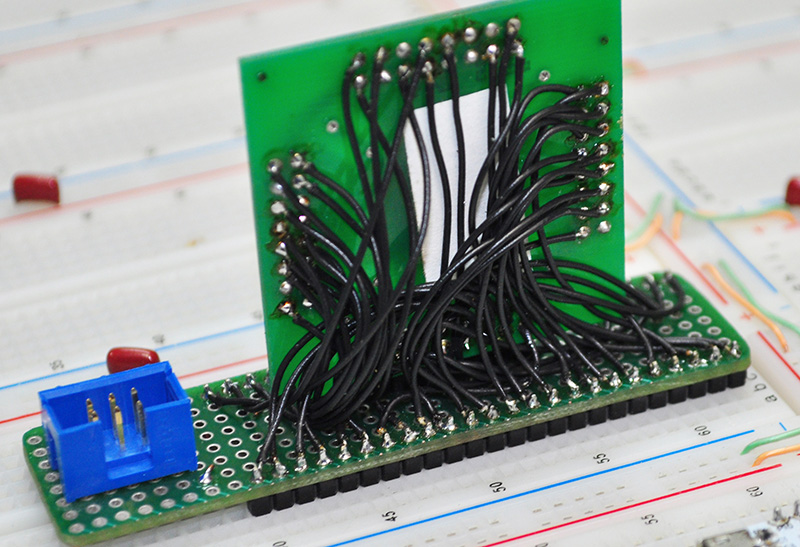

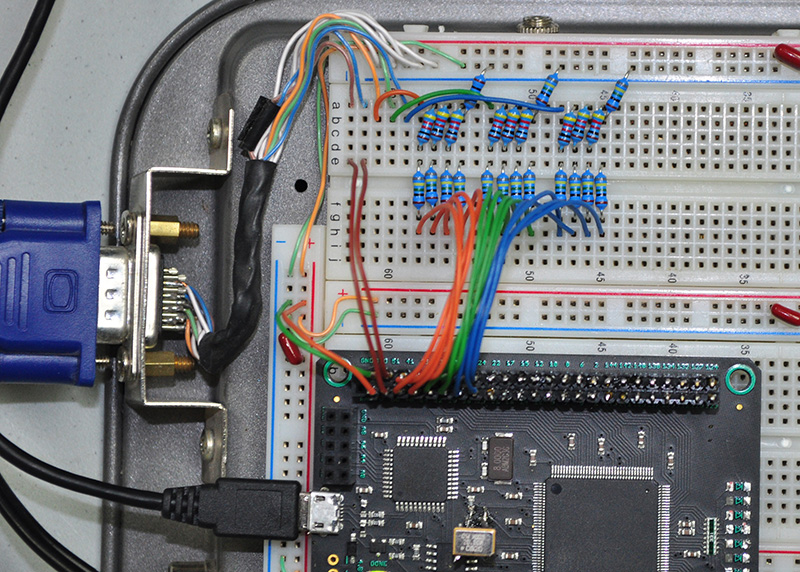

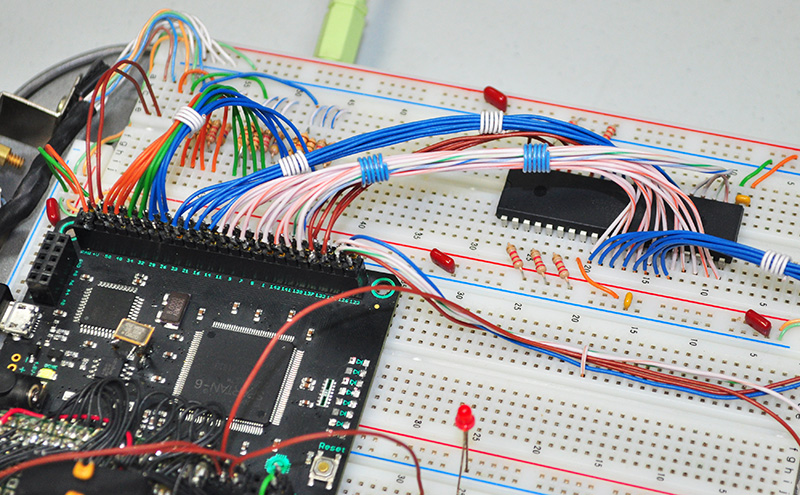

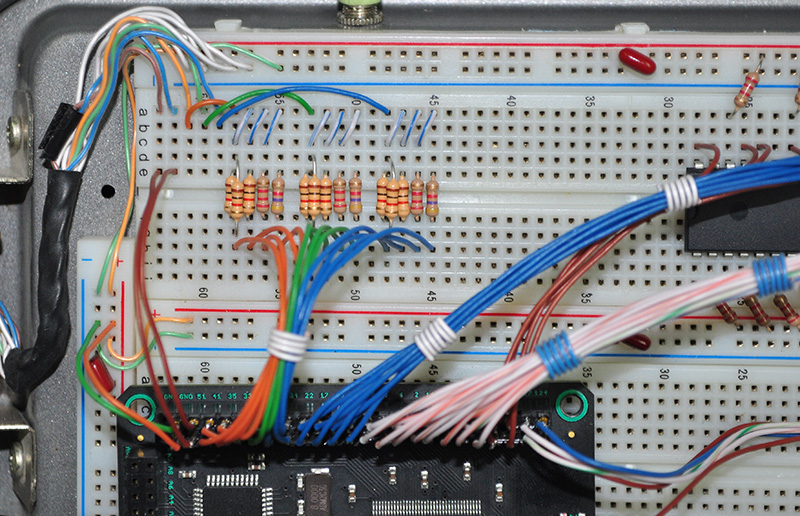

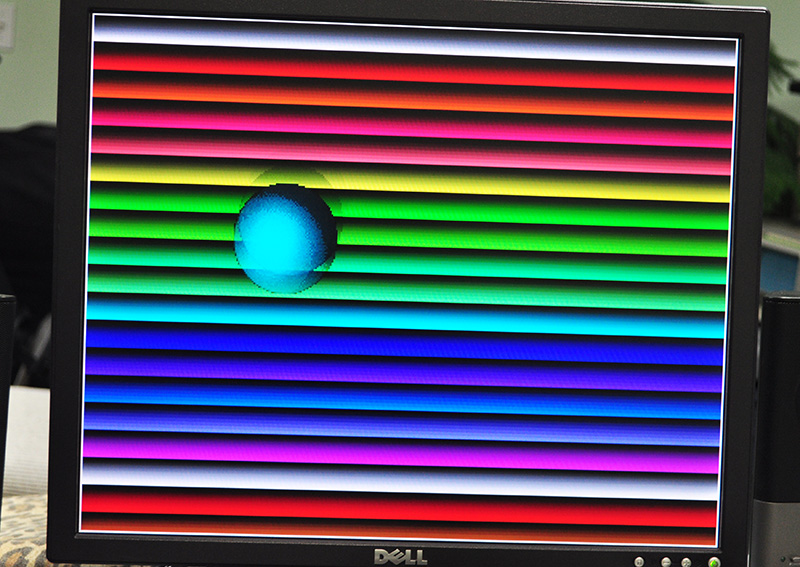

This project is all about the 6502 and its assembly language. It is not about the supporting hardware that makes up what I call the “Chipset”. The Chipset will be whatever modern FPGA fits my design, which gives the 6502 some basic Graphics, Sound, and IO functionality.

So here are my “Must Have” Design Goals…

Code: Select all

1) The CPU will be a REAL 6502 in DIP Format.

2) The system will boot with a functional Operating System.

3) No reliance on modern equipment for coding.

4) The OS will include an IDE and Assembler.

5) Access to at least 4MB of Multimedia SRAM.

6) Instant toggle between OS and assembled / running code.

7) Decent Graphics and Sound built into the Chipset.

8) Custom file system to use any mass storage device.

9) Standard Monitor and Keyboard support.

10) No ROMs. OS and Fonts sent to SRAM at boot.

11) Small form factor case with 6502 behind backlit window.

No reliance on modern equipment for coding means that all assembly will be entered, assembled, and run directly by A65. The OS will boot directly into the IDE, and allow assembling of the source code to another 64K segment in the 4MB address space. The OS segment will be protected from any access by the running program. All SRAM above the running program segment will be accessible by making function calls to the chipset. The running program can rewrite its own codespace, which will allow it to read code from extended memory and write it into the executable erea. This will allow the 6502 to essentially run a program of any size up to 4MB.

Right after an "Assemble and Execute" command is given by the OS, the chipset will grab the contents of Zero Page and store it internally until the OS is returned. A "Return to OS" command will be a keyboard hot key (ESC + F1). This way, the IDE can retain its state for things such as current source code scroll position, IDE settings, etc. Since the OS segment is protected from access by the running program, you can crash and burn all you like, and still return instantly to the OS, and then repair your code. This is what I consider old-school debugging ... just fix it and run it again until it works, man!

Source code will be stored as words in the remaining ~3MB of SRAM Data Space. The words will represent a color value and a character code. This will allow for approximately 32,000 lines of code to be worked on, each line having 64 characters of any color. I chose 64 characters since my VGA generator puts out a screen of 66x35 characters onto the 400x300 resolution display.

The 4MB of SRAM is to be divided into the following segments…

Code: Select all

Video Buffer A : 0,000,000 (120K Protected)

Video Buffer B : 0,120,000 (120K Protected)

6502 Operating : 0,240,000 (64K Protected)

6502 Executable Program : 0,305,536 (64K Full Access)

Working Memory : 0,371,072 (up to 4 MB Total Memory)

Code: Select all

Video : VGA at 400 x 300 resolution with 256 colors from palette of 4096

Sound : 4 Independent 8 bit channels mixed down to 2 stereo channels

GPU : Transparent aware blitter and basic drawing functions

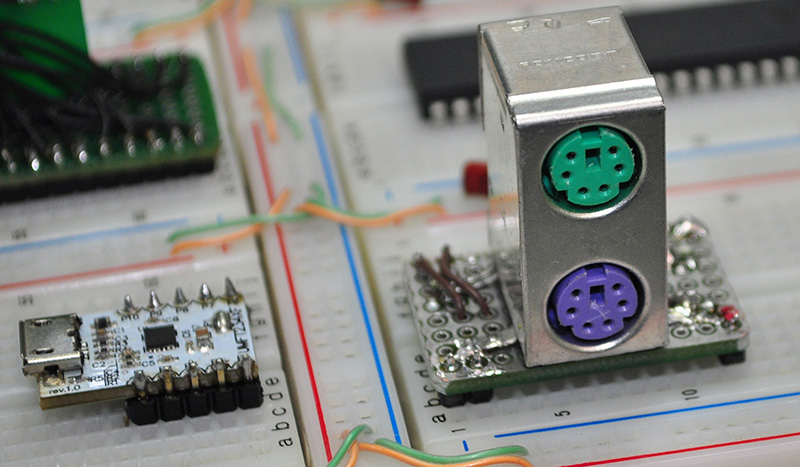

IO : PS2 keyboard, SD card slot, VGA port, audio port, USB (serial) port

The goal is to do all code development right on the unit. I will also include some basic drawing programs and coding tools, which can be loaded as separate programs. A completed program will be stored on the external mass storage device, which at this point will probably be an SD card. I have detailed a file system that will allow the OS to include simple Load, Save and Delete commands.

In the case where I may want to “import” sound or graphics data from my PC into A65 for a demo or game, the onboard USB port can be used to stream bytes from the PC into A65. The USB port will be a simple FTDI USB to serial converter, and I will make a basic export program for the PC. This does not break my “no outside reliance” rule too badly, as it is only to import sound and graphics that have been converted. A65 will have the task of then saving these to the SD card using its own file system. There will be no ability to use the SD Card on a PC beside to backup images of SD cards for safe keeping.

The final cabinet will be around 10 inches wide by 6 inches deep, and have a sloped front as to show off the 6502 behind an LED backlit clear window. The color of the LED backlight will correspond to the mode of operation, such as OS running, Assembling, or Program Executing.

Ok, so there are my basic design goals and reasons for creating Anvil-6502.

Let the fun begin!

Cheers,

Radical Brad... never afraid to Hit The Bare Metal!