Yay... progress.

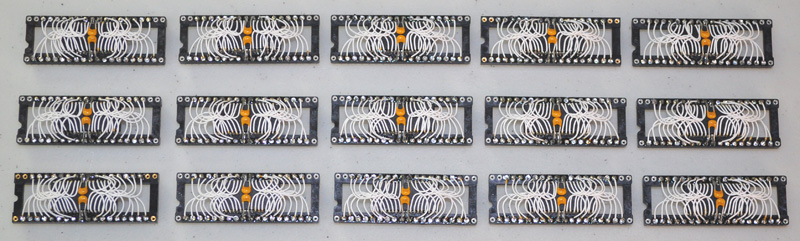

I now have 5 SRAMs completed, and hope to get at least 10 more today.

At that point, I can start on the new design and just work on the rest of the SRAM when time presents.

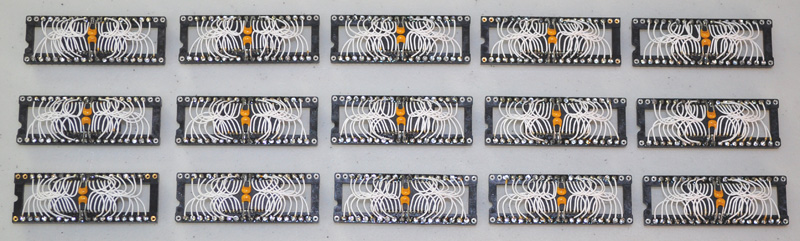

Here is what my day is going to look like...

36 pins x 25 SRAMs = 900 Wires!

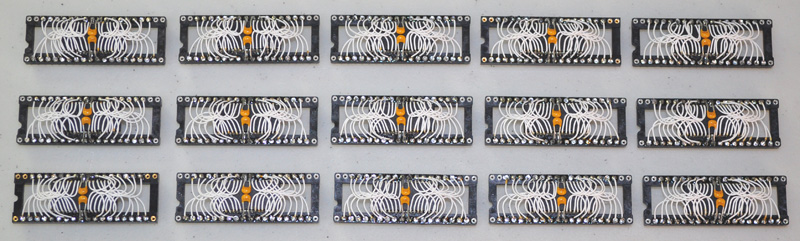

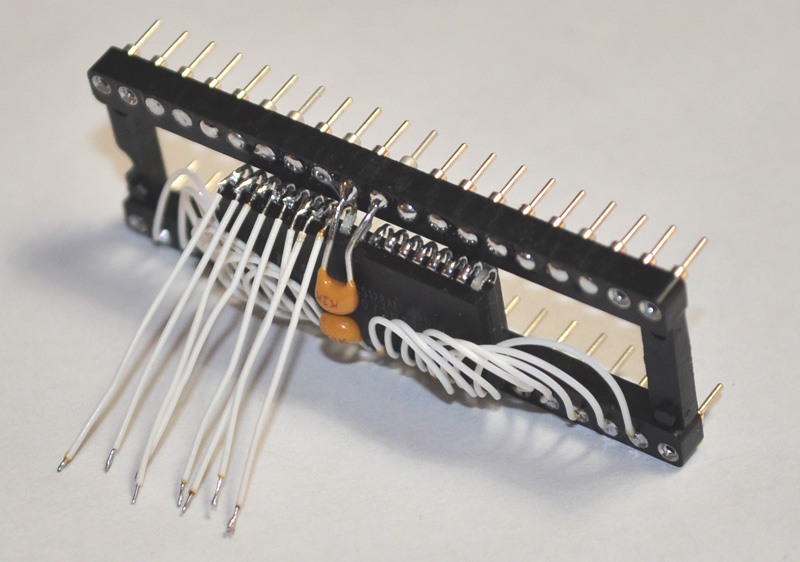

After chopping all the wires using a jack knife on a cutting board, I then stripped the ends.

I did this by rolling the wire carefully under the blade if the knife, and them pulled off the insulation.

The exposed wire is then soldered slightly at each end, one at a time.

Wires can then be soldered to the pins.

I do this in rows on each side of VCC and ground like so...

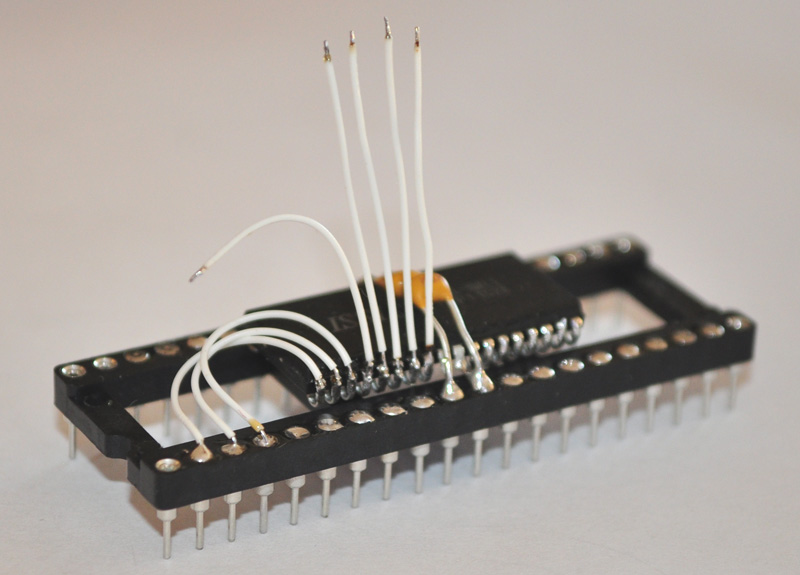

Solder to the SRAM, and then bend the wires to the socket.

Now the other side...

Switch sides, and then repeat.

And the final result...

One breadboard ready 10ns 512k SRAM.

Vulcan-74 will require 25 of these SRAMs now...

Code: Select all

2 x 512K : Video Buffer One (492K x 12 Bits)

2 x 512K : Video Buffer Two (492K x 12 Bits)

1 x 512K : Sync Memory (32,768 Bytes)

16 x 512K : Graphics Memory (4MB x 15 Bits)

4 x 512K : Sound Memory (2MB x 8 Bits)

Ok, I am off to the SRAM factory to burn some solder.

Later,

Radical Brad