...

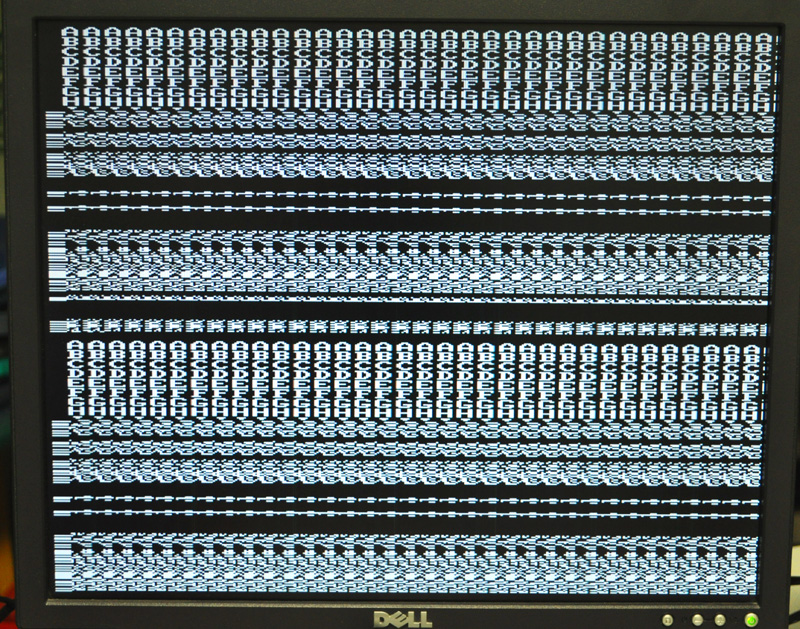

Yes, video needs to be at least capable of a text that is readable on the screen!

Allowing for a microcontroller/... seems a bit... odd to me...

Sound: feeding an appropriate adress line into a speaker generating a fixed square wave would be it?

Code: Select all

ld r17,X+ ;2

ldi ZL,lo8(CHARS) ;1

ldi ZH,hi8(CHARS) ;1

mul r18,r17 ;2

add ZL,r0 ;1

adc ZH,r1 ;1

add ZL,r19 ;1

clr r0 ;1

adc ZH,r0 ;1

elpm r17,Z ;3

sts UDR1,r17 ;2

Code: Select all

; init pointers to character data in RAM and then do this code:

LDI XH, 0x00

ldi xl, (0<<RXEN1)|(1<<TXEN1)

sts udr1, xh ; 2 send 0x00 to SPI, (USART is disabled)

sts UCSR1B, xl ; 2 USART is enabled

sts udr1, xh ; 2 send 0x00 to SPI (USART is enabled)

lpm xl, Z ; 3 nop

lpm xl, Z ; 3 nop

lpm xl, Z ; 3 nop

lpm xl, Z ; 3 nop

lpm xl, Z ; 3 nop

movw xl, acc ; 1

lds acch, mnumbytes ; 2

BUILDSCREEN: ; repeat this 40 times

lds acc, ucsr1a ; 2 read SPI status

ld acc, X+ ; 2 move curr chr in ZL

sts udr1, acc ; 2 send to SPI

lpm xl, Z ; 3 nop

lpm xl, Z ; 3 nop

nop ; 1

dec acch ; 1

brne BUILDSCREEN ; 2/1

ldi xl, 0x00 ; 1

sts udr1, xl ; 2 (only 12 clocks, because tx is buffered)

sts UCSR1B, xl ; 2 disable USART

end: