Just wanted to drop in and throw out some greetings to the 6502 crowd!

Since my free time is sparse during the summer months, I have not had much time to work on my 6502 project, but today I gave myself a break from the homestead and did some hacking.

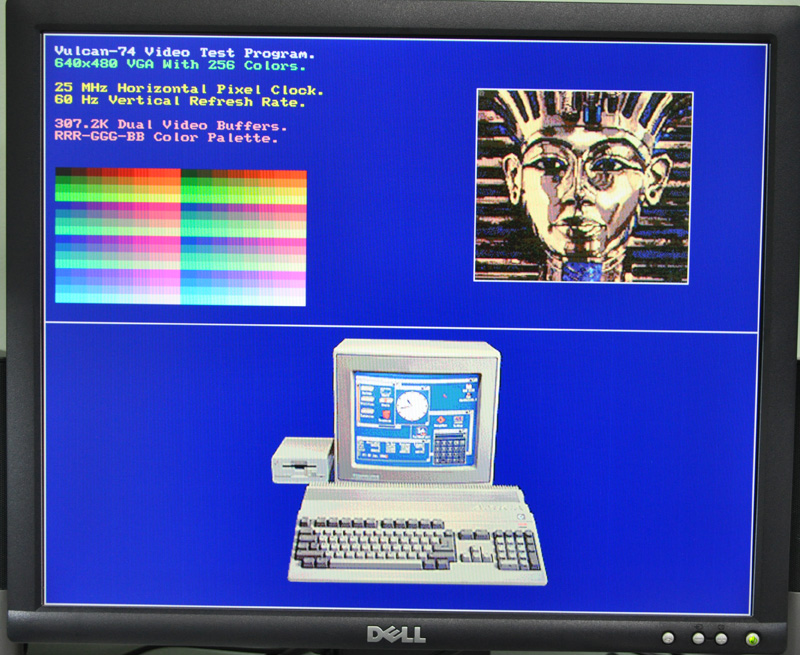

Today, I decided to revive the Video Game version of Vulcan-74, but made it "portable" so I could work on it when I am away for work on road trips.

Yeah, since I am often stuck for a day or two in some remote hotel, I wanted a project that would fit into a shoebox.

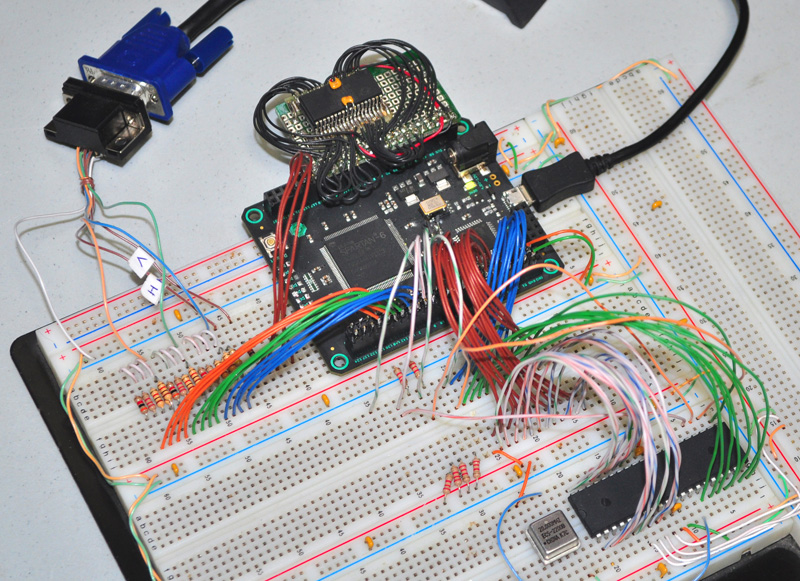

So the plan was to hack together an FPGA emulator version of the giant breadboard, and I managed to do it one one day!

Now this is cool since I am somewhat new to Verilog, but it does prove that knowing the hardware makes one into a better HDL coder.

The target is a Spartn-6 FPGA, and the "donor" board was once a Mojo-FPGA Board. I say donor because I hacked it all to hell.

I needed a meg of SRAM, so I dead-bugged a pair of 512K SRAMs to the board, and then replaced the oscillator with a 20MHz clock.

The FPGA is clocked at 40MHz, and does some real trickery when it comes to sharing the SRAM with 6502, Video, Sound, and GPU.

The 6502 thinks it is just connected to a super fast 64K SRAM, and the FPGA does all the boot load stuffing and IO magic.

I am also working on some SD Card code to load everything on startup, but for now it is all done via SB cable.

The FPGA version actually has more power than the breadboard version, since it is easy to add features in code.

Some of the extra features include...

- 4096 color programmable palette that can display 256 colors at once.

- Single cycle 32 bit math accessible by the 6502.

- Graphics functions such as line, box, circle, fill, and text (C64 Font) built in.

- Sprite rotations for every 90 degrees, including mirror image.

- Horizontal and Vertical image sheering for ultra fast Wolfenstien-like ray trace games.

- Built in math stuff like Sin, Cos, Collision Detection, etc.

- Polygon fill routine.

I also plan to emulate my unfinished Sound Engine, which will be like an 8 channel Amiga.

This quick hack turned out so well that I decided to give it an official title...

"Fusion-6502".

It's basically a chipset for a real 6502! Sound graphics and IO from a single FPGA.

Ok, here is the obligatory eye candy....

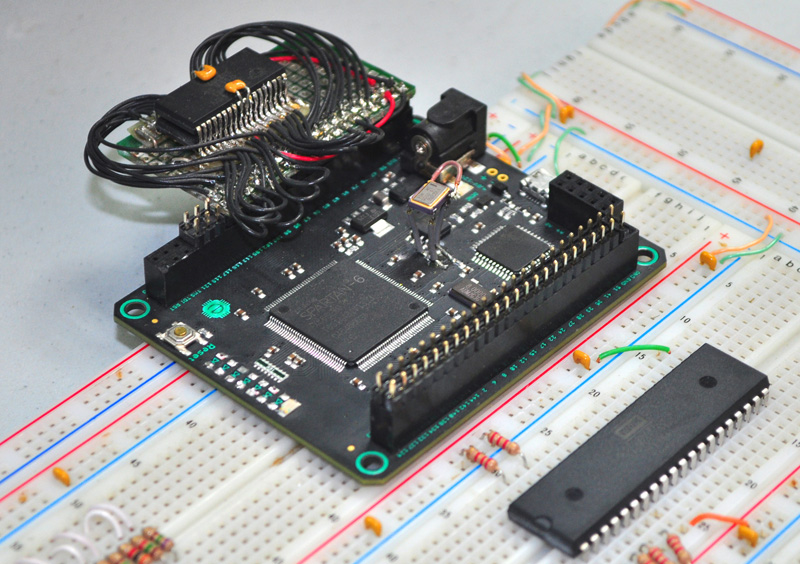

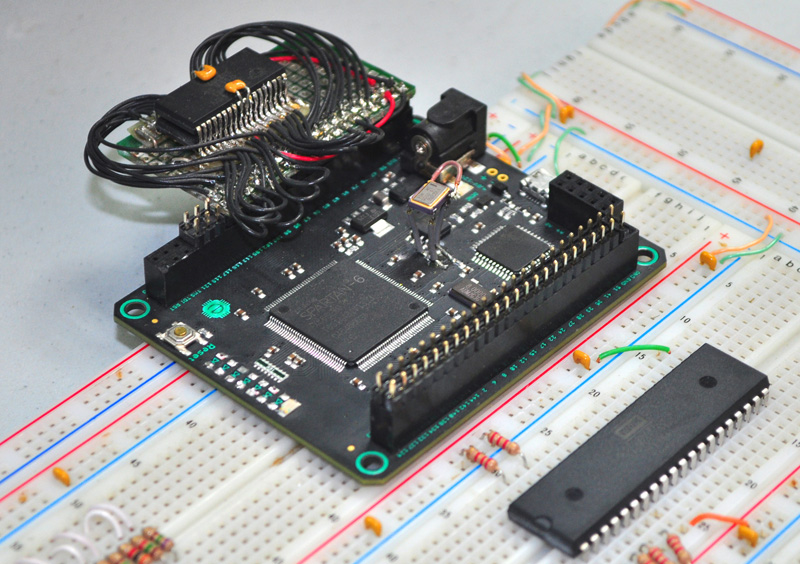

This was once a MOJO Fpga board.

This was once a MOJO Fpga board.

To gain the required 98 IO pins, I desoldered all of the onboard LEDs and made a new IO map.

I also ripped up the oscillator and added a new 20MHz version.

This is doubled internally by the PLL to meet the 40MHz timing for 800x600 VGA.

A pair of 512K 10ns SRAMs added.

A pair of 512K 10ns SRAMs added.

Everything is shared by the 1 meg of onboard memory, arbitrated by the FPGA.

Zero page and IO live internally in code, but everything else is in SRAM.

Graphics Data, Sound Data, 6502 Code, and dual Video Buffers all take tuns!

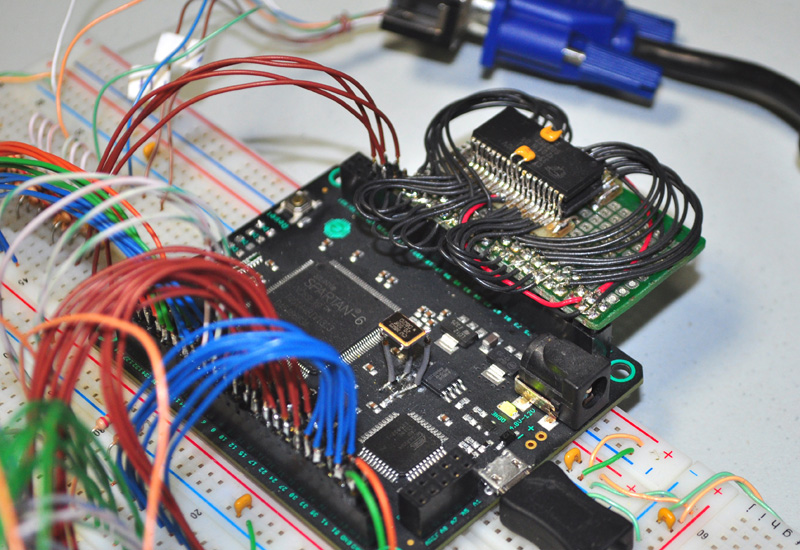

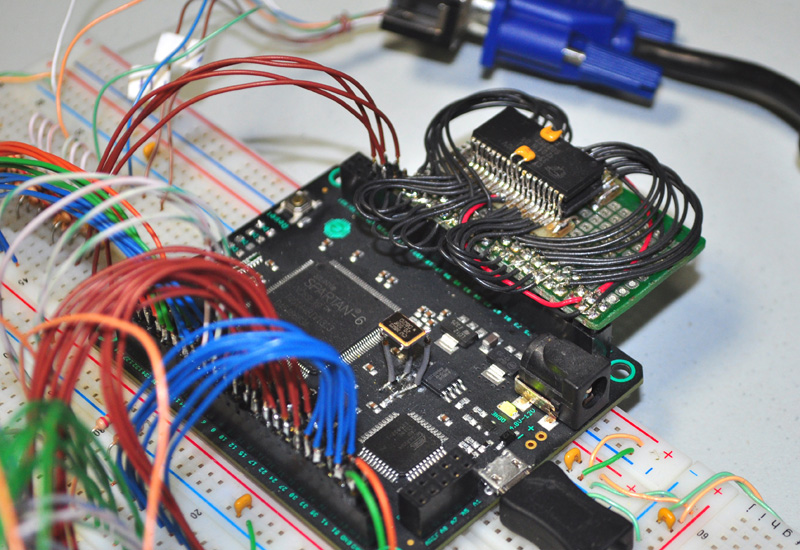

6502 and Video DAC

6502 and Video DAC

The 6502 has no idea that it is connected to an FPGA!

I have tested the 6502 up to 8MHz, which is the "legal" top speed for 3.3v operation.

As you can see by the resulting videos, this is plenty fast to womp an Amiga for graphics power!

The Video DAC is 12 bits, for a total of 4096 colors. Only 256 are displayed at once.

To allow for more color control, the palette is fully programmable on the fly.

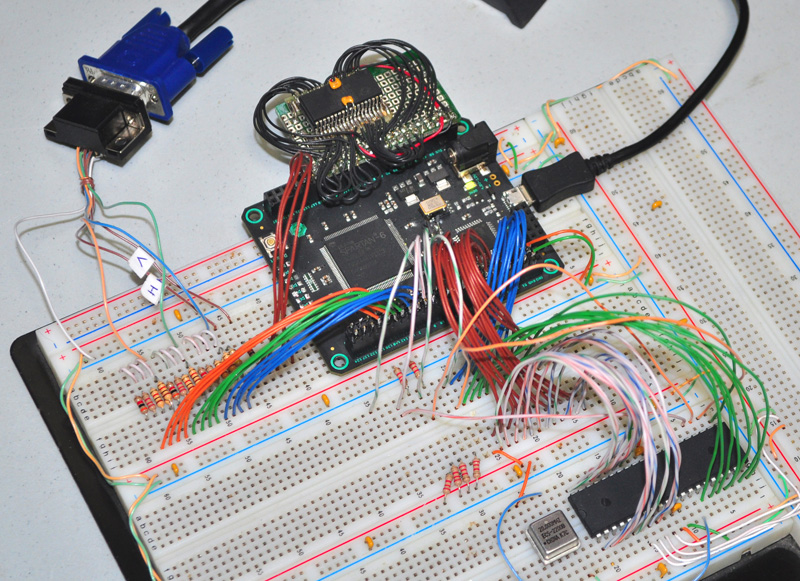

It's those damn checker balls again!!

It's those damn checker balls again!!

Yeah, what can I say... I like watching those checker balls fly around the screen!

This time they are multi-colored thanks to the abilty to rotate the color palette on the fly.

I only have to store one 32 color ball sequence, and can rotate the dark panels 16 times.

These ar 80x80 sprites with 256 color depth, and one invisible "alpha" color.

Fusion-6502 can hurl over 30 of these around the screen at 60 frames per second!

For comparison "Boing" on the Amiga only did one ball, and it was only color cycled.

I started this project at 8:00am this morning, but did not complete the Sound System yet.

Not too bad for a day's work, and I will complete the Sound System on the next free rainy day!

Here is a video of it working...

https://youtu.be/CNVghL233FI

Anyone interested in a board for this project? It's a great platform to test 6502 assembly on!

I would probably provide it with everything minus the 65C02, which would drop into a DIP socket.

OK, back to my farm until the next rain or snow day.

Thanks again for this website!

Cheers,

Radical Brad