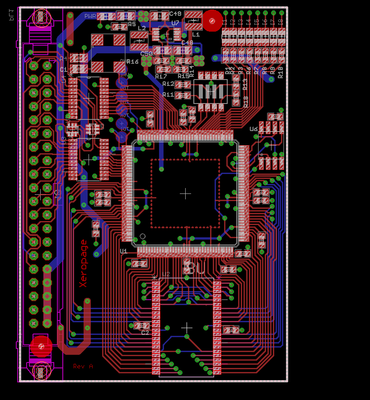

The board is designed for use as a second processor to a BBC micro, but that means it has a byte wide memory mapped interface (at 5V) which should be suitable for any 8 bit host. Indeed, with different code the 40-pin connector could be rejigged to provide, for example, a serial connection instead.

Might be of interest to anyone to sign up for a second production run, or good as inspiration.

Of course, the 32-bit wide memory interface with 2 Mbyte of memory looks interesting from a 65Org24 or 65Org32 perspective. Or even a good old 65Org16!

See these threads:

http://stardot.org.uk/forums/viewtopic.php?f=3&t=9994 (Index/Signposts thread)

http://stardot.org.uk/forums/viewtopic.php?f=8&t=8932 (Order thread)

http://stardot.org.uk/forums/viewtopic. ... 780#p98780 (Tech thread)

Presently three types of CPU core are supported and tested (implemented in the FPGA):

"Matchbox sized 6502 / Z80 / 6809 Co Pro"

and there's interest in a PDP-11 core too.

It's only recently come to life, so no reports of very fast clock speeds yet.