Whoa! Alot of comment since my last post. I have been trying hard to do my homework before I come and post "silly-reflections" and speculations. I will read your postings (since 12/4) and respond.

I have reached a few new conclusions. I think I need a multilayer board. I don't want to "farm out the work" as that is "cheating"; I was thinking maybe I could make my own multilayer board (but couldn't find a source for pre-peg; and, anyway, not sure I have the oven to get it "cooked" properly).

So I thought, maybe, two double sided boards with a "peg board" (unclad) between them. Inward facing boards could be power and ground planes, and the pegboard separates those two. Total stack would be 1/16" *3 = approx. 5 mm. The DIP pins should extend through that (though I didn't check the schematics yet). The boards could be held together by , say, five nuts and bolts; the copper around each nut and bolt should be etched, so no contact is made with the circuits.

Maybe you fellas know of some kind of glue, for inbetween the boards? I dunno, just a thought. I am going to proceed with a four-layer design and a two-layer design.

I'll be using PhotoEZ sheets for the silkscreen pattern; but I see some stuff on the internet for laser print/toner transfer techniques. Maybe I'll try that someday, but I know PhotoEZ works (its just a bit expensive, I think).

Also, VIAs; I was reading Garth's primer and saw that his decoding scheme allowed for about ten of them. The decoding circuit that I presently have is wholly inappropriate. I leave 16KB (Kilo-locations) for I/O. Is there any GOOD reason to do this?

I am reworking "the plan" as we speak.

Thanks, again. I will read and comment later on the above discussions (also, I am still confusing myself over the "RAM-decode+clock" advice of Garth's; But I will have it worked out very soon (

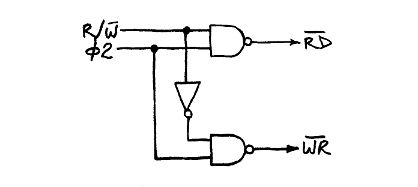

viewtopic.php?f=12&t=3539 ). Timing diagrams, I am sure, are tricky. I just haven't had the "mental fortitude" to tackle it, just yet.

On the plus side, my parts situation is shaping up nicely. All the more reason for me to "finalize" some kind of design.

It would be awesome if I could work the Kodak image sensor project into the 6502 project. Still studying I2C and 65C22 to get a handle on how this REALLY works.

Any advice on running 65816 and 6522 at 3.3V, so that the Kodak sensor device matches (Kodak sensors CANNOT be 5V!). I don't mind buying a new EEPROM and RAM, but I am not sure I could find ones that run at 3.3V?

Maybe 5V computer is what I should stick with, and try to alter the Kodak signal to interface with the 6522? Any tips for that sort of a plan? (I should read all of my posts since joining two months ago; who was it that warned me against "flying a jumbo jet; before piper plane"? Smart person, whoever it was!). Cheers.

(P.S. I watched a youtube video about Nolan Bushnell, Atari founder, yesterday. His original plan was to take a small cheap microcomputer and hook it up to 6, then, 5, then 4 displays, and amortize the cost of the computer, by having kids pump it full of quarters. At 3 video screens the cost made no sense, so he abandoned the project when he couldn't keep up with the I/O. He moved to "hardwired", "many-chip", state-machines, for creating the video arcade market (though pinball already existed, I guess); not full von-Nuemann, because of this. He also mentions an interesting anecdote about "keeping all the NMOS fabs under his employ, to guarantee his near-monopoly on the gaming market". It worked for awhile.)