nonarkitten wrote:

Oh Jeff, surely you're ignoring the rather excellent HCS08 and HCS12 processors from NXP (nee Freescale; Motorola) which can reach speeds of 50MHz with many instructions hitting single cycles (e.g., TAX and INCx). The S12 is so close to the 6809 but so much faster with fractional and extended multiply and divide routines built-in or even weirder instructions like WAV (calculates the weighted average) and TBL (table lookup and interpolate).

At first I had difficulty locating HCS12 doc; but, with that problem solved, I'm starting to get acquainted. It does seem that this family offers some good, Forth-y features!

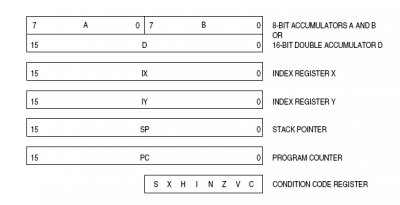

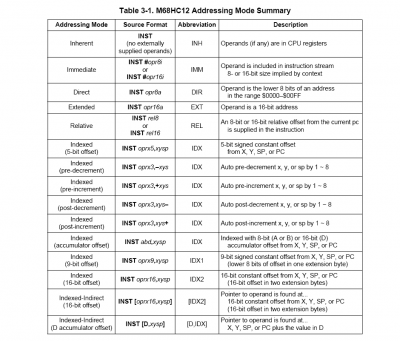

Like the 6809, it's very fluent with stack operations. The Address Modes (below) include pre- and post-increment and pre- and post-decrement modes that let you include a push or pop as part of another operation. On a slightly different topic, it's interesting that, "The CPU12 allows the index register to be incremented or decremented by any integer value in the ranges –8 through –1 or 1 through 8. The value need not be related to the size of the operand for the current instruction."

NXP offers a very wide selection of devices, most featuring a 16-bit data bus, it seems, and some with mapping logic that expands memory beyond 64K. But, as I eventually learned, HCS12 doesn't appear in the part numbers. A

search on Mouser's site for HCS12 returns a bunch of MC9S12 part numbers, for example. There are lots of branches on the family tree, and I've only scratched the surface. The diagrams below came from the

S12CPUV2 Reference Manual. Thanks again, nonarkitten, for the tip.

-- Jeff

Attachment:

programming model.png [ 13.11 KiB | Viewed 5113 times ]

programming model.png [ 13.11 KiB | Viewed 5113 times ]

Attachment:

'HC12 address mode summary.png [ 90.71 KiB | Viewed 5113 times ]

'HC12 address mode summary.png [ 90.71 KiB | Viewed 5113 times ]

_________________

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html