My time has been very limited lately, but last night Vulcan-74 has made another milestone of progress!

The XY half of the GPU is now working perfectly, complete with Alpha Control.

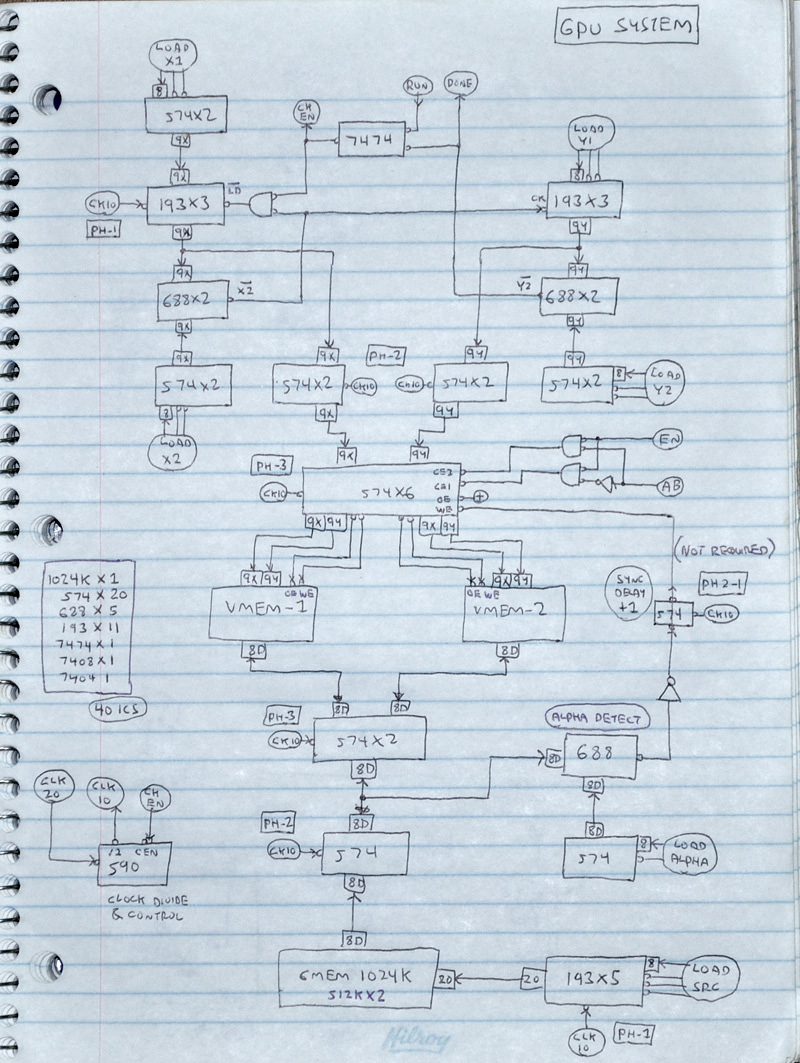

After seeing the failure of the 574 synced version, I tore up 90% of the GPU to start over.

This time, I lowered the clock, but planned for single cycle operation, using a 6502-like dual phase clock, that in my instance will clock our pixel data on the rising edge, and then do alpha detection and writing to memory on the falling edge.

In order to keep this system as efficient as possible, I clocked a 74HC4017 decade counter, to divide the master 20MHz clock by 4. The clock pulse is taken on the 4th count, which also drives the reset. This clock sequence is then inverted, so I get a pulse stream of HI-HI-HI-LO. This works perfectly, since the counter pathway needs a lot more time than the registering of output data and the WE line. If I were to simple use a 50% duty cycle clock instead, then I would have to divide the master clock even more to give the counters more time before the falling edge.

I will explain this in MUCH more detail when I redo this project on my website as a DIY plan.

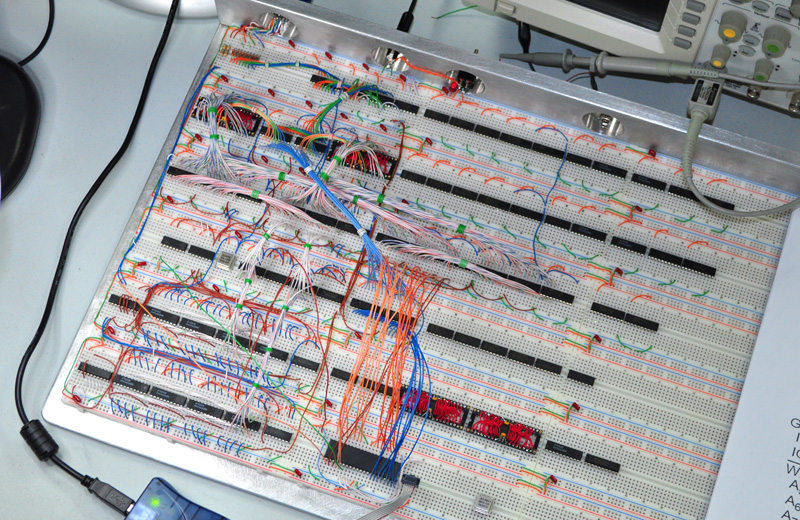

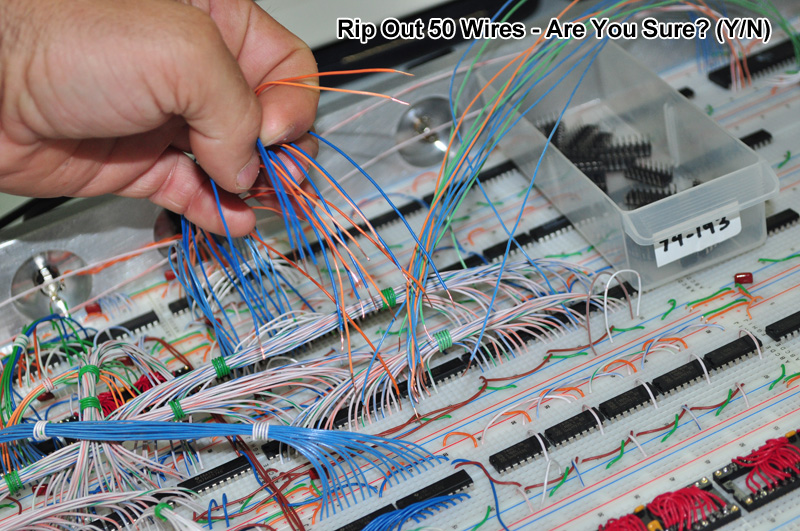

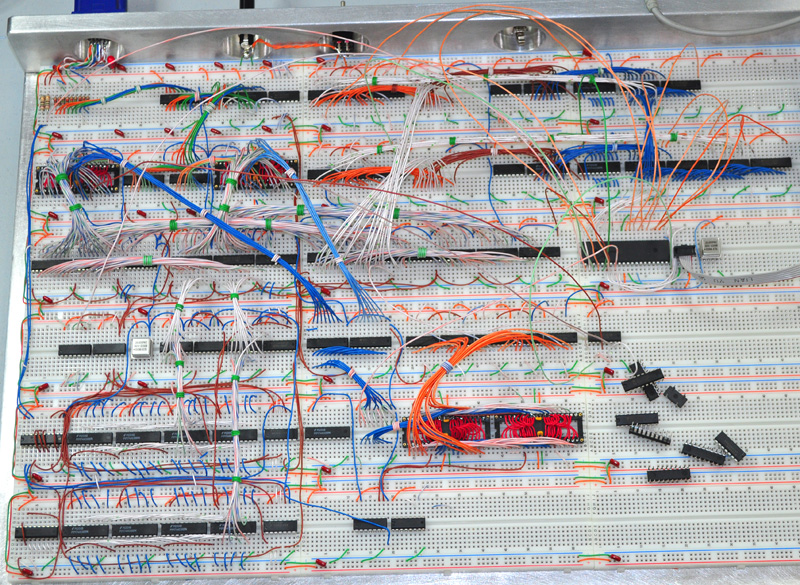

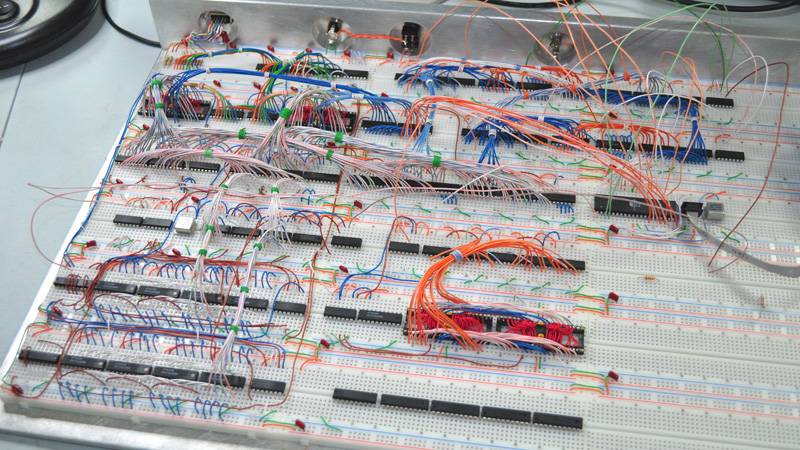

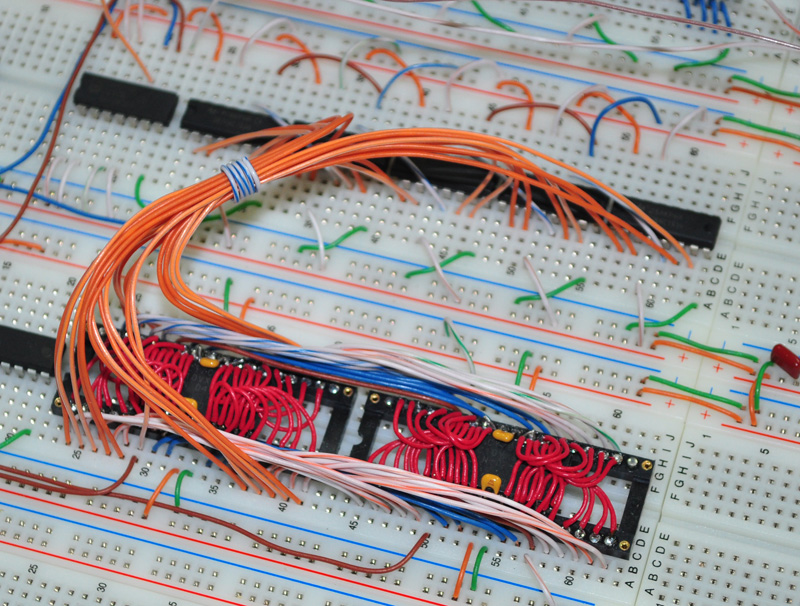

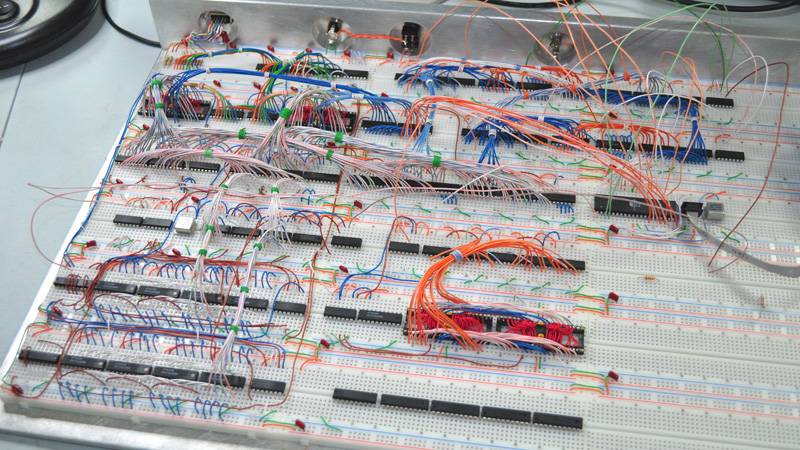

It's a baron waste land of abandoned circuitry!

It's a baron waste land of abandoned circuitry!

I ripped up most of the GPU wires, and took out any 74HC574 that was being used as a "phase" to clock data.

Now each of these GPU signals must reach the destination in a single cycle...

- X Destination Sprite Address (9 bits)

- Y Destination Sprite Address (9 bits)

- Pixel Data Destination (8 bits)

- Pixel Data for Alpha Control (8 bits)

- Alpha Comparator WE Line (1 bit)

- Source Sprite Address (20 bits)

- Pixel Data Source (8 bits)

This required a full redesign of the entire GPU with the exception of the 20 bit Source Counters.

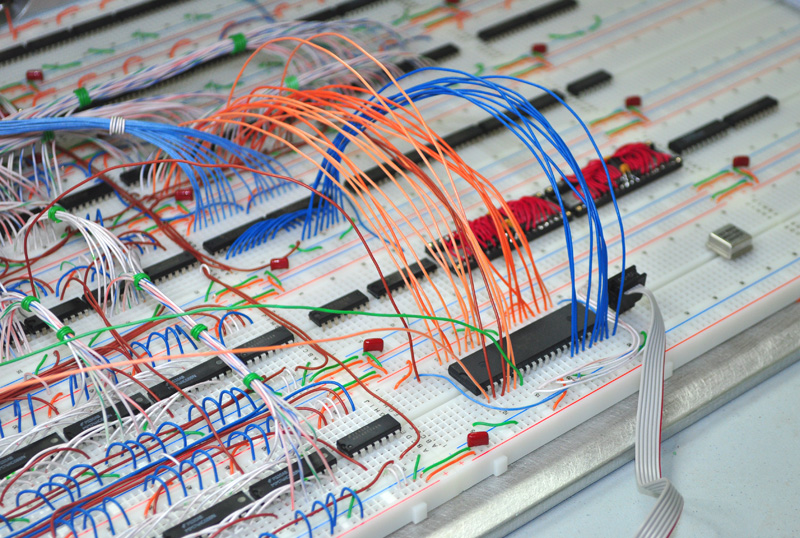

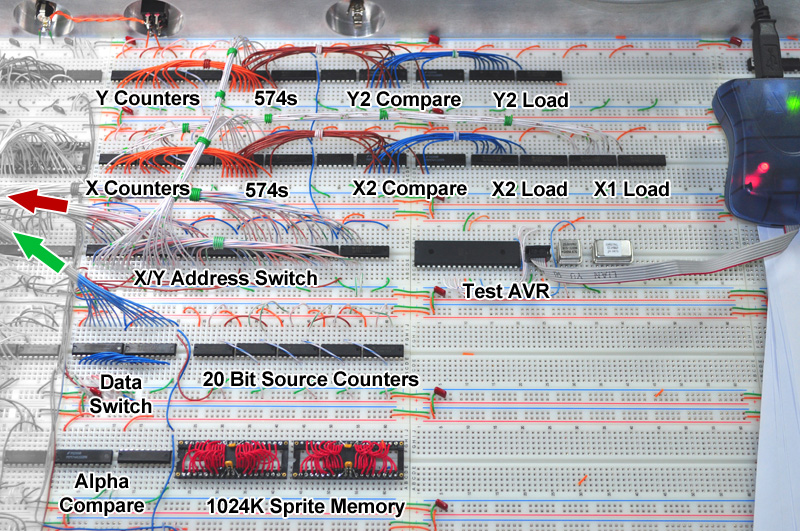

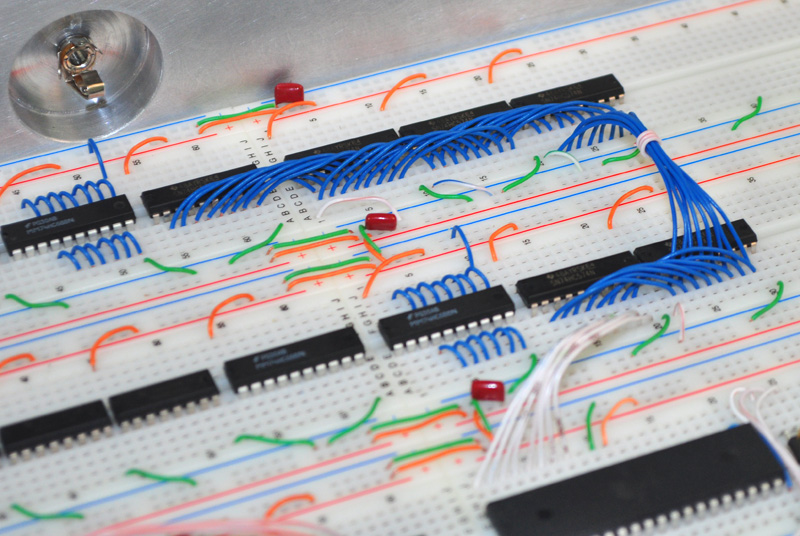

Redoing the XY counter wiring.

Redoing the XY counter wiring.

Any job worth doing is worth doing right, so I plugged in the new ICs and cut proper length wires.

Dude, we got a lot of wires here!

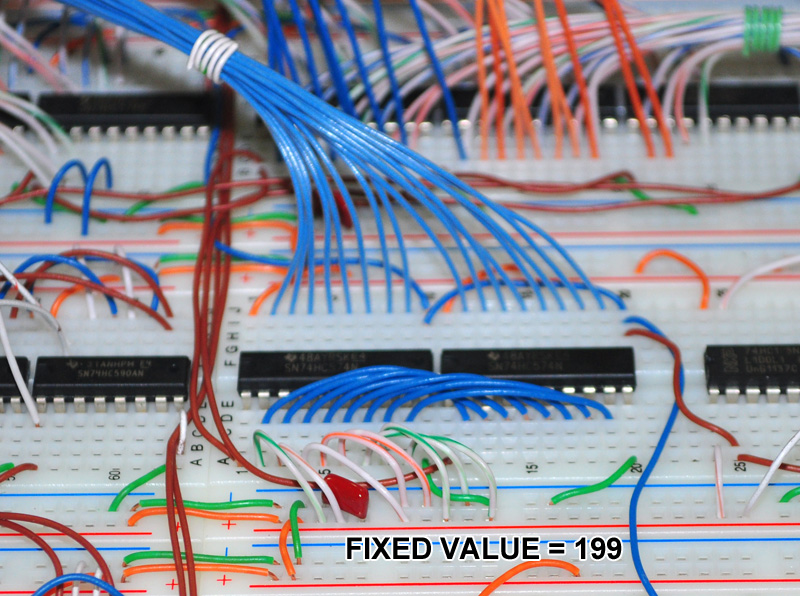

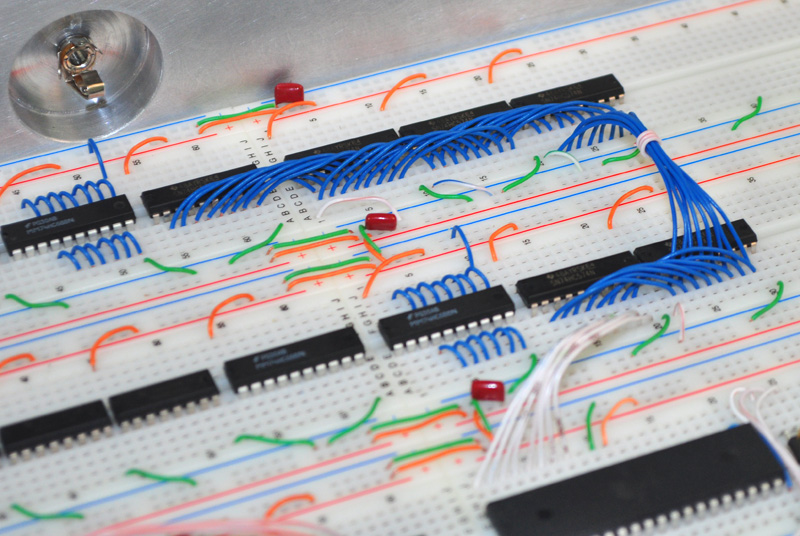

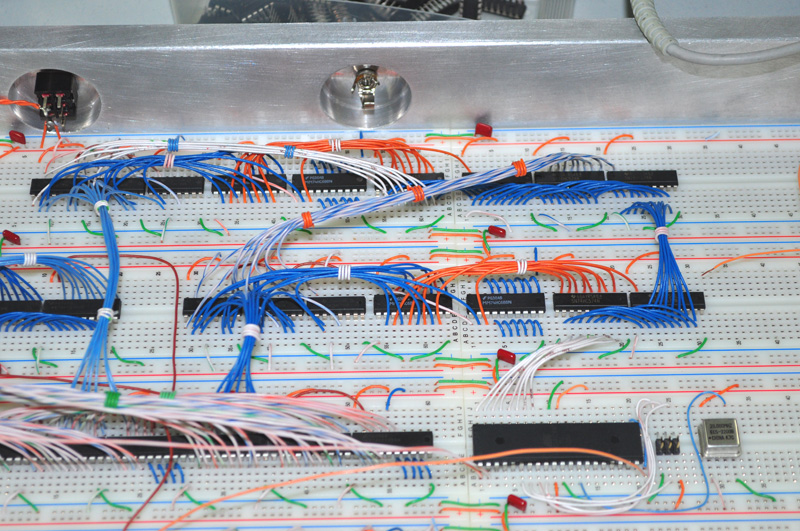

The XY Destination Counter System.

The XY Destination Counter System.

The XY address generation system is much the same as before, using 74HC193 counters and comparators.

The X counter can count from any number between 000 and 399, and the Y counter range is 000 to 299.

The reset of the X counter triggers the Y counter, and the wrap of the Y counter halts the GPU to a "Completed" state.

The 6502 (AVR for now) simply sets the start and end data for the counters and then hits the "Run" line to get them going.

As the GPU does its magic, the 6502 can go on to do other things, and only needs to check that the GPU is done before sending it another command.

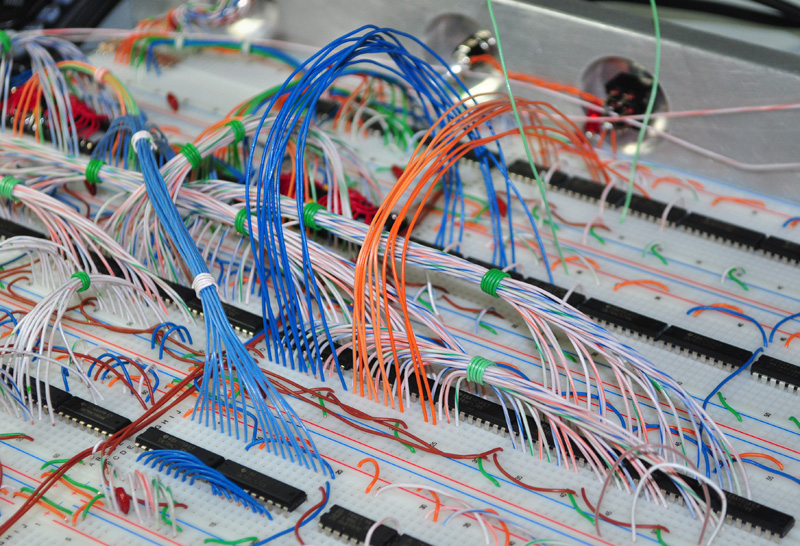

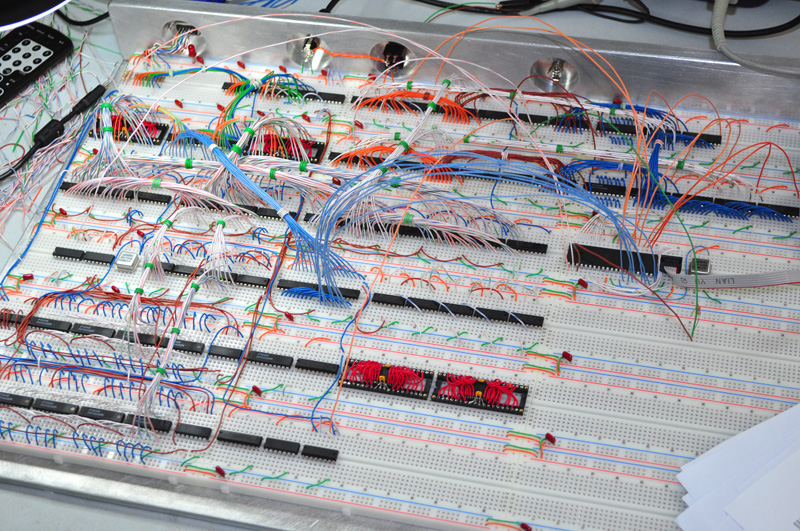

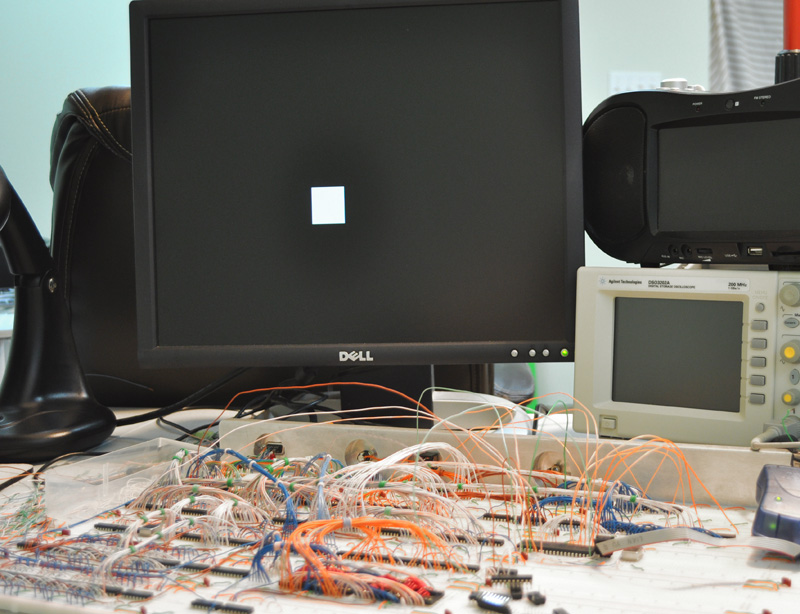

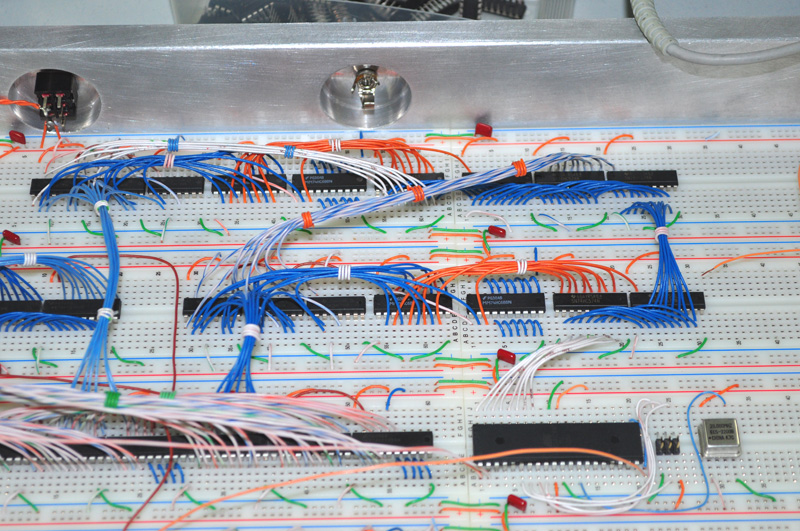

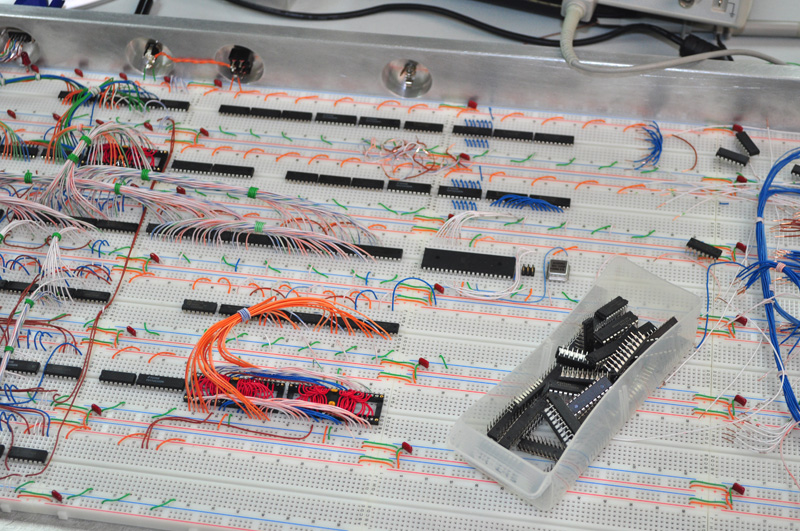

Spaghetti anyone? Temporary wires from the AVR.

Spaghetti anyone? Temporary wires from the AVR.

The rest of this wiring is a dreadful mess, but that's because it's only temporary.

Since the AVR is only acting as a 6502 stuntman for now, the wiring is just tossed in adhoc.

At this point, only the upper half of the GPU is being tested, so all Sprites will appear as solid blocks.

In order to make them look nicer, this time I added a data port from the AVR to set the color of the blank Sprite Data.

The AVR sets the following 8 bit data bytes and then triggers the GPU to execute the command...

- Destination X1.lo Start Address

- Destination X1.hi Start Address

- Destination X2.lo End Address

- Destination X2.hi End Address

- Destination Y1.lo Start Address

- Destination Y1.lo Start Address

- Destination Y2.lo End Address

- Destination Y2.hi End Address

- Destination Block Color (temporary)

- GPU Run Signal

Once the data is set, the AVR sits back and enjoys a Mojito as the GPU logic fires out pixels like hellfire.

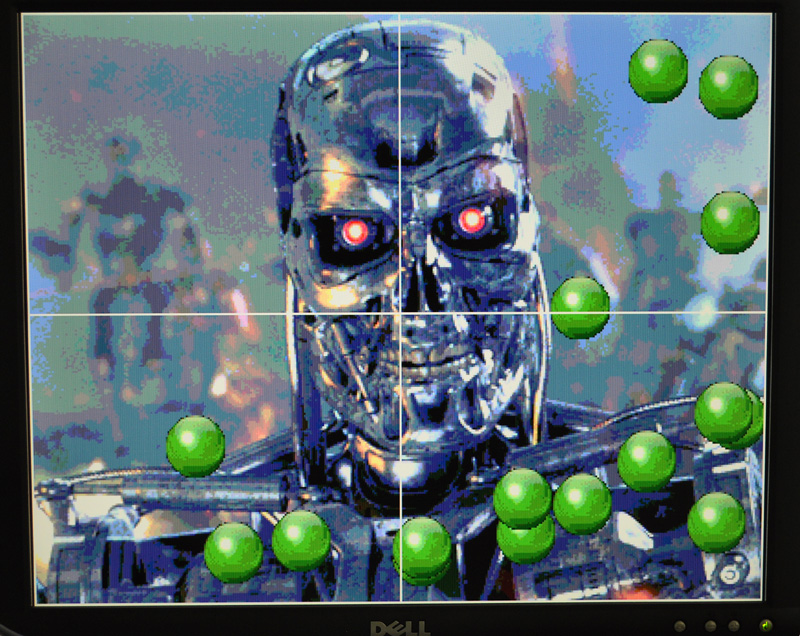

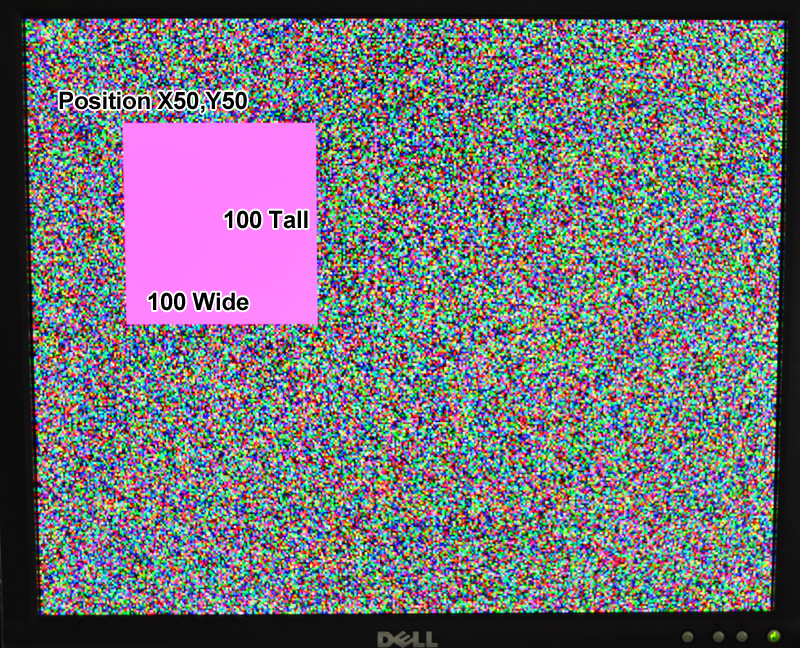

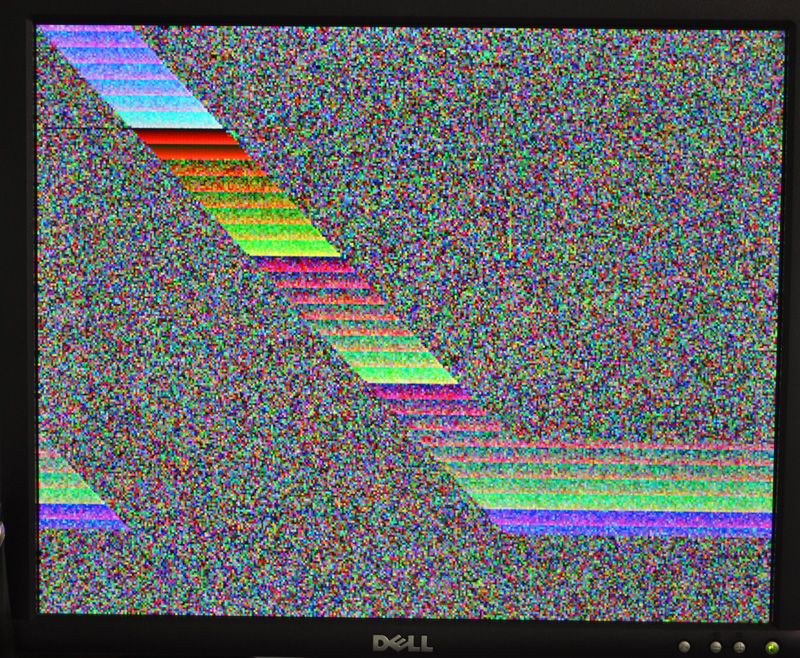

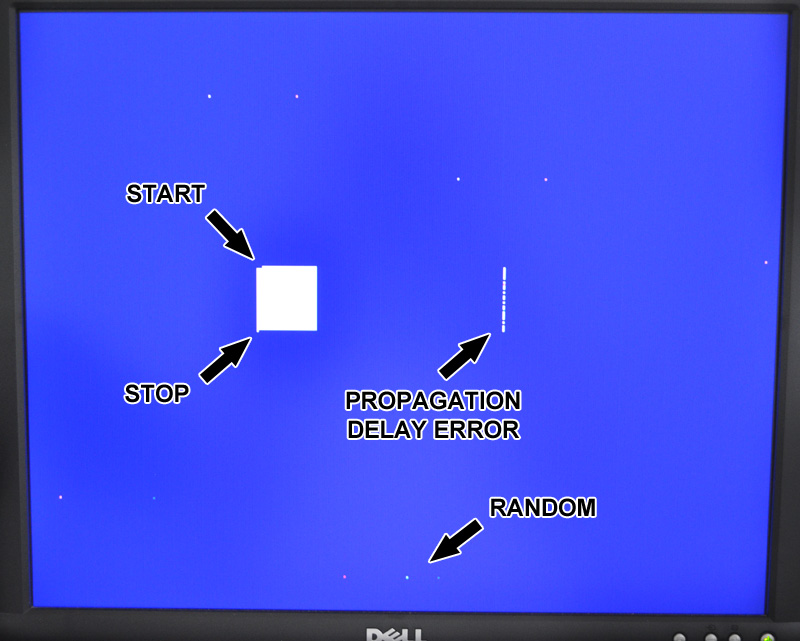

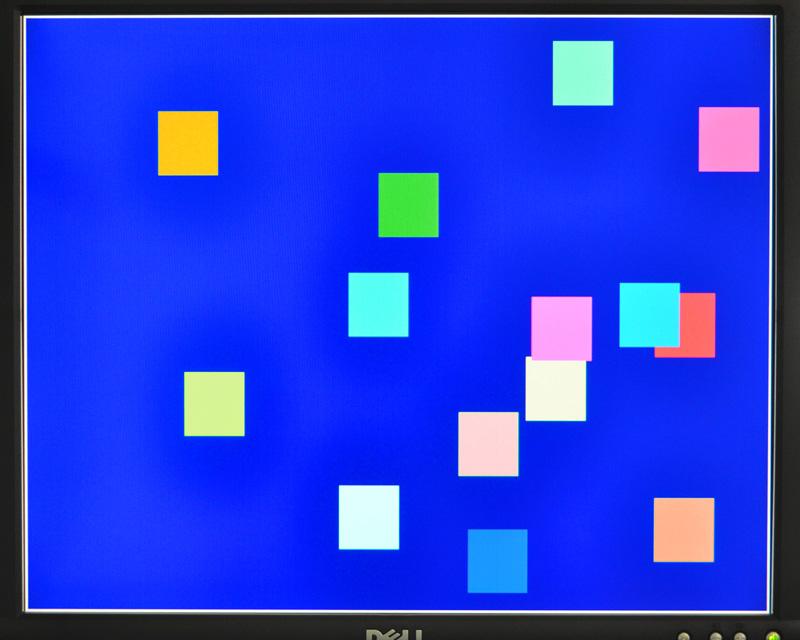

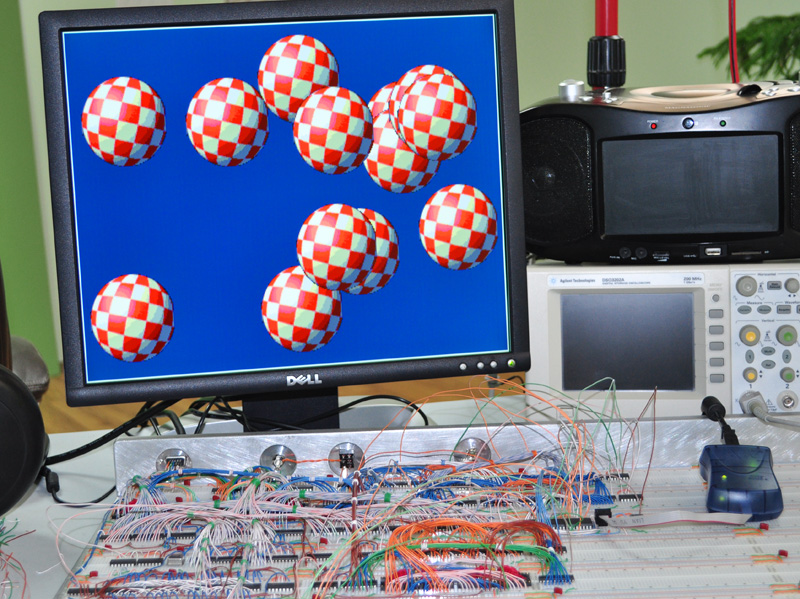

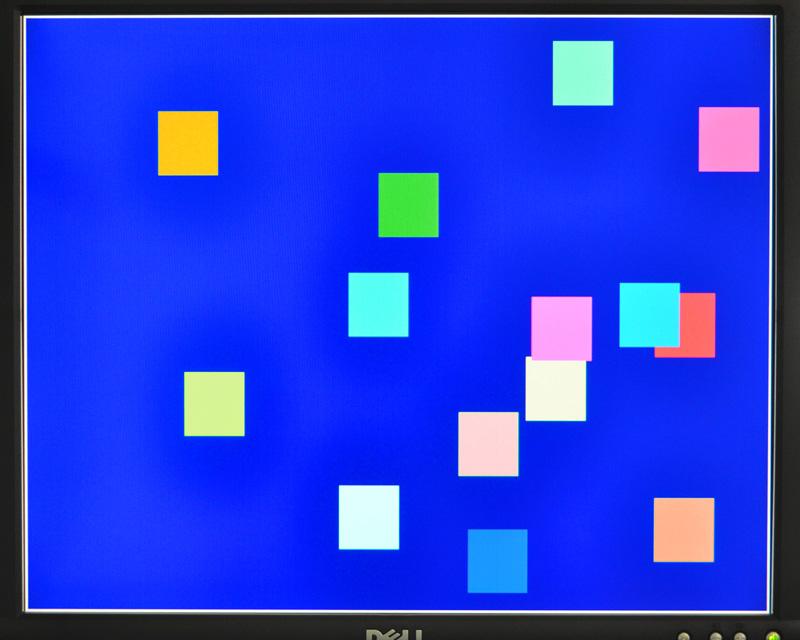

Dummy Sprites generated at 60 FPS by the GPU!

Dummy Sprites generated at 60 FPS by the GPU!

Now, these solid 32x32 blocks may not look that impressive, but this is really a landmark achievement in the GPU design.

Once the Source logic is connected, these Sprites will have 256 colors as well as full transparency using the Alpha Color Control.

Sprites can be any size from 1x1 pixels to 400x300 pixels, and have 255 colors, with one color used as transparency.

Seeing these blocks move around at 60 frames per second glitch free means that the GPU is 100% functional now!!

The GPU is even being used as a temporary "Screen Clear" system by first drawing a 400x300 blue block at location 0,0 on the screen.

From there, the AVR draws 16 randomly bouncing 32x32 Sprites, which at this point only show up as solid blocks.

On a side note, the "Screen Clear System" will be another logic subsystem that simply wipes the entire back buffer to any color.

using 74HC590 counters, I intend to clock this part of the logic to 40MHz. Yes, you read that correctly... 40MHz logic on a breadboard!

The GPU is currently achieving a pixel rate of 5 Million Pixels per Second! Not too bad for a handful of logic chips on breadboard, eh?

Once I verify the operation of the Source half of the GPU, I may try to up the speed to 6.66 MPPS.

Before the GPU was working, the AVR running at 20MHz could manually draw maybe 8 blocks at 60 FPS.

The GPU can easily do 60 or more! The 6502 clocked at 20MHz is going to have similar performance.

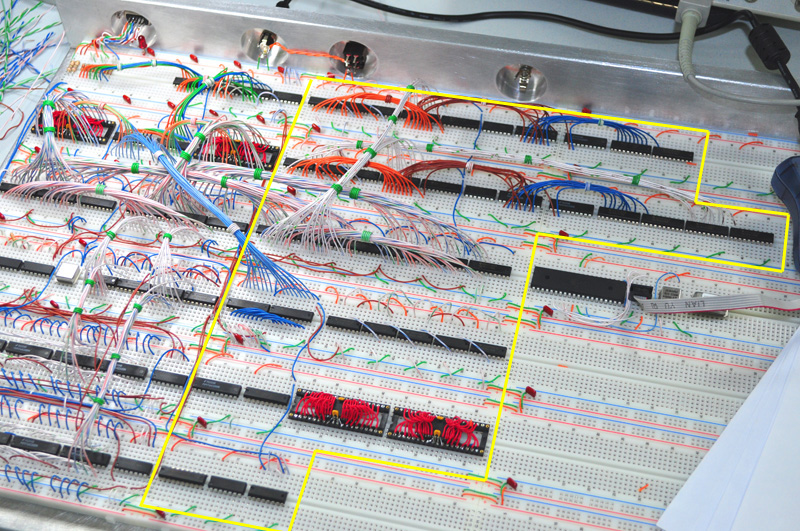

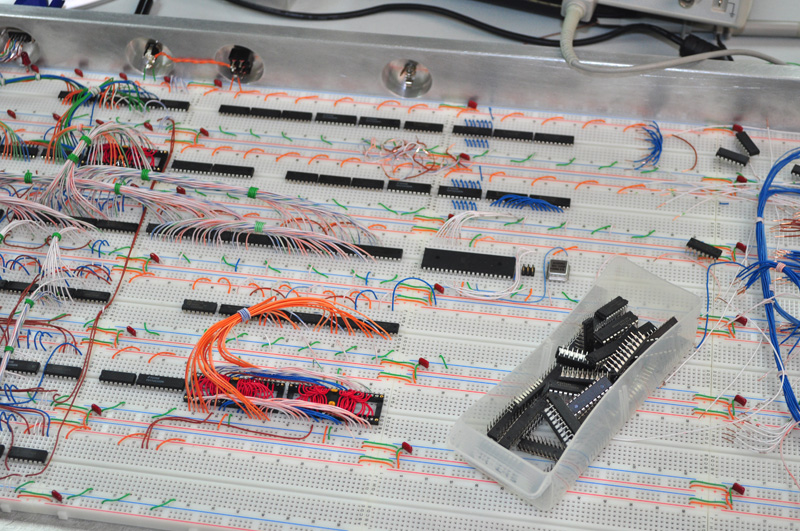

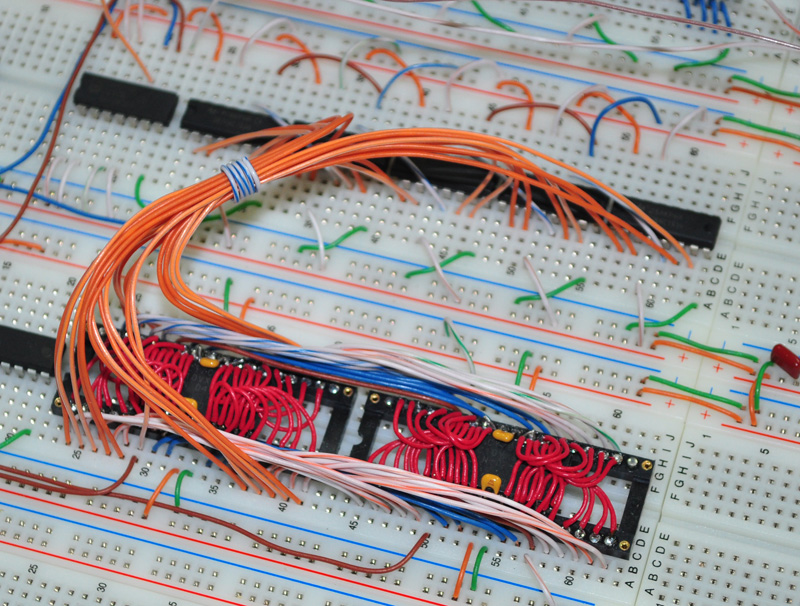

The Source Sprite Memory - next to be connected.

The Source Sprite Memory - next to be connected.

Now that the GPU has been proven, I am hyped to wire up the bottom half and show some real sprites.

I only need to hook up the Source Sprite Memory, which is a 1024k SRAM pair with a 20 bit counter.

Pixel data is streamed our serially to the Alpha Control, in sync with the XY Destination Counter Logic.

For those who are afraid to try a single panel breadboard over 1Mhz, consider this...

I now have half of this Goliath breadboard hooked up, and it is clocked from single 20MHz oscillator.

There are 80 ICs on the board, and several SRAMs that are being accessed at 20Mhz.

VGA is being drawn to an 800x600 screen at 60Hz, and it is 100% standard exact.

When completed, I will have 24 breadboards tied together running over 150 ICs.

One part of this circuit will be clocked at 40MHz.

If all goes well, the next set of images will have real sprites with transparency moving around the screen.

I have videos as well, but it takes days to upload from my Off-grid, Redneck, Boondocks satellite internet, so maybe later!

Cheers,

Radical Brad