-- Jeff

How do we handle the loss of 5V CPLDs?

Re: How do we handle the loss of 5V CPLDs?

BigEd wrote:

Well, it does make them supply-voltage compatible, but as you have to drop the supply voltage you will lose clock speed - unless you have suitable level conversion in place.

cr1901 wrote:

Million-dollar question: How much propagation delay do these level shifters add?

-- Jeff

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

Re: How do we handle the loss of 5V CPLDs?

GARTHWILSON wrote:

I expect it has to do with the fact that the WDC parts can run down to 1.2V, unlike 74HCTxx which is 5V only.

- BigDumbDinosaur

- Posts: 9425

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

Re: How do we handle the loss of 5V CPLDs?

scotws wrote:

GARTHWILSON wrote:

I expect it has to do with the fact that the WDC parts can run down to 1.2V, unlike 74HCTxx which is 5V only.

x86? We ain't got no x86. We don't NEED no stinking x86!

Re: How do we handle the loss of 5V CPLDs?

scotws wrote:

shouldn't we be looking at how to move our designs to 3.3V instead of hanging on to 5V?

BigDumbDinosaur wrote:

as you reduce the voltage, the maximum rate at which CMOS devices can be run is likewise reduced.

It's unfortunate, because there are some lovely, high-capacity RAMs on the market nowadays, and it'd be feasible to fully populate all 16 megabytes of an 65c816 system!

-- Jeff

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

Re: How do we handle the loss of 5V CPLDs?

According to what I'm reading from a commentator over on another forum, 5V parts aren't going away.. the selection is increasing, including new 5V ARM processors. Apparently this has to do with e.g. the automotive industry, or noisy environments etc.

Re: How do we handle the loss of 5V CPLDs?

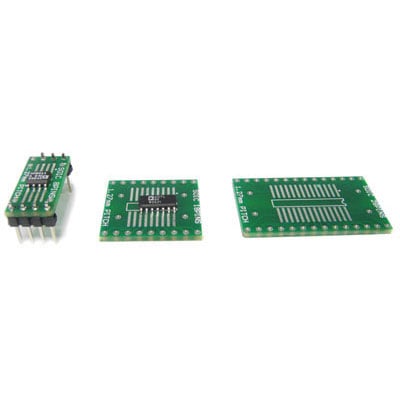

74cb3t3384 seems only to come in SMD  .

.

- GARTHWILSON

- Forum Moderator

- Posts: 8773

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Re: How do we handle the loss of 5V CPLDs?

banedon wrote:

74cb3t3384 seems only to come in SMD  .

.

http://www.jameco.com/webapp/wcs/stores ... 2130263_-1 :

or http://www.jameco.com/webapp/wcs/stores ... =CAT151PDF :

6502.org wrote:

Image no longer available: http://www.jameco.com/Jameco/Products/M ... 178195.jpg

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

Re: How do we handle the loss of 5V CPLDs?

Thanks Garths. I thought there was some sort of trade off in maximum speed if you use one of these? I.e. one of the reasons for doing wirewrap is to get direct straight connections, but the extra traces on the card inhibit this?

- GARTHWILSON

- Forum Moderator

- Posts: 8773

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Re: How do we handle the loss of 5V CPLDs?

True, it's not quite ideal, but the inductance of the connections from the WW pins to the IC's die would not be much different from what it would be using a DIP leadframe plugged into the same socket. Getting a custom board made, with power and ground planes, and soldering SMT parts down to it with no socket, would be better for high-speed performance.

I still find it hard to believe that whoever chose the pinout of 74xx ICs decades ago with the power and ground pins at the corners instead of the middle of each side couldn't look ahead far enough to realize that parts were going to get faster and faster, and that keeping the inductance of the power and ground connections down would become paramount! So bone-headed!

I still find it hard to believe that whoever chose the pinout of 74xx ICs decades ago with the power and ground pins at the corners instead of the middle of each side couldn't look ahead far enough to realize that parts were going to get faster and faster, and that keeping the inductance of the power and ground connections down would become paramount! So bone-headed!

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

Re: How do we handle the loss of 5V CPLDs?

BigDumbDinosaur wrote:

Also, as you reduce the voltage, the maximum rate at which CMOS devices can be run is likewise reduced.

a) http://web.inter.nl.net/users/J.Kortink ... /index.htm

b) http://web.inter.nl.net/users/J.Kortink ... /index.htm

Both use a 14 MHz rated W65C02, although a) can also employ a W65C816. a) is a DIP, runs at 5V, and up to 20 MHz (with 20 ns SRAM). b) is a QFP, runs at 3V3, and up to 24 MHz. Maybe not an exactly 1:1 comparison, but nevertheless there is no indication that at 3V3 the W65C02 suffers from limited clock speed.

- BigDumbDinosaur

- Posts: 9425

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

Re: How do we handle the loss of 5V CPLDs?

Windfall wrote:

BigDumbDinosaur wrote:

Also, as you reduce the voltage, the maximum rate at which CMOS devices can be run is likewise reduced.

a) http://web.inter.nl.net/users/J.Kortink ... /index.htm

b) http://web.inter.nl.net/users/J.Kortink ... /index.htm

Both use a 14 MHz rated W65C02, although a) can also employ a W65C816. a) is a DIP, runs at 5V, and up to 20 MHz (with 20 ns SRAM). b) is a QFP, runs at 3V3, and up to 24 MHz. Maybe not an exactly 1:1 comparison, but nevertheless there is no indication that at 3V3 the W65C02 suffers from limited clock speed.

x86? We ain't got no x86. We don't NEED no stinking x86!

Re: How do we handle the loss of 5V CPLDs?

What John might be seeing is that a QFP is a better package than a DIP for a high speed design. I agree, the physics of CMOS make it slower with reduced voltage - of course, in a complete system there's more going on than the CMOS logic gates in the CPU.

Re: How do we handle the loss of 5V CPLDs?

GARTHWILSON wrote:

I still find it hard to believe that whoever chose the pinout of 74xx ICs decades ago with the power and ground pins at the corners instead of the middle of each side couldn't look ahead far enough to realize that parts were going to get faster and faster, and that keeping the inductance of the power and ground connections down would become paramount! So bone-headed!

BigDumbDinosaur wrote:

The W65C02S has been conservatively rated

Good point about the package, Ed. And John, what was the RAM speed in system (b)?

-- Jeff

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

Re: How do we handle the loss of 5V CPLDs?

Dr Jefyll wrote:

But (remarking on John's post) when the doc says 5V operation surpasses 3V operation, we expect that comparison to be valid, on the presumption that any conservatism applies equally to both.

Dr Jefyll wrote:

Good point about the package, Ed. And John, what was the RAM speed in system (b)?

Re: How do we handle the loss of 5V CPLDs?

Dr Jefyll wrote:

But to clarify for Scot (who's probably wondering), 3.3V chips running on 3.3 volts don't suffer any performance loss. The problem arises when a system with one power supply includes both 3.3V chips and chips (such as WDC micros) which can accept 3V or 5V. It's not permissible to operate the 3 volt chip on 5V, so instead the 5V-capable chip must run on 3.3 volts -- which means it'll fall short of its potential, performance-wise.