Long time no see - welcome back.

Visual6502 is my usual go-to reference, but in almost all cases

Balazs' schematic will have the same circuits.

You're right to be looking for D-type latches - in MOS technology they are normally just a single pass transistor on the input to an inverter. The inverter's input acts as a capacitor, so when the pass gate is off the state of charge is preserved.

If the latch has several multiplexed inputs, there's no need for a separate mux, because a set of pass gates all connecting to the same storage node acts to provide a set of inputs with their respective enables.

If the output of the latch is to be used to drive some simple logic gate, it may be possible to merge the logic gate with the latch: the storage node is now an input to the logic gate. If two logic gates must be fed by the latched output, one possibility is to duplicate the latch function, and have each gate offer a capacitive input as a storage node, another is to use both of the inputs as the storage node.

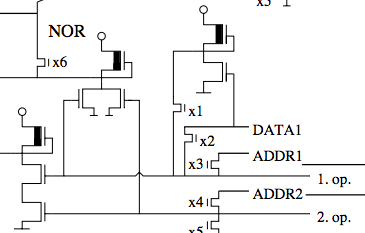

And that's what we see with the A and B inputs to the ALU: two or three inputs come in, go through some pass gates, and connect to the inputs of two logic gates which form the first part of the ALU: there's an inverter to provide optional inversion, and a NAND and a NOR to perform logic operations and to form part of the full adder function.

Attachment:

File comment: Clip from Balazs' schematic: ALU inputs with data flowing right to left.

6502-ALU-inputs.png [ 20.27 KiB | Viewed 1652 times ]

6502-ALU-inputs.png [ 20.27 KiB | Viewed 1652 times ]

Note that Balazs' schematic has the ALU at the top with the output at the left, whereas visual6502 has the ALU at the bottom with the output at the right. Balazs' terms the three input busses DATA1, ADDR1 and ADDR2, whereas visual6502 terms them idb (Internal Data Bus), adl (Address Bus Low) and sb (Special Bus). The five input controls which Balazs' calls x1 through to x5 are called in visual6502 dpc8_nDBADD, dpc9_DBADD, dpc10_ADLADD, dpc11_SBADD and dpc12_0ADD - these names derive from Hanson's naming, which is direct from MOS themselves, via their schematics.

Attachment:

File comment: Visual6502 screenshot of ALU inputs with data flowing left to right

visual6502-ALU-inputs.png [ 70.45 KiB | Viewed 1652 times ]

visual6502-ALU-inputs.png [ 70.45 KiB | Viewed 1652 times ]

I've highlighted the B input here. All of that highlighted area is one node, at the same voltage, but the bulk of the capacitance holding the charge is formed by the two transistor gates over on the right: the polysilicon gates run vertically here, and the upper transistor is the input to a two-input NOR gate while the lower one is an input to a two-input NAND gate. There are three logic gates visible: you see the red pullup area for each one. The one on the left is the optional input inverter.

Hope this helps.

Ed