Thanks for the suggestion -- examples would be good.

Alarm Siren has a

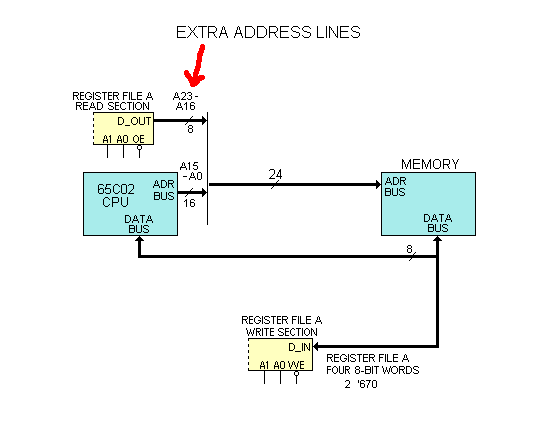

scheme that can illustrate use of a '670, so I've taken the liberty of reproducing and altering his diagram.

At the bottom there's a VIA acting as a 3-bit Bank Register. And it's easy to imagine a

74_573 transparent latch doing basically the same job (as shown in red). Essentially you write the desired Bank number from the data bus to the VIA (or to the '573), and thereafter the bank number gets read out on pins which hardware interprets as the upper address bits when the program accesses the "window" at 8000-BFFF. This is a time-tested approach; solid and familiar territory.

Unfortunately it can be a bottleneck having just one Bank Register. There's save/restore overhead if its use needs to be shared with an Interrupt Service Routine, and even simple

non-interrupt tasks face challenges because having only one window means only one bank can be accessible at a time. For example, it's very awkward to compare strings or other data structures if each resides in a different bank. Also you can't copy directly from one extended Bank to another. Instead you're forced to copy from extended RAM to base RAM then (after altering the Bank Register) copy again to extended RAM in the destination Bank.

The '670 is really just four transparent latches in one package, and that's a big help in keeping the chip count low if you choose to implement two (or even four) Bank Registers to relieve the bottleneck. The '670 read select and write select inputs dictate which latch will be active, and there are different ways you might want to manage those inputs. One option is to simply give the 64K base map

two "windows" into extended RAM. You'd decode the address to determine which window is being referenced, and thereby derive a signal to drive the aforementioned '670 read select input. Write select is somewhat similar but used when you're loading up the '670 registers prior to use. By writing to the '670 you can "aim" one window at one bank and the other window at another. Both windows become immediately accessible, and doing a copy or comparison suddenly becomes a great deal faster. HTH, and let me know please if there's anything important I missed.

Druzyek, I missed your post while typing my own. Nice to see we share that view of a 670 as basically a set of latches.

With my KK Computer I kind of went to town, 670-wise.

It has four bank registers and they're 8 bits wide.

Also there's a drastically different mechanism to control

when the 670's engage. A window scheme uses ordinary 6502 instructions, and the VIA/'573/'670 kicks in

only for cycles during which an access within the designated window results -- that's how we get a cycle-accurate answer to the "when" question. Typically as the instruction concludes there's a transition to the other bank; finally, for one cycle only, there's a data access (read or write) of the other bank. That concludes the instruction and the access to the other bank. It's a fairly simple scheme to implement, but unfortunately the windows are smaller than you might wish because they and the base RAM must all fit within 64K. In fact the total of everything that's immediately accessible never exceeds 64K. In contrast, KK has new instructions, and external microcode that "knows" what the CPU is doing on every cycle. So again we get a cycle-accurate answer to the "when" question, but the cues comes from microcode, not an address decoder waiting for the window to get touched. The need for the window goes out the window!

Now every bank can be a full 64K in size -- and as much as 256K can be made immediately accessible. That's assuming 4 Bank Registers, and you could increase that if your new instruction set can be adapted to accommodate. Another advantage of breaking the window is that 64K chunks are much faster to process than non-64K chunks when the goal is to simulate a "flat" aka linear 16 MB space. Flatness isn't a major concern when it comes to storing code, but if it's

data which your new address space is going to be filled with then flat addressing is a boon, especially for hosting and examining objects bigger than 64K.

The KK Computer is summarized

here, and the block diagram shows the 670's but to clarify here's an edited excerpt. The 670 is drawn in two pieces but it connects in much the same way as in the example above (accepting writes from the data bus and outputting high address bits).

-- Jeff

[multiple edits...]

- KK_block_diagram_excerpt.png (5.5 KiB) Viewed 2293 times