Hi Norby,

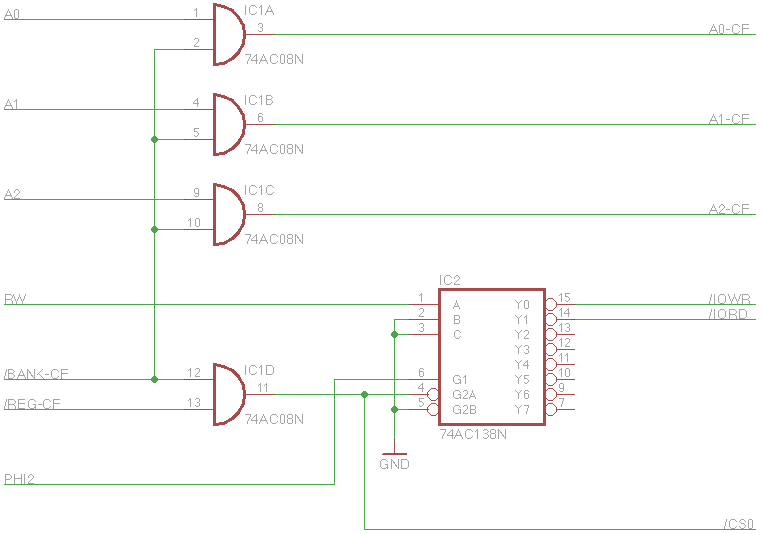

first let me elaborate on the last point. Here a drawing on which I base the explanation

- Fake a DMA using one Bank

- DMA-Fake.png (8.9 KiB) Viewed 2285 times

/REG-CF is the normal select signal to access the registers of the IDE Task File and is only asserted (low) when you normally access the registers in PIO mode. The /BANK-CF is asserted whenever you want to access the DATA Register. /BANK-CF is asserted for one entire bank, but due to the AND gates whatever address within the bank is accessed it always selects the Data register of the Task File. So you can use the MVN or MVP instructions to transfer the sector buffer to/from memory.

As for busses in Eagle I used them, but only for signals with suffixes, so I named the Bus like A[0..15]. But did not know you can specify a free list of signal names, separated with comma, and even mix and match both, signals with suffixes and individual names in one bus. That's really a cool feature. Then together with the labels it makes even a complex schematic neat and clean. Thanks for the hint.

I did not find the time to redraw all signals and busses using your trick. But nevertheless, so you don't have to wait too long, here the preliminary drawings of my design

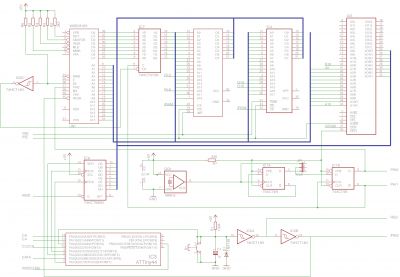

First the core with the CPU, Memory, Keyboard, DP-RAM (Video), Clock and Reset circuit

- SBBC Main Parts

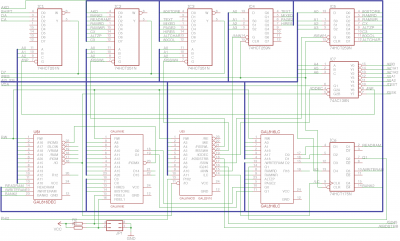

As next follows decoder, the internal IO required to emulate the Apple II and other logic packed into GALs

- SBBC Internal IO

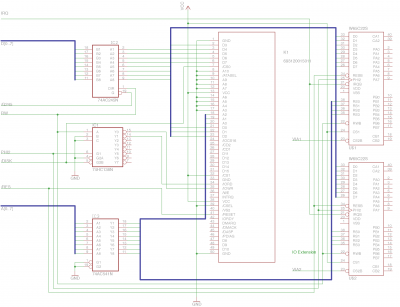

And the last drawing contains the IO connected to the IO Extension slot

- SBBC External IO (IO Expansion Bus)

The two SC2691 (UART) are not drawn yet, but are not required to get an idea of my design. I use GALs instead of a CPLD (I have not yet jumped into this cold water) and as it is at the moment they are used very inefficiently. You could achieve the same result with just 3 GALs. This is mainly because I built the SBBC step by step before I had the final design and made many design changes during the soldering sessions. However it does have all the features I wanted it to have from the beginning. These were PS/2 Keyboard, VGA Display and a mode that emulates an Apple IIe. E.g. I never wanted to decode the full 16Mbyte address space (I need only 512kbyte RAM). Even better, instead of a real 16-bit IDE I use the CF-Cards in 8-bit IDE mode which made the interface a piece of cake.

Regards

Peter