One other thing I forgot... I was looking up whether I'd need bus drivers or not

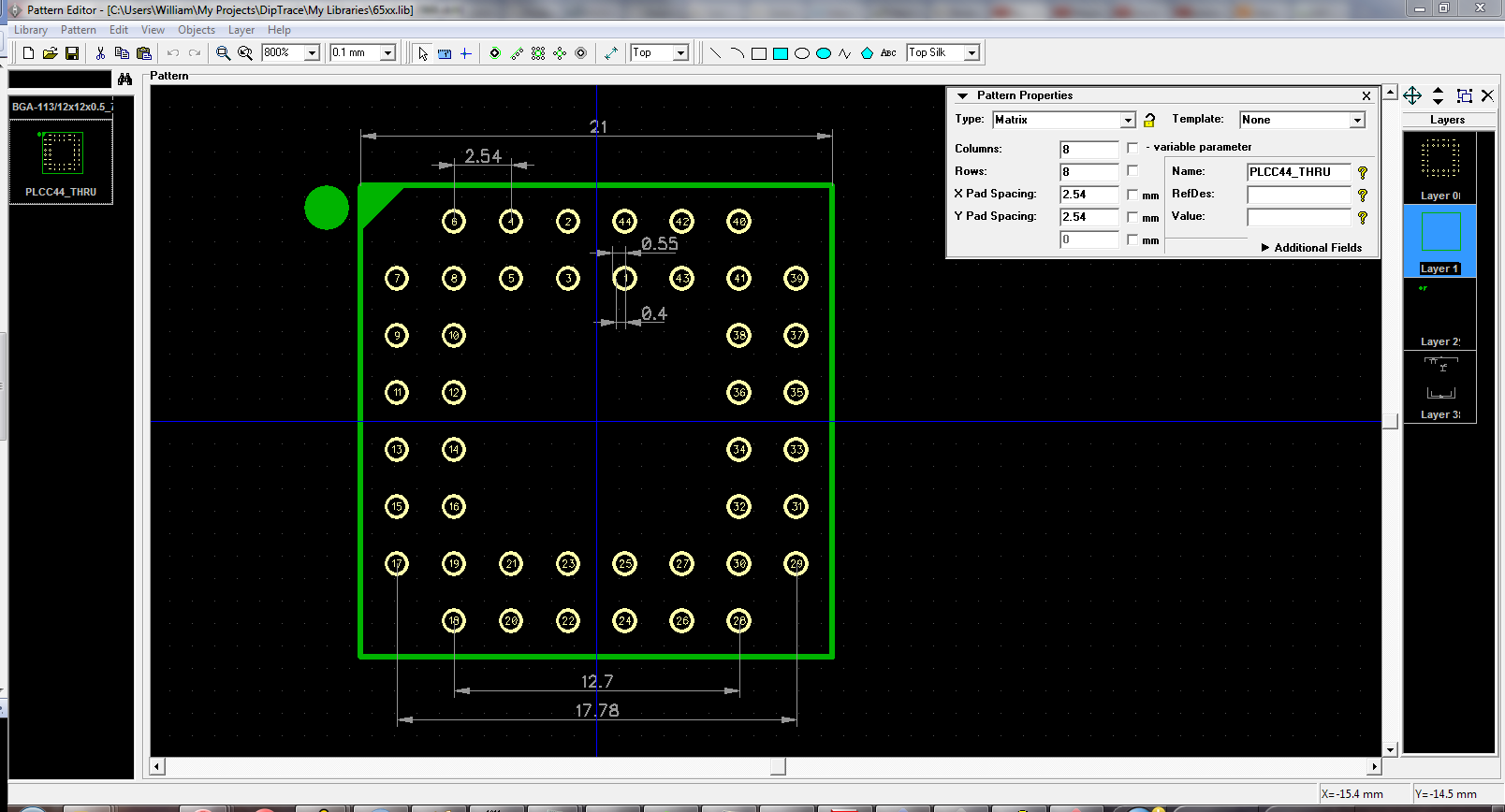

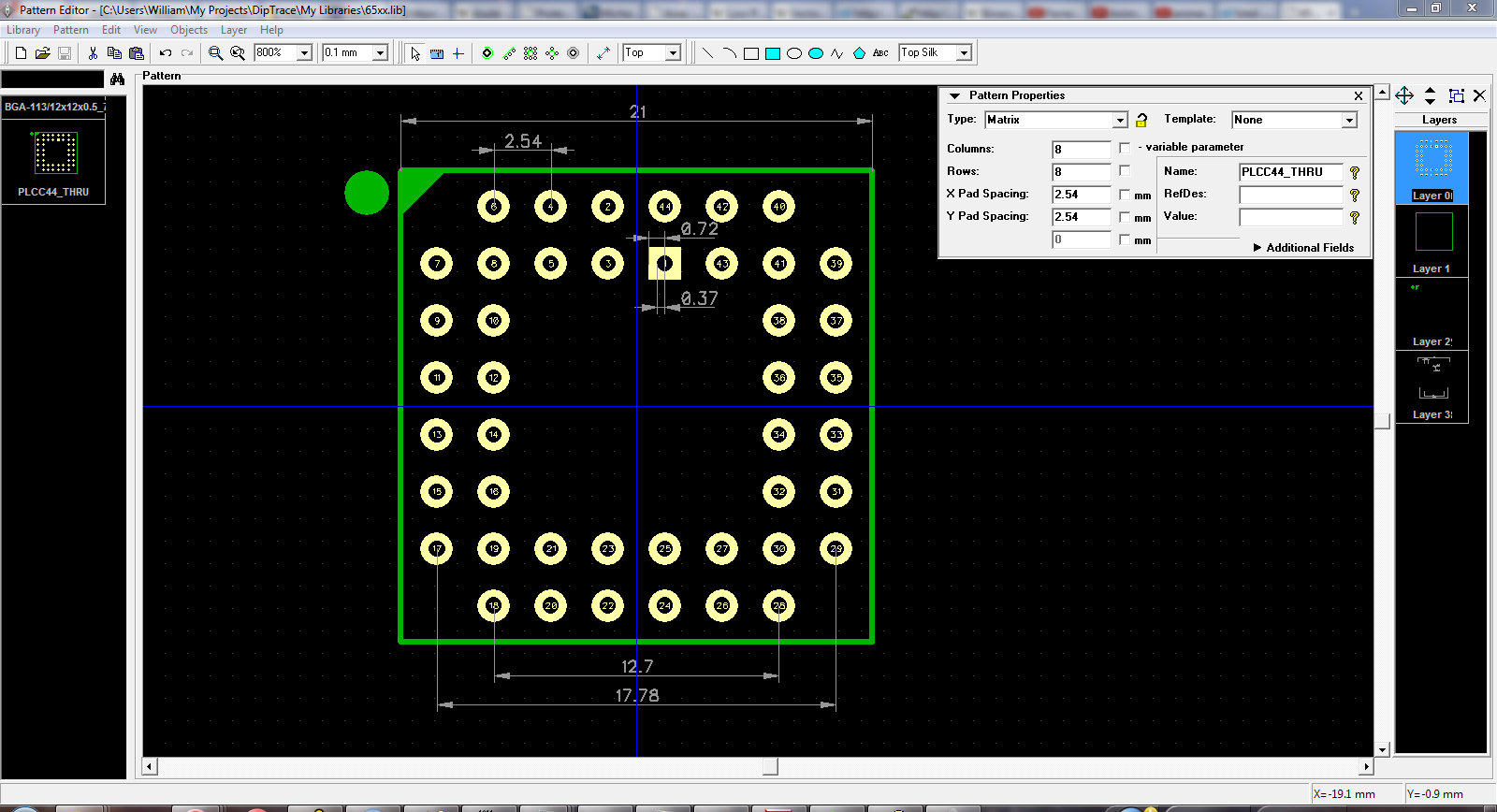

Well, I can tell you that my POC V1.0 unit ran reliably at 12.5 MHz without the SCSI host adapter (HBA) plugged in but wouldn't boot at anything higher than 10 MHz with the HBA in place. Observation with the 'scope made it clear that the culprit was bus loading, especially the data bus, which is wired to all I/O chips, as well as the SRAM. The devices themselves don't contribute much to loading, but the traces and sockets do. Incidentally, plugging in the HBA effectively takes the buses off-board, plus adds two more sockets. That it works at 10 MHz seems to be a minor miracle.

When I did the POC V1.1 update I worked on reducing address and data bus path lengths and was able to get that unit to boot at 12.5 MHz with the HBA plugged in. However, 'scope observation still shows that the data bus is being dragged down and the edges are rounded, though not enough to cause anything to get confused. V1.1 will

not boot at 14 MHz with the HBA and the data bus looks better but still shows some edge rounding and a little bit of ringing. This is with 74AC logic.

I am not going to use bus drivers in POC V2, which will use a CPLD for glue logic. I will start it off at 10 MHz and then keep bumping up the clock until it won't run. I know that the limit won't come from the CPLD, which is 10ns pin-to-pin.

For an initial system, even with DMA, I can see the logic. However, what happens when the drive strength of the '816 is no longer sufficient when you start adding more peripherals? Will the new delay from the bus drivers cause the initial design at the original clock speed to go kaput? And would a hypothetical DMA controller need to disable the bus driver as well, or would the BE pin be sufficient?

I can't think of any conflicts offhand, but just for "preventative maintenance

", would the addition of a bus driver on the address/data lines cause any conflicts with the process of cycle-steal DMA?

My earlier comment about being sure that everything is "downstream" of the bus drivers accounts for the skew between inputs and outputs at the drivers. You will have to use very fast logic to keep skew at a reasonable level.

During DMA, the MPU must be off the buses, which means that the bus drivers must be tri-stated. My earlier example doesn't show this, as it came from a circuit where no DMA was contemplated.

I should probably look at the original IBM PC schematic for an example...

I suspect you'll be astonished at how much silicon (74LS) it took to get it to work.