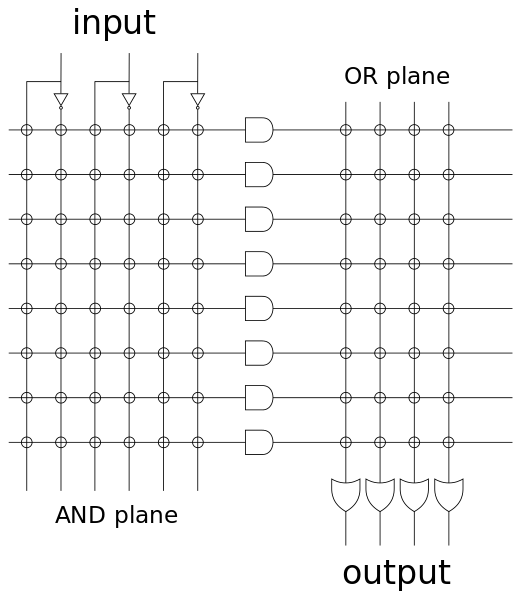

In the most simplistic terms, the Programmable Logic Array (PLA) is a device that allows logic products to be summed (combined) to form a logic signal. The logic products are represented by the AND terms, and the sums are represented by the OR terms.

In your diagram, the inputs are put into the device as true and not true terms. Another array wires crossing under these input wires collect these terms into a single product. As represented in your diagram, the product term can consist of any of the inputs and their complements.

A second array of wires allows the product terms to be collected into sums of product terms. Thus, the output each of the AND gates functions as an input to this second array, and another set of wires below them allow these terms to be collected into sums of products which are the outputs of the ORs shown on your diagram.

In the 6502 and similar processors which use PLAs, the IR (instruction register), the processor sequencer, and other signals such as the processor flags are provided as inputs to the PLA. The number of OR terms is generally much higher than the number of inputs so that their outputs can be used to control specific logic circuits.

In the 6502, the IR is an 8-bit register, the processor sequencer must represent at least 7 memory cycles (so it's at least 3 bits in width), IRQ, NMI, the ALU flags (NVZC), Interrupt Mask (I), Decimal Mode Flag (D), memory ready (RDY), etc., are inputs to the PLA.

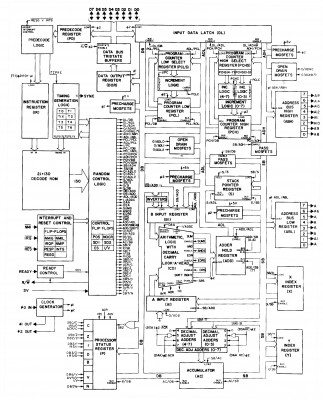

Elsewhere on the Internet there's a block diagram of the 6502 (

Hanson's Block Diagram) that shows that the number of inputs signals into the PLA are 21 and the number of outputs are 130. This means that there are at least 42 (true and not true) inputs into the first array of your diagram, and that there are 130 OR gates collecting product terms in the second array of your diagram. However, there's no direct way to determine the number of AND gates used to develop the product terms collected by the OR gates.

The beauty of a logic arrays like the one used in the 6502 is its ability to be tailored specifically to the requirements of the application. As a user programmable element, there's a practical limit imposed by the process used in its implementation. Thus, PLAs tend to have a fixed number of AND terms and a fixed number of OR terms. The 6502 uses a logic array where the number of AND and OR terms is determined by the designer.

As you can also see in the referenced block diagram, there's feedback from the decode logic into the processor sequencer. This feedback determines the next cycle of the sequencer. Because the designer used a PLA in the implementation, at each state in the sequencer, the designer is able to take a branch to the appropriate next state with a minimal amount of logic. Further, the state transitions equations have access to the current state of all critical signals and the instruction register. Together, the decode logic and the sequencer can minimize the number of distinct states required to implement the complex addressing modes of the 6502.

Viewed as a Finite State Machine (FSM), the 6502 is best characterized as a Mealy model FSM. Without the regularity provided by the PLA, the implementation of the 6502 would have been significantly more difficult in "random" logic.

That being said, there's a penalty to be paid by using a PLA: PLAs are generally slower than random logic. But I'm of the opinion that given the technology of the time, the lower operating speed imposed by the PLA was compensated for by the improved efficiency of the processor as whole. This is supported by claims made by others on this forum and elsewhere regarding the performance of a 6502 at 1MHz compared to the performance of an 8080 at 4MHz.

- 6502 Block Diagram - Hanson

Michael A.