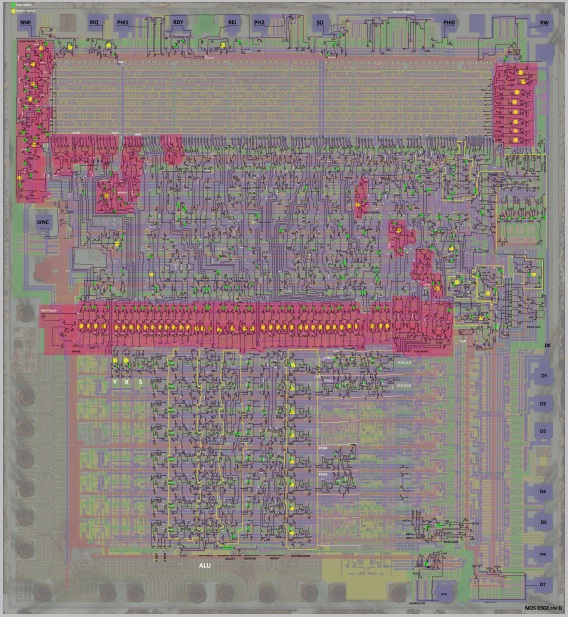

6502 simulation already done.

I have implemented almost all random logic in form of C code.

Please again ignore my previous post

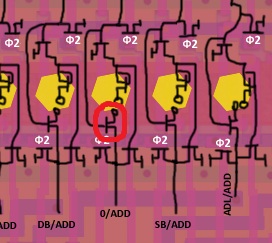

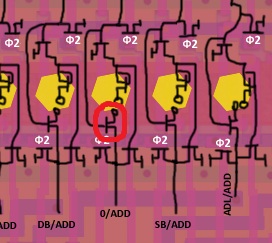

, because I was wrong - random logic outputs are NOT using RS-like latches (I thought it was depletion-mode transistor but it was simply pullup ).

As you already noticed, other RS-like formations (flags) are not really "flip/flops". They are just some transient circuits, which are "loaded" during PHI2 and "read-back" during PHI1. Such pass-through gates are need to eliminate unwanted read-back conflicts during "load".

Also I (possibly) found a glitch in program counter swapping (well, not actually glitch

just some specific 6502 inner working). The reason is program counter put its value on ABH/ABL and loaded back in inverted form back again, to compensate swap, which occure every half-clock.

After I complete random logic, I show you opcode lifetime sequence (which "commands" random logic dispatch to bottom part per cycle).

Reset sequence is simply sort of BRK (its already known though), since instruction register is 0x00 after reset.

I found, that stack register keep its value in inverted form, so its value after power-up is NOT(0x00) = 0xFF (extended to 0x01FF). When stack register value is loaded from the bus (and written back), it get pre-inverted.