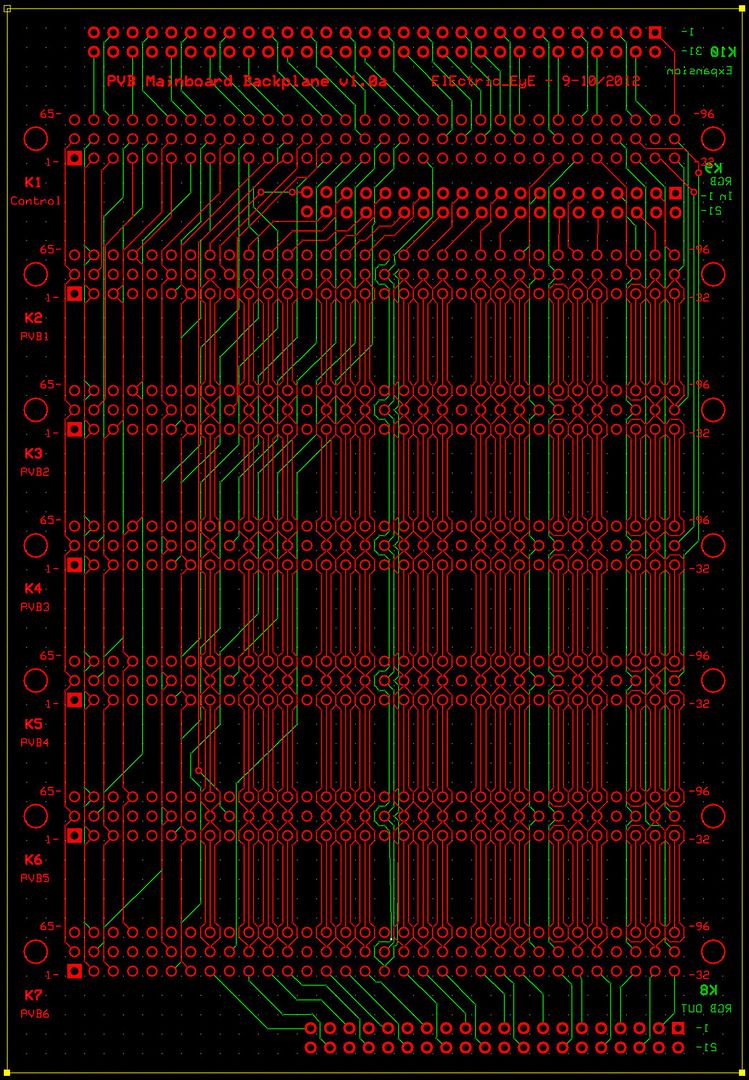

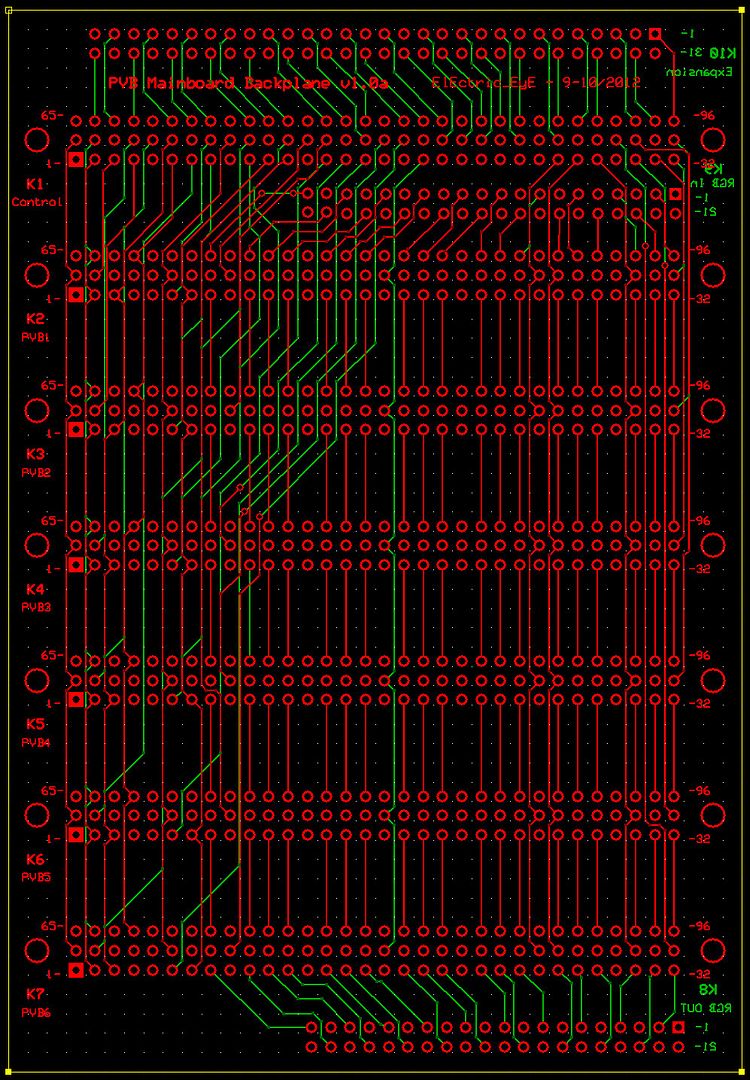

Using their Standard service, I can get 2 boards made for ~$100. The size limitation is gone also and the temptation was their to increase the number of PVB slots from 4 to 8, thereby maximizing pin usage from the control board connector. This increase in board size would be negligible in cost, however with the realization that in the past I have missed errors or have had other small oversights with all of my first attempts so far I will go ahead with the current design and hopefully put this order in 2 days. Definately, by next week though.

Yes, but the EPCB standard service product does not have silkscreen or solder mask. Are you okay with those features being omitted?

.

.