Code: Select all

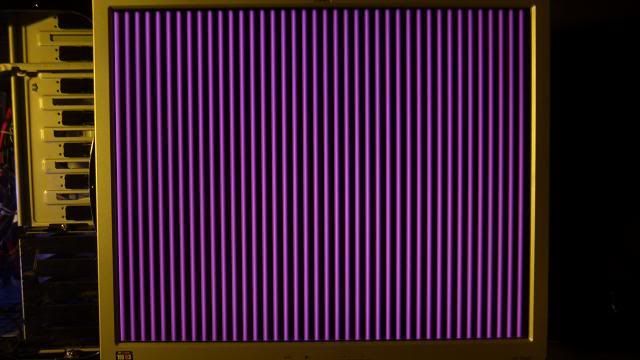

module patterngen(

output [4:0] Red_data,

output [5:0] Green_data,

output [4:0] Blue_data,

input pclk,

input hsync,

input vsync,

input hstart,

input vstart,

input hblank,

input vblank

);

reg [4:0] Red_count = 31;

reg [5:0] Green_count = 63;

reg [4:0] Blue_count = 31;

reg countflag = 1; //start with 1 since hblank starts with 1 on powerup

always @(posedge pclk)

if ( hstart | hblank )

countflag <= ~countflag; //toggle flag at beginning and end of displayed line

always @(posedge pclk)

if ( countflag )

begin

Red_count <= Red_count - 1;

Green_count <= Green_count - 1;

Blue_count <= Blue_count - 1;

end

assign Red_data = Red_count;

assign Green_data = Green_count;

assign Blue_data = Blue_count;

endmodule