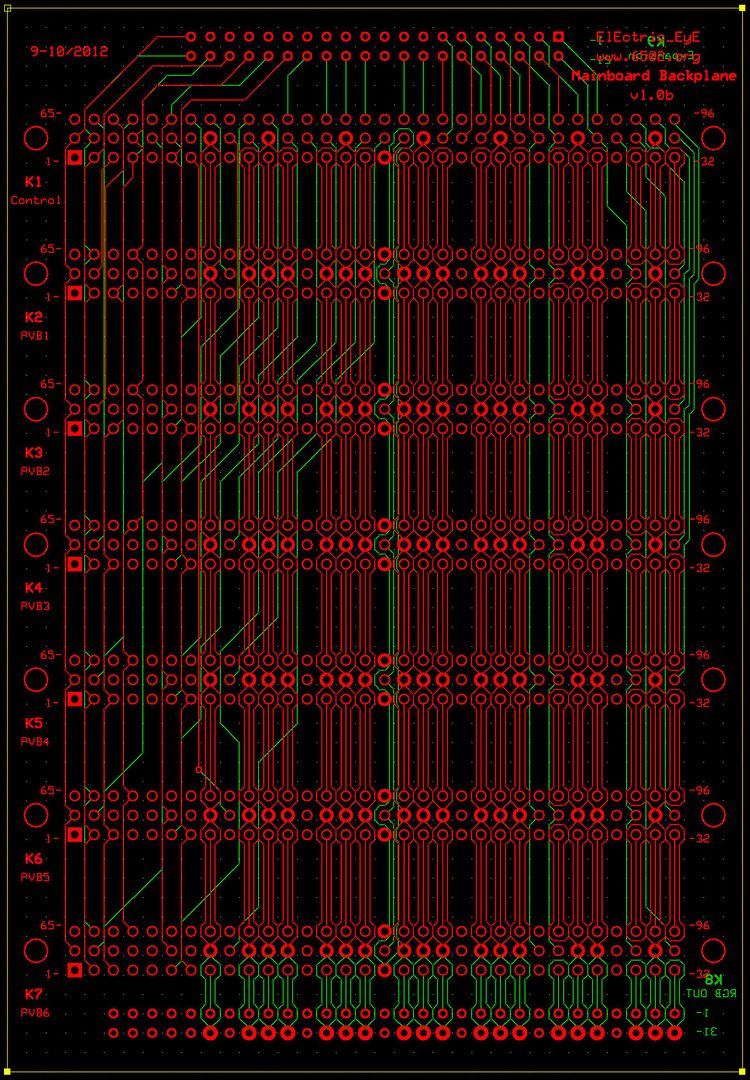

6 Parallel Video Boards and a still yet to be designed Controller board will be able to fit on the main connectors K1-K7. Thankfully, the Standard service does not appear to have a hole limitation as this design uses 800+ holes.

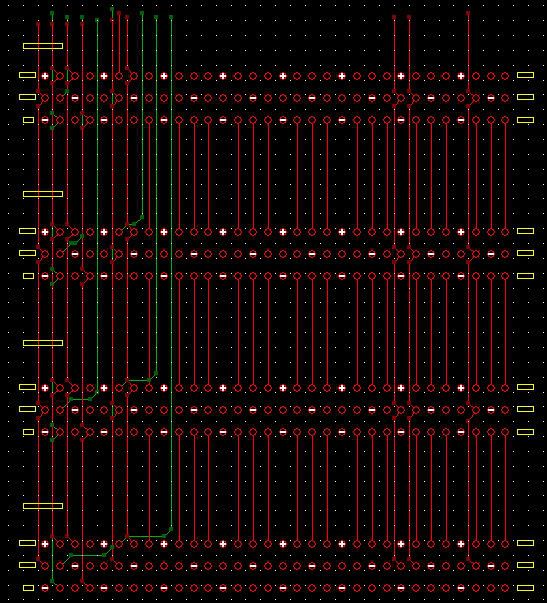

After wrestling abit for the layout of this Mainboard, I came to the conclusion this layout must absolutely dictate the assignment of pins for the main connector of the Parallel Video Board. Meaning, at certain points, 2 board layouts (PVB & Mainboard) had to be developed simultaneously.

A nice thing I had noticed is that a total of 48-signals can be joined directly using straight traces! This was very good news as early on, as I had not routed a single signal on the bottom layer or have had to use via's...

Also I must mention Garth Wilson, who has contributed significantly to the final layout of this design, spotting some critical errors and making suggestions about improvements for successful high-speed (100+MHz) signal transmission. A great many thanks Garth!

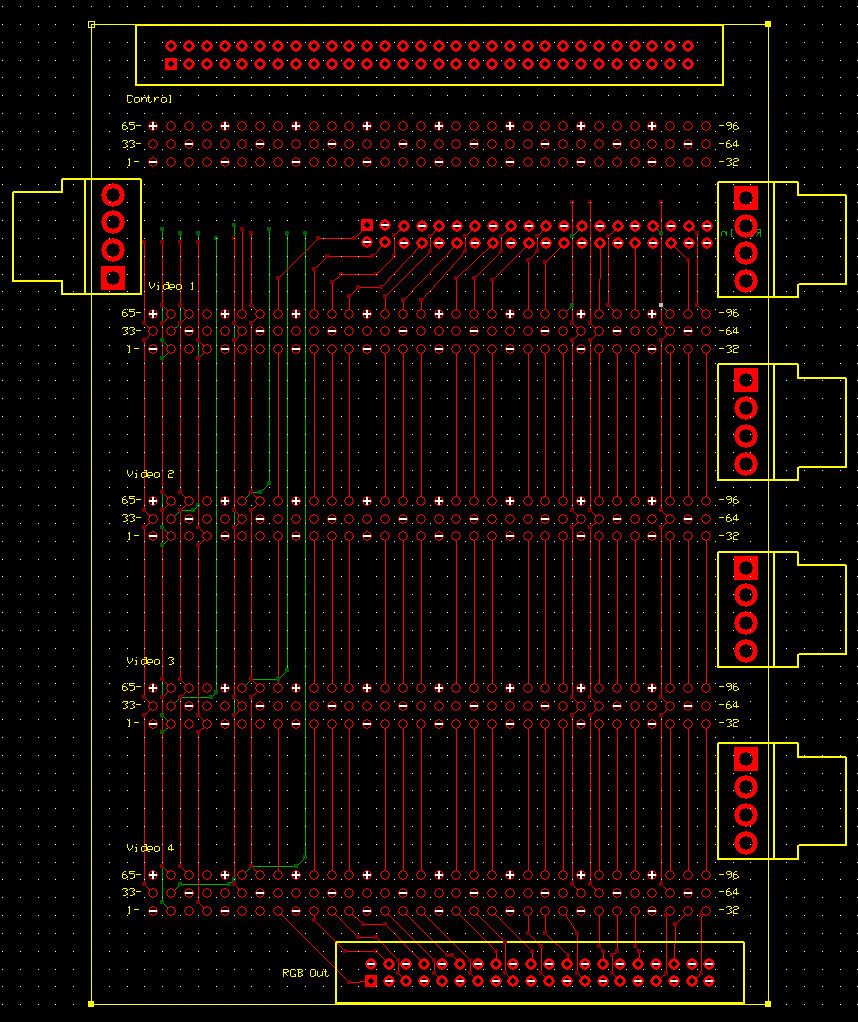

Here is the layout showing 6 PVB headers K2 thru K7. K1 is the controller board. K8 is an expansion header primarily meant for a future HDMI board. K9 is the expansion header meant for a sound board at this point. It uses a 16-bit databus, utilizing the lower 8 bit databus common to all the PVBs. K9's layout is done, but actual pin assignments are still a work in progress. All headers are mounted on top, except for K8 & K9.

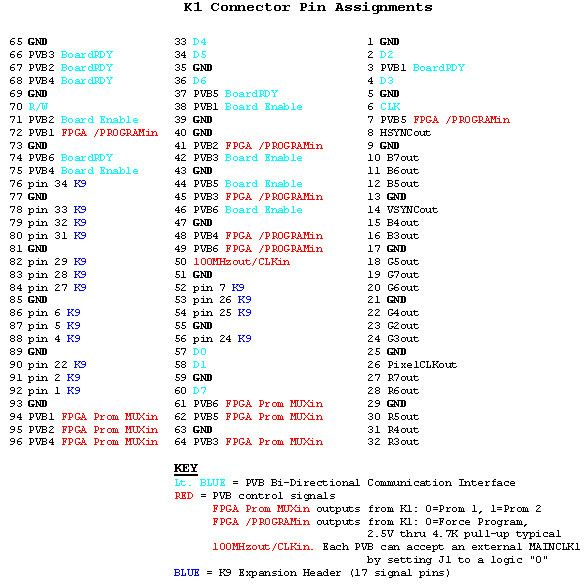

Pin assignments for the K1 Controller Board connector:

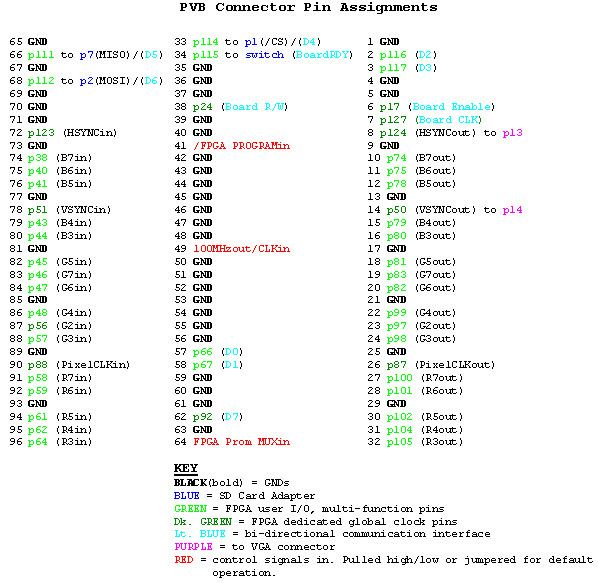

Pin assignments for K2-K7 Parallel Video Boards:

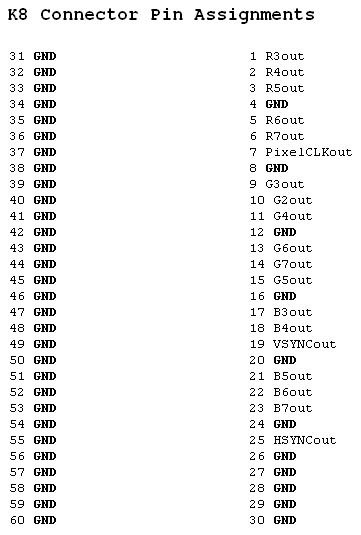

Pin assignments for the HDMI header:

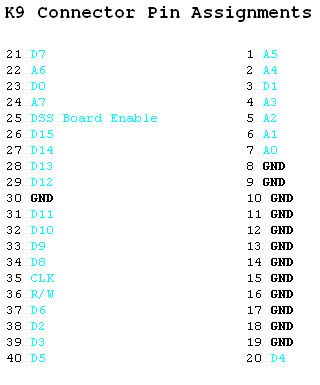

Pin assignments for the Expansion header (in-flux):

Parts list:

Code: Select all

QTY Price Description Part# Package Supplier ID

-------------------------------------------------------------------------------------------------------------

7 $4.85 96-pin male receptacle A32857-ND vertical thru-hole Digi-Key K1,K2,K3,K4,K5,K6,K7

1 $3.78 40-pin male header MHB40K-ND vertical thru-hole Digi-Key K9

1 $5.63 60-pin male header MHB60K-ND vertical thru-hole Digi-Key K8

14 $0.43 M2.5x1" fem/fem spacer AE10862-ND thru hole Digi-Key

14 TBD M2.5x15mm Screw TBAEDIT: 10/12/12 - Added K7, K8 pin assignments and parts list.

EDIT: 10/17/12 - Expanded design to include 6 PVB's using same board size.

EDIT: 10/18/12 - This thread is currently a W.I.P.

EDIT: 10/19/12 - Last thread EDIT was a mistake, however updated K1 connector pin assignments

EDIT: 10/23/12 - 2 x Updated parts list

EDIT: 10/23/12 - Updated K8,K9 pics

EDIT: 10/30/12 - Pre-Finalized design

EDIT: 8/05/13 - Changed Title