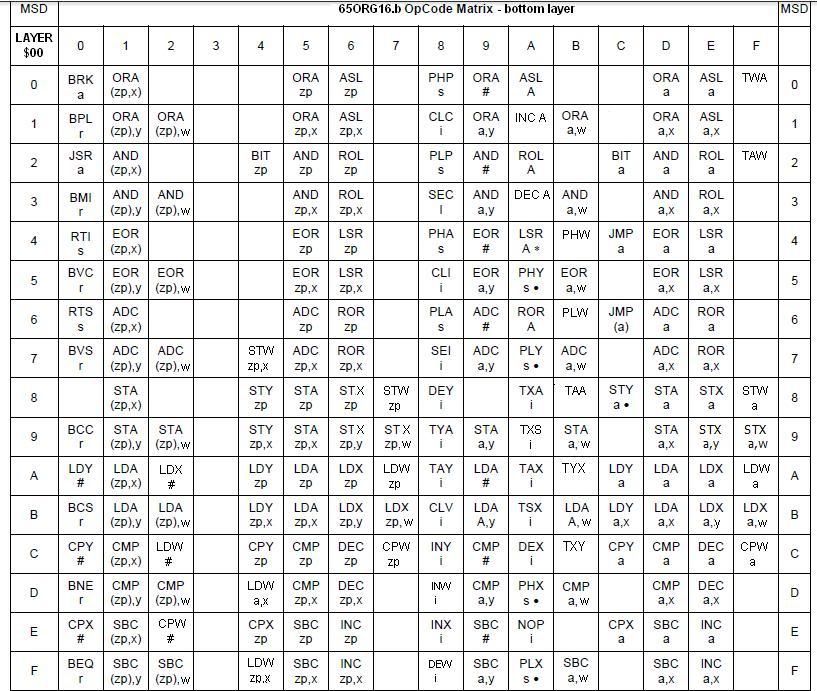

I've "de-optimized" Arlet's opcode state machine in order to make sure I have every single bit perfect

as it needs to be to obey the opcode table above, or the Sim will crash as it has been doing all day, at least on my fast machine, with ISE13.2, it is crashing. On my slow laptop, with ISE13.4, the Sim appears to be correct... I'm not blaming ISE at this point. I find errors in my opcode decoding frequently. It's not pretty, but progress will be made!

Code: Select all

/*

* Microcode state machine */...

casex ( IR[15:0] )

16'b0000_0000_0000_0000: state <= BRK0;

16'b0000_0000_0010_0000: state <= JSR0;

16'b0000_0000_0100_0000: state <= RTI0; //

16'b0000_0000_0100_1100: state <= JMP0;

16'b0000_0000_0110_0000: state <= RTS0;

16'b0000_0000_0110_1100: state <= JMPI0;

16'bxxxx_xxxx_xxx0_01xx: state <= ZP0; // even rows, columns 4,5,6,7

16'b0000_0000_xxx1_0000: state <= BRA0; // odd rows, column 0

16'bxxxx_xxxx_xxx0_0001: state <= INDX0; // even rows, column 1 --(zp,x)

16'bxxxx_xxxx_xxx1_0001: state <= INDY0; // odd rows, column 1 --(zp),y

16'bxxxx_xxxx_xxx1_0010: state <= INDY0; // odd rows, column 2 --(zp),w

16'bxxxx_xxxx_0xx1_0101: state <= ZPX0; // row 1,3,5,7, column 5

16'bxxxx_xxxx_0xx1_0110: state <= ZPX0; // row 1,3,5,7, column 6

16'bxx00_xx00_10x1_010x: state <= ZPX0; // row 9,B, column 4,5

16'b0000_0000_0111_0100: state <= ZPX0; // STW zpx

16'bxxxx_xxxx_11x1_01xx: state <= ZPX0; // row D,F, column 4,5,6,7

16'bxxxx_xxxx_0010_1100: state <= ABS0; // BIT abs

16'bxxxx_xxxx_0xx0_1101: state <= ABS0; // row 0,2,4,6 even D column

16'bxxxx_xxxx_0xx0_1110: state <= ABS0; // row 0,2,4,6 even E column

16'b0000_0000_1xx0_11xx: state <= ABS0; // row 8,A,C,E, column C,D,E,F --X/Y/W abs

16'bxxxx_xxxx_xxx1_1xx1: state <= ABSX0; // odd rows, column 9,B,D,F

16'bxxxx_xxxx_xxx1_1110: state <= ABSX0; // odds rows, column E

16'bxx00_xx00_0x00_1000: state <= PUSH0; // PH[A..Q], PHP

16'b0000_0000_x101_1010: state <= PUSH0; // PHX, PHY

16'b0000_0000_0100_1011: state <= PUSH0; // PHW

16'b00xx_00xx_0x10_1000: state <= PULL0; // PL[A..Q], PLP

16'b0000_0000_x111_1010: state <= PULL0; // PLY, PLX

16'b0000_0000_0110_1011: state <= PULL0; // PLW

16'b0000_0000_1xx0_00x0: state <= FETCH; // IMM, row 8,A,C,E, column 0,2

16'bxxxx_xxxx_xxx0_1001: state <= FETCH; // IMM, even rows, column 9

16'b0000_0000_0xx1_1000: state <= REG; // CLC, SEC, CLI, SEI

16'bxxxx_xxxx_1xxx_1000: state <= REG; // DEY, TY[A..Q], T[A..Q]Y, INY, INX, INW, DEW

16'bxxxx_xxxx_xxx0_1010: state <= REG; // <shift/rotate> [A..Q], TX[A..Q], NOP

16'bxxxx_xxxx_00x1_1010: state <= REG; // INC/DEC [A..Q]

16'bxxxx_xxxx_10x1_1010: state <= REG; // TSX, TXS

16'bxxxx_xxxx_1xx0_1011: state <= REG; // T[A..Q][A..Q],TYX,TXY

16'bxxxx_xxxx_1111_00x0: state <= REG; // TW[A..Q], T[A..Q]W

endcase