Recreating the Commodore PET with an FPGA

Quote:

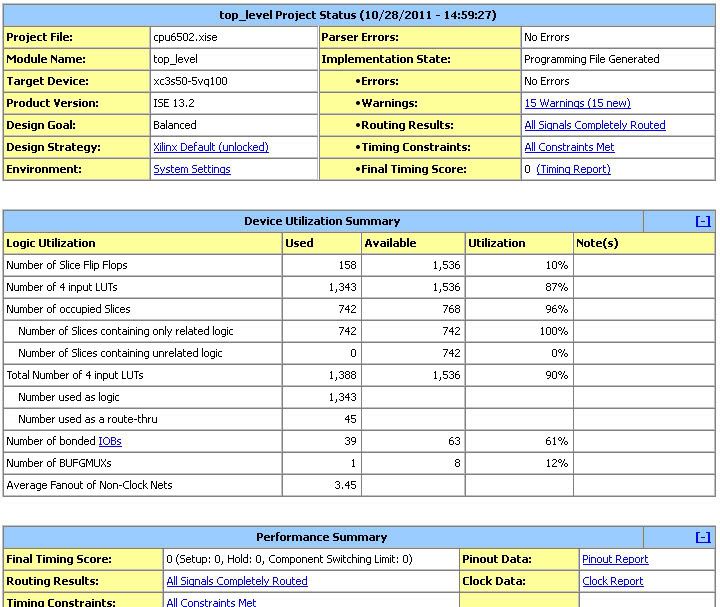

Using a Xilinx Spartan-6 FPGA on the Digilent Nexys3 dev board, he has implemented the Pet in Verilog. Like the original, his clone contains 16K of both ROM and RAM, utilizing the same simulated 6502 microprocessor he used on a previous Apple ][+ project. The FPGA version of the computer sports a 640x400 resolution which is twice that of the original, so [Thomas] simply doubled the size of each of the PET’s pixels to fill in the extra space.