Tonight after coming home from work, I was looking over previous posts and manually entering Arlet's (3) previous RDY mod's to be updated in the CPU.v / ALU.v modules in my new schematic. That is, before I realized his edit!

I would like to ask a Verilog beginners question at the very bottom...

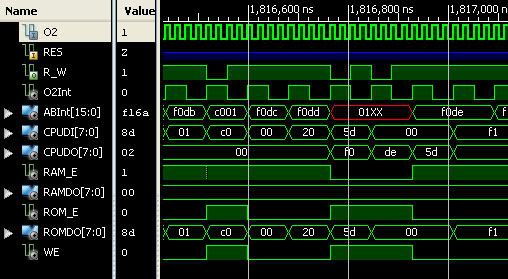

Excellent! I will be able to test the RDY in the hardware once I get the Flash successfully programmed. I'm currently working out a few issues now with system running @12MHz to accommodate the slow 70ns access time of the Flash. I'm trying to implement a top level bi-directional bus that goes to the Flash because I need to program it for a Chip Erase. Before, I was just trying to read from the Flash, but now I need to send 6 consecutive data at certain addresses for the Chip Erase. Got the software figured out, but...

Once I get it working, I'll be able to test RDY when the system is running @38MHz, and I plan to use a DCM, not just FF's. Will put wait states on everything accessed off chip, i.e. display, Flash, etc. Internal RAM and ROM will run full speed at all times.

As I mentioned before somewhere, I have my eye on the Spartan 6 and the same bi-directional bus structures apply to it. Although it seems to have different OBUF's, ISE auto-updates the design. Why Spartan 6? Because, I can solder it (a 144-pin QFP package) and when I put the current design on the Spartan 6, max speed (according to ISE) went from 51MHz to 89MHz...

My Verilog Newbie Question:

Are multiple "always" statements that are present inside of a module handled instantaneously, or is there a priority or a delay when instantiated? I ask this because I noticed you put RDY assignment last in the cpu module, while I had put it after reset. Was wondering if this minute detail affects anything?