My Mainboard Design

-

Karatorian

- Posts: 17

- Joined: 13 Mar 2011

- Location: Rindge NH USA

- Contact:

My Mainboard Design

I've always wanted to build a computer. So lately I've been working on a design for a simple 6502 based machine. As I don't have a whole lot of electronics experience, I'm trying to keep things simple for now.

I've started working on a design, which you can download here. The generic logic gates are supposed to be high speed CMOS 74xx series chips. I didn't like the ones in gschem's default library, so I made my own. However, I've yet to properly set up the pin numbering and lables. (Just call me lazy.)

It's pretty basic at the moment, with 32K of SRAM at the bottom of the address space and 8K of FRAM at the top. The rest of the top half of the address space is currently unoccupied, but I plan to add IO space there (and possibly more RAM).

Clearly, there's some work still to be done. In particular, I cheated and black boxed the clock and reset circuits. Any pointers to resources on solid designs for them would be appreciated. I've noticed a lot of you start with a slower clock speed and then crank it up until it stops working. Do you just use a fixed clock and then swap out the crystals, or is you use a variable clock speed design? If the latter, how do you build one?

I'll appreciate any feedback you can give me, but I have a few specific questions.

Firstly, what should I do with the unused output pins? I know it's not a good idea to just let them float, but I don't know how to properly tie them off.

Secondly, the FRAM's datasheet says that, unlike an SRAM, /CE is edge triggered. On the falling edge, it latches /OE, /WE, and the address lines. So, to make sure /OE is in the proper state when latched, I used two AND gates in the FRAM's address decode. Is this proper design, or just overkill? I originally had one four input AND tied to both /CE and /OE, but then I changed it.

My current address decoding is pretty ad-hoc. I think it'll work alright, but as I start adding IO and stuff, it's sure to get more complicated. Is there a more systematic way of address decoding that's better, or should I just keep going with the random logic gate approach?

Finally, real computers have blikenlights. I want to add LEDs so you can see the state of the buses and stuff. (Probably more useful once I add a single stepping mode.) What's the proper way to do that and avoid causing problems?

Anyway, that's what I'm working on and wondering about. Any input you have would be greatly appreciated.

I've started working on a design, which you can download here. The generic logic gates are supposed to be high speed CMOS 74xx series chips. I didn't like the ones in gschem's default library, so I made my own. However, I've yet to properly set up the pin numbering and lables. (Just call me lazy.)

It's pretty basic at the moment, with 32K of SRAM at the bottom of the address space and 8K of FRAM at the top. The rest of the top half of the address space is currently unoccupied, but I plan to add IO space there (and possibly more RAM).

Clearly, there's some work still to be done. In particular, I cheated and black boxed the clock and reset circuits. Any pointers to resources on solid designs for them would be appreciated. I've noticed a lot of you start with a slower clock speed and then crank it up until it stops working. Do you just use a fixed clock and then swap out the crystals, or is you use a variable clock speed design? If the latter, how do you build one?

I'll appreciate any feedback you can give me, but I have a few specific questions.

Firstly, what should I do with the unused output pins? I know it's not a good idea to just let them float, but I don't know how to properly tie them off.

Secondly, the FRAM's datasheet says that, unlike an SRAM, /CE is edge triggered. On the falling edge, it latches /OE, /WE, and the address lines. So, to make sure /OE is in the proper state when latched, I used two AND gates in the FRAM's address decode. Is this proper design, or just overkill? I originally had one four input AND tied to both /CE and /OE, but then I changed it.

My current address decoding is pretty ad-hoc. I think it'll work alright, but as I start adding IO and stuff, it's sure to get more complicated. Is there a more systematic way of address decoding that's better, or should I just keep going with the random logic gate approach?

Finally, real computers have blikenlights. I want to add LEDs so you can see the state of the buses and stuff. (Probably more useful once I add a single stepping mode.) What's the proper way to do that and avoid causing problems?

Anyway, that's what I'm working on and wondering about. Any input you have would be greatly appreciated.

@loop: lda (src),y — sta (dst),y — iny — bne @loop — inc src+1 — inc dst+1 — dex — bne @loop

Hi Karatorian

your link to http://static.karatorian.org/hardware/mainboard.pdf doesn't work for me.

Cheers

Ed

your link to http://static.karatorian.org/hardware/mainboard.pdf doesn't work for me.

Cheers

Ed

Re: My Mainboard Design

Karatorian wrote:

Firstly, what should I do with the unused output pins? I know it's not a good idea to just let them float, but I don't know how to properly tie them off.

André

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Re: My Mainboard Design

Karatorian wrote:

... I've noticed a lot of you start with a slower clock speed and then crank it up until it stops working. Do you just use a fixed clock and then swap out the crystals, or is you use a variable clock speed design? If the latter, how do you build one?...

Cool idea with the FRAM. It'll probably be your speed limiter at this point. What access time?

- GARTHWILSON

- Forum Moderator

- Posts: 8775

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Quote:

I've started working on a design, which you can download here.

Quote:

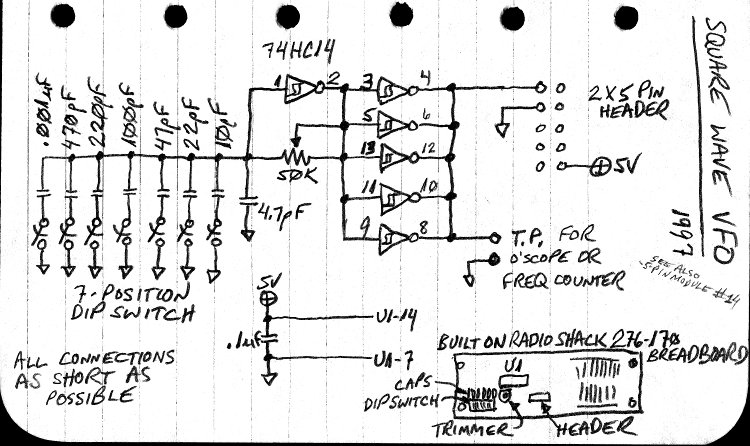

In particular, I cheated and black boxed the clock and reset circuits. Any pointers to resources on solid designs for them would be appreciated.

Quote:

I've noticed a lot of you start with a slower clock speed and then crank it up until it stops working. Do you just use a fixed clock and then swap out the crystals, or is you use a variable clock speed design? If the latter, how do you build one?

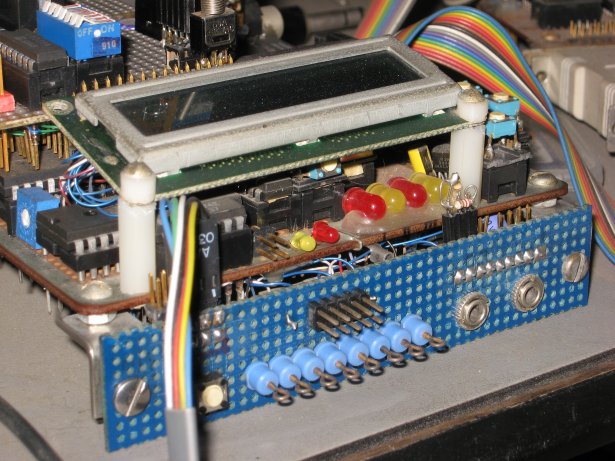

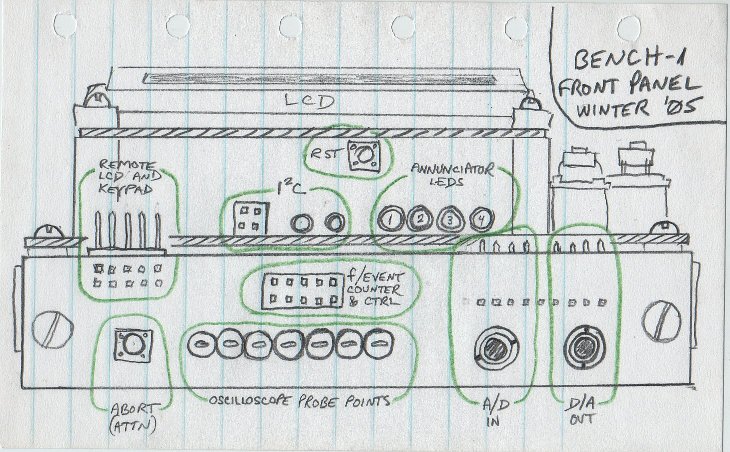

I made a much smaller and faster one later, but this will do the job for beginning construction, and the faster stuff (100MHz) is more of a challenge to build and make it well behaved.

Quote:

what should I do with the unused output pins? I know it's not a good idea to just let them float

Quote:

the FRAM's datasheet says that, unlike an SRAM, /CE is edge triggered.

Quote:

My current address decoding is pretty ad-hoc. I think it'll work alright, but as I start adding IO and stuff, it's sure to get more complicated. Is there a more systematic way of address decoding that's better, or should I just keep going with the random logic gate approach?

Quote:

Finally, real computers have blikenlights. I want to add LEDs so you can see the state of the buses and stuff. (Probably more useful once I add a single stepping mode.) What's the proper way to do that and avoid causing problems?

with the legend:

There's more about this computer on my project pages, at http://www.6502.org/users/garth/projects.php?project=1 . They're outdated and don't show the mezzanine, but you'll get more info.

Edit: I have a series of articles now on building your own 6502 computer, at http://wilsonminesco.com/6502primer/index.html.

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

-

Karatorian

- Posts: 17

- Joined: 13 Mar 2011

- Location: Rindge NH USA

- Contact:

Sorry about the 404, I'm such a scatter brain sometimes. It's fixed now.

I've read about hooking unused inputs through a resistor, rather than straight to Vcc, but I've never understood the point. Is there some situation where it's actually needed, or is it just a waste?

Access time is 70ns. It'll be a cool idea if I can get one. Nowhere I looked had them in stock, so I just requested a sample from the company. The eventual idea is to put in a switch to enable FRAM writing, which will allow the computer to do it's own "ROM" updates, but protect the boot code from getting scribbled on by buggy code.

Sounds unlikely. How do you get it out of enable?

You can get the datasheet from the manufacturer's website: http://ramtron.com/files/datasheets/FM16W08_ds.pdf Maybe "edge triggered" isn't the right terminology, but they go into detail about how it differs from SRAM. Basically, /CE needs to be clocked, it can't be held low.

Ok, maybe the blinkenlights aren't such a good idea. Although, I do plan on implementing single-stepping. Hacker folklore about old dinosaurs with lots of lights is somehow appealing to me. I guess I'll have to make an LED bank IO device instead. In retrospect, it'd probably be more useful anyway as then they'd be under software control, rather than just flickering away at imperceptible speed.

Thanks for the pointers to the clock circuits, I'll look into them and expand my schematic. Thanks for the rest of your advice as well, I'll let you know what comes out of it.

fachat wrote:

Unused inputs should be tied to a defined logic level. You could for example define a "logic 1" signal with a single 10kOhm to VCC and use that for all inputs. OTOH I normally connect them directly to VCC, but that has bitten me because I wasn't able to cut a trace and re-use that logic gate when I found a bug in the first draft board.

ElEctric_EyE wrote:

Cool idea with the FRAM. It'll probably be your speed limiter at this point. What access time?

GARTHWILSON wrote:

Quote:

the FRAM's datasheet says that, unlike an SRAM, /CE is edge triggered.

Ok, maybe the blinkenlights aren't such a good idea. Although, I do plan on implementing single-stepping. Hacker folklore about old dinosaurs with lots of lights is somehow appealing to me. I guess I'll have to make an LED bank IO device instead. In retrospect, it'd probably be more useful anyway as then they'd be under software control, rather than just flickering away at imperceptible speed.

Thanks for the pointers to the clock circuits, I'll look into them and expand my schematic. Thanks for the rest of your advice as well, I'll let you know what comes out of it.

@loop: lda (src),y — sta (dst),y — iny — bne @loop — inc src+1 — inc dst+1 — dex — bne @loop

- BigDumbDinosaur

- Posts: 9428

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

F-RAM

Karatorian wrote:

I've read about hooking unused inputs through a resistor, rather than straight to Vcc, but I've never understood the point. Is there some situation where it's actually needed, or is it just a waste?

Quote:

the FRAM's datasheet says that, unlike an SRAM, /CE is edge triggered.

/CE Input Chip Enable: /CE selects the device when low. Asserting /CE low causes the address to be latched internally. Address changes that occur after /CE goes low

will be ignored until the next falling edge occurs.

Functionally translated, pulling /CE low selects the chip, without regard to the clock cycle. Sounds like a level-sensitive input to me, just like any other RAM or ROM.

x86? We ain't got no x86. We don't NEED no stinking x86!

Re: F-RAM

BigDumbDinosaur wrote:

Sounds like a level-sensitive input to me, just like any other RAM or ROM.

Karatorian wrote:

I've read about hooking unused inputs through a resistor [...] is it just a waste?

Quote:

"Connect unused inputs to VCC through a 1k resistor so that if a transient that exceeds the input maximum rating should occur, the impedance will be high enough to protect the input."

BigDumbDinosaur wrote:

The theory behind using resistors to tie unused gate inputs to Vcc is in the event you suddenly need the gates you can make a simple patch to the board.

-- Jeff

- BigDumbDinosaur

- Posts: 9428

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

Re: F-RAM

Dr Jefyll wrote:

BigDumbDinosaur wrote:

Sounds like a level-sensitive input to me, just like any other RAM or ROM.

x86? We ain't got no x86. We don't NEED no stinking x86!

-

Karatorian

- Posts: 17

- Joined: 13 Mar 2011

- Location: Rindge NH USA

- Contact:

I haven't been working on my mainboard design much. (I got distracted with ideas for a USB FRAM/EPROM programmer.) However, I came up with a new address decoding scheme (using a '138), which lead to a more organized (if still unpopulated) memory map.

As before, the low 32k is the SRAM. The high 32k is now split into eight banks of 4k each, the seventh and eighth of which are occupied by the boot FRAM. So it's the same layout as before, but now IO space (or whatever else) has (course grained) address decoding.

Once I got that laid out I started thinking about IO devices. I've got a lot of ideas, but I figured I'd keep the main board pretty bare bones. So I decided to throw a bus on it instead. I've been interested in passive backplanes (like the S100) ever since I first heard of them. However, rather than the traditional edge connectors and separate backplane, I borrowed an idea from the Arduino and sketched out a plan for stackable mezzanine boards.

The bus is pretty dumb, it's mostly just the native interface of the 65C02. After drawing up various concepts and looking at available connectors, I decided to go with two rows of 24 pin sockets. I plan to place the sockets at opposite ends of the board and organized their pinouts accordingly.

The first connector (which I've dubbed the X bus) consists of everything needed for address decoding. Namely, the address bus, write enable, and the clock. Additionally, it has the six available decode lines from the '138, which select 4k banks in the open space between the SRAM and FRAM.

The other connector (the Y bus) has everything else. Which means, the data bus, power rails (+5 and +12), and most of the CPU pins (missing are PHI1O, PHI2O, and /SO). With two grounds (one next to each power rail), this leaves four reserved pins. (Or five if I give up one ground. However, this may not be enough as I've already got extra ideas brewing.)

Originally, I only planned on using twelve bit addressing on the bus (the higher bits are all decoded by the mainboard already), which would've saved a few pins, but then I had a eureka moment that made me change my mind. I realized that, if the bus supported it, I could use the programmer I've been designing in circuit! (I just realized that it could also be used to drive IO boards directly from the PC).

Once I made that change, other good reasons for having the full address bus came to mind, like DMA, and remote debugging. Some of these ideas require additions to the bus that haven't been fully developed. In circuit programming wants to run the clock on it's own terms, so it'd need some method of disabling the mainboard's clock. One of my more sophisticated debugging ideas requires the PC emulating potentially any address, which would require some way of avoiding the onboard address decoding. Simple DMA ought to work with what I've already got defined though.

Another idea contending for the few remaining pins is some sort of reset line. The /RES line is exposed on the bus, so any device that wanted to could conceivably pull it high if it wanted, but that seems like a dirty hack. Furthermore, if that device has a reset connected to /RES, it may not even work at all.

Since it's the device pulling /RES high, it'll reset itself and then it's anybody's guess what state the /RES line'll be in. The reset period may not be long enough for other devices on the bus to properly reset, or, worse, the /RES line may be pulled up indefinitely. Having any output lines connected to /RES is probably a bad idea, as I'm sure the state of said line during a reset is undefined for a great many devices, which could reek all kinds of havoc.

What's needed is a dedicated reset output (from the daughter board's POV) the instructs the mainboard's reset circuitry to cleanly reset the machine. So there goes another pin.

One more thing that could be really nice to have once I start developing IO devices would be a programmable interrupt controller. That would require adding additional IRQ lines, so It's likely the bus is going to get larger before I actually implement this.

Anyway, you can check out the latest version of the schematic here. It's still got no clock and reset sub-circuits. That's my next mission (thanks again for the tips), but before then, I've got a few questions.

First up is another question about unused inputs. For completely unused inputs, things are pretty simple, just tie them to the proper logic level. However, what's I'm wondering about is how to handle inputs that aren't used on the mainboard, but might be used by a mezzanine. Then again, they might not...

For instance, the mainboard doesn't do anything involving interrupts, so it wants /IRQ tied to ground. If the mainboard ties it to ground, what happens when some device tries to bring it high? And if it doesn't work, how do you do it correctly?

It's a similar situation with RDY and BE. However, in this case, for normal operation, the mainboard wants them tied high. So, can they be driven low by something else? It seems to me that one way (tied low or tied high) ought to work and the other one won't. (Unfortunately I don't know enough to be sure which. I wish I could remember more of that electronics class I took (years ago) in high school.)

Either way, you'd end up with some non-functioning inputs. How do you solve this? Use inverters so that the default state is the one that can be driven by others on the bus? Or is there a simpler way?

And now for my other question. I added a simple write protection jumper for the FRAM. All it does is tie /W to Vcc or /RW, depending on if you want write protection or not. If it's enabled, this means when the CPU tries to write to the FRAM, it ends up doing a read instead. So both the CPU and the RAM will be driving the DATA bus.

Is this safe or could it let the magic smoke out? It's much simpler to just disable the write line than to conditionally disable the select lines, but I don't want to blow anything up in the process.

Finally, one more RAM question. What's the real difference between the E (or CE) and G (or OE) lines? I know what the basic difference is, but I don't understand why they're separate lines. Essentially, I don't see the point of G.

I look forward to any comments, critiques, suggestions, answers, and questions you might have. (And I apologize for being so long winded. Had a lot of ideas today.)

As before, the low 32k is the SRAM. The high 32k is now split into eight banks of 4k each, the seventh and eighth of which are occupied by the boot FRAM. So it's the same layout as before, but now IO space (or whatever else) has (course grained) address decoding.

Once I got that laid out I started thinking about IO devices. I've got a lot of ideas, but I figured I'd keep the main board pretty bare bones. So I decided to throw a bus on it instead. I've been interested in passive backplanes (like the S100) ever since I first heard of them. However, rather than the traditional edge connectors and separate backplane, I borrowed an idea from the Arduino and sketched out a plan for stackable mezzanine boards.

The bus is pretty dumb, it's mostly just the native interface of the 65C02. After drawing up various concepts and looking at available connectors, I decided to go with two rows of 24 pin sockets. I plan to place the sockets at opposite ends of the board and organized their pinouts accordingly.

The first connector (which I've dubbed the X bus) consists of everything needed for address decoding. Namely, the address bus, write enable, and the clock. Additionally, it has the six available decode lines from the '138, which select 4k banks in the open space between the SRAM and FRAM.

The other connector (the Y bus) has everything else. Which means, the data bus, power rails (+5 and +12), and most of the CPU pins (missing are PHI1O, PHI2O, and /SO). With two grounds (one next to each power rail), this leaves four reserved pins. (Or five if I give up one ground. However, this may not be enough as I've already got extra ideas brewing.)

Originally, I only planned on using twelve bit addressing on the bus (the higher bits are all decoded by the mainboard already), which would've saved a few pins, but then I had a eureka moment that made me change my mind. I realized that, if the bus supported it, I could use the programmer I've been designing in circuit! (I just realized that it could also be used to drive IO boards directly from the PC).

Once I made that change, other good reasons for having the full address bus came to mind, like DMA, and remote debugging. Some of these ideas require additions to the bus that haven't been fully developed. In circuit programming wants to run the clock on it's own terms, so it'd need some method of disabling the mainboard's clock. One of my more sophisticated debugging ideas requires the PC emulating potentially any address, which would require some way of avoiding the onboard address decoding. Simple DMA ought to work with what I've already got defined though.

Another idea contending for the few remaining pins is some sort of reset line. The /RES line is exposed on the bus, so any device that wanted to could conceivably pull it high if it wanted, but that seems like a dirty hack. Furthermore, if that device has a reset connected to /RES, it may not even work at all.

Since it's the device pulling /RES high, it'll reset itself and then it's anybody's guess what state the /RES line'll be in. The reset period may not be long enough for other devices on the bus to properly reset, or, worse, the /RES line may be pulled up indefinitely. Having any output lines connected to /RES is probably a bad idea, as I'm sure the state of said line during a reset is undefined for a great many devices, which could reek all kinds of havoc.

What's needed is a dedicated reset output (from the daughter board's POV) the instructs the mainboard's reset circuitry to cleanly reset the machine. So there goes another pin.

One more thing that could be really nice to have once I start developing IO devices would be a programmable interrupt controller. That would require adding additional IRQ lines, so It's likely the bus is going to get larger before I actually implement this.

Anyway, you can check out the latest version of the schematic here. It's still got no clock and reset sub-circuits. That's my next mission (thanks again for the tips), but before then, I've got a few questions.

First up is another question about unused inputs. For completely unused inputs, things are pretty simple, just tie them to the proper logic level. However, what's I'm wondering about is how to handle inputs that aren't used on the mainboard, but might be used by a mezzanine. Then again, they might not...

For instance, the mainboard doesn't do anything involving interrupts, so it wants /IRQ tied to ground. If the mainboard ties it to ground, what happens when some device tries to bring it high? And if it doesn't work, how do you do it correctly?

It's a similar situation with RDY and BE. However, in this case, for normal operation, the mainboard wants them tied high. So, can they be driven low by something else? It seems to me that one way (tied low or tied high) ought to work and the other one won't. (Unfortunately I don't know enough to be sure which. I wish I could remember more of that electronics class I took (years ago) in high school.)

Either way, you'd end up with some non-functioning inputs. How do you solve this? Use inverters so that the default state is the one that can be driven by others on the bus? Or is there a simpler way?

And now for my other question. I added a simple write protection jumper for the FRAM. All it does is tie /W to Vcc or /RW, depending on if you want write protection or not. If it's enabled, this means when the CPU tries to write to the FRAM, it ends up doing a read instead. So both the CPU and the RAM will be driving the DATA bus.

Is this safe or could it let the magic smoke out? It's much simpler to just disable the write line than to conditionally disable the select lines, but I don't want to blow anything up in the process.

Finally, one more RAM question. What's the real difference between the E (or CE) and G (or OE) lines? I know what the basic difference is, but I don't understand why they're separate lines. Essentially, I don't see the point of G.

I look forward to any comments, critiques, suggestions, answers, and questions you might have. (And I apologize for being so long winded. Had a lot of ideas today.)

@loop: lda (src),y — sta (dst),y — iny — bne @loop — inc src+1 — inc dst+1 — dex — bne @loop

-

Karatorian

- Posts: 17

- Joined: 13 Mar 2011

- Location: Rindge NH USA

- Contact:

Bus Design

I think I've figured (at least part of) my question about (potentially) unused inputs on my bus. Basically, I need pull-up or pull-down resistors to set the default state of these inputs. However, I don't know exactly what size of resistors to use.

I came across an informative article Implications of Slow or Floating CMOS Inputs, from which I learned some useful things. It talks about how floating inputs can lead to unstable results, or even worse, component damage if the floating voltage falls into the critical 0.8 to 2.0 volt range. It also discusses minimum rise times to avoid the same problem.

They give an equation:

V(t) = Vcc - (e ** (-t / (CT * R) * (Vcc - Vi))

Which can be used to calculate the voltage at time t, V(t), given the total bus capacitance, CT, the resistance of the pull-up, R, and the initial voltage Vi. This allows you to figure out the size of pull-up you need to satisfy the rise time requirements of the devices on the bus.

In their example, they give Vi as 0.5 volts, but they don't say where this number comes from. Anyone got any ideas? Wouldn't it be safer to assume zero?

They also give a table of the rise time requirements for various logic families. They vary pretty widely, but all but the fastest devices (some ABT) are satisfied with 10ns/v. This means that I've got 20ns to get the line to a safe level of two volts. (Maybe less if I want to leave some headroom. Their example uses 15ns for 10ns/v parts.)

So I started looking at the datasheets I had handy to see what sort of input capacitances I could expect. With what's already on my bus, I have the CPU at 5pF, the SRAM at 7pF, and the FRAM at 6pF (inputs) and 8pF (IOs). So that gives a total of about 20pF. That's not including various bits an pieces in the address decoding, but that's the easy part. (I can go dig up the datasheets.)

The hard part is estimating the capacitance of the bus itself. I'm planning on using printed PCBs for the cards themselves, and wirewrap headers for the bus connectors. I don't know how to estimate the capacitance of the traces. The capacitance of the headers isn't in the datasheet, but I've read elsewhere on the forum that it's kinda high.

So I was wondering if someone could point me towards a good reference for these sorts of things. Or some formulas to figure them out.

Of course, just the bus capacitance of the mainboard isn't much help, but it should allow me to estimate an average per card. By punching numbers into the above equation, I've determined that I can select a specific "max permitted bus" capacitance and then derive the size of my pull-up resistors from there.

Basically, as the capacitance goes up, the max value of the resistors goes down. However, there's got to be some sort of drawback to that, because most of the designs I've looked at (in the hardware projects section) use large values, like 4.7k and 3.3k, whereas the numbers I'm coming up with are much lower. For instance, 375 ohms for a 100pF (kinda' random value), and under 100 ohms for 400pF (the specified limit for I2C). So what's the downside?

Finally, I figure that pull-down resistors can be figured in a similar manner. However, I'm sure there's some difference that must be figured into the formula. Anyone got any hints for figuring that?

I came across an informative article Implications of Slow or Floating CMOS Inputs, from which I learned some useful things. It talks about how floating inputs can lead to unstable results, or even worse, component damage if the floating voltage falls into the critical 0.8 to 2.0 volt range. It also discusses minimum rise times to avoid the same problem.

They give an equation:

V(t) = Vcc - (e ** (-t / (CT * R) * (Vcc - Vi))

Which can be used to calculate the voltage at time t, V(t), given the total bus capacitance, CT, the resistance of the pull-up, R, and the initial voltage Vi. This allows you to figure out the size of pull-up you need to satisfy the rise time requirements of the devices on the bus.

In their example, they give Vi as 0.5 volts, but they don't say where this number comes from. Anyone got any ideas? Wouldn't it be safer to assume zero?

They also give a table of the rise time requirements for various logic families. They vary pretty widely, but all but the fastest devices (some ABT) are satisfied with 10ns/v. This means that I've got 20ns to get the line to a safe level of two volts. (Maybe less if I want to leave some headroom. Their example uses 15ns for 10ns/v parts.)

So I started looking at the datasheets I had handy to see what sort of input capacitances I could expect. With what's already on my bus, I have the CPU at 5pF, the SRAM at 7pF, and the FRAM at 6pF (inputs) and 8pF (IOs). So that gives a total of about 20pF. That's not including various bits an pieces in the address decoding, but that's the easy part. (I can go dig up the datasheets.)

The hard part is estimating the capacitance of the bus itself. I'm planning on using printed PCBs for the cards themselves, and wirewrap headers for the bus connectors. I don't know how to estimate the capacitance of the traces. The capacitance of the headers isn't in the datasheet, but I've read elsewhere on the forum that it's kinda high.

So I was wondering if someone could point me towards a good reference for these sorts of things. Or some formulas to figure them out.

Of course, just the bus capacitance of the mainboard isn't much help, but it should allow me to estimate an average per card. By punching numbers into the above equation, I've determined that I can select a specific "max permitted bus" capacitance and then derive the size of my pull-up resistors from there.

Basically, as the capacitance goes up, the max value of the resistors goes down. However, there's got to be some sort of drawback to that, because most of the designs I've looked at (in the hardware projects section) use large values, like 4.7k and 3.3k, whereas the numbers I'm coming up with are much lower. For instance, 375 ohms for a 100pF (kinda' random value), and under 100 ohms for 400pF (the specified limit for I2C). So what's the downside?

Finally, I figure that pull-down resistors can be figured in a similar manner. However, I'm sure there's some difference that must be figured into the formula. Anyone got any hints for figuring that?

@loop: lda (src),y — sta (dst),y — iny — bne @loop — inc src+1 — inc dst+1 — dex — bne @loop

- GARTHWILSON

- Forum Moderator

- Posts: 8775

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

answering various questions without quoting them:

The downside to the low-value resistors is current consumption and whether you're asking more from the driver than it can supply. WDC CMOS parts have very strong drivers though, able to drive a valid logic state at something like 50mA, symmetrically (in spite of what the data sheet says). Rockwell's 65c22 could pull down to a valid logic 0 with nearly 100mA (although doing it for any length of time would probably damage it) or up with something like 10 or 20mA (I don't remember exactly, but I did test it years ago). NMOS ones are not that strong.

For CMOS inputs that won't get toggled, even hundreds of kilohms is fine to hold them. If you have open-drain IRQ sources though, the resistance needs to be low enough to pull the line back up in time to be at a logic 1 after clearing the interrupt status, before the RTI. I had a problem with that once in something where I used a high resistance to save power. After my RTI, the line had not floated up enough yet to keep the processor from thinking there was already another interrupt that needed service.

Very few lines will have a resistive pull-up though. Most lines will be actively driven up or down by something.

The .5V may have been the assumed upper threshold for a valid logic 0. Usually they want an output to get that down at least to .4V and an input threshold to consider anything below .8V to be a logic 0. The lower threshold for a valid logic 1 is usually assumed to be 2V for input, 2.4V for output.

Due not only to capacitance but also transmission-line effects, I would not recommend having the processor's own buses (data, address, R/W\, Φ2) off the main board unless you plan on staying down at a couple of MHz where you can get away with murder. [Edit: I must clarify that that refers to timings. If you have fast parts, you still have to keep your nose clean regarding build technique, as poor build technique can bite you even at very low clock rates.] If you put 65c22's and possibly other I/O ICs on the main board and then interface other peripherals through those, you'll avoid the pitfalls and the processor will be free to run faster.

RST\, IRQ\, NMI\, RDY, SO\, and BE will normally be high. Things that want to change the normal status will have to yank them down, not up.

Bus contention probably won't "let the smoke out," but it's just bad & pointless design. At a minimum it will increase the power supply current requirement.

On the RAM, CE enables the inside which may take longer to set up the address routing and so on. You might get a head start by enabling the chip before you can afford to enable its output which can be done more quickly. This allows a given speed of RAM to operate at more MHz since you're giving it more time to respond. If you enable the chip based on Φ2 however (instead of enabling during Φ1, before Φ2 rises), then you can just leave the OE true all the time. Outputs won't be enabled if the chip is not enabled.

The downside to the low-value resistors is current consumption and whether you're asking more from the driver than it can supply. WDC CMOS parts have very strong drivers though, able to drive a valid logic state at something like 50mA, symmetrically (in spite of what the data sheet says). Rockwell's 65c22 could pull down to a valid logic 0 with nearly 100mA (although doing it for any length of time would probably damage it) or up with something like 10 or 20mA (I don't remember exactly, but I did test it years ago). NMOS ones are not that strong.

For CMOS inputs that won't get toggled, even hundreds of kilohms is fine to hold them. If you have open-drain IRQ sources though, the resistance needs to be low enough to pull the line back up in time to be at a logic 1 after clearing the interrupt status, before the RTI. I had a problem with that once in something where I used a high resistance to save power. After my RTI, the line had not floated up enough yet to keep the processor from thinking there was already another interrupt that needed service.

Very few lines will have a resistive pull-up though. Most lines will be actively driven up or down by something.

The .5V may have been the assumed upper threshold for a valid logic 0. Usually they want an output to get that down at least to .4V and an input threshold to consider anything below .8V to be a logic 0. The lower threshold for a valid logic 1 is usually assumed to be 2V for input, 2.4V for output.

Due not only to capacitance but also transmission-line effects, I would not recommend having the processor's own buses (data, address, R/W\, Φ2) off the main board unless you plan on staying down at a couple of MHz where you can get away with murder. [Edit: I must clarify that that refers to timings. If you have fast parts, you still have to keep your nose clean regarding build technique, as poor build technique can bite you even at very low clock rates.] If you put 65c22's and possibly other I/O ICs on the main board and then interface other peripherals through those, you'll avoid the pitfalls and the processor will be free to run faster.

RST\, IRQ\, NMI\, RDY, SO\, and BE will normally be high. Things that want to change the normal status will have to yank them down, not up.

Bus contention probably won't "let the smoke out," but it's just bad & pointless design. At a minimum it will increase the power supply current requirement.

On the RAM, CE enables the inside which may take longer to set up the address routing and so on. You might get a head start by enabling the chip before you can afford to enable its output which can be done more quickly. This allows a given speed of RAM to operate at more MHz since you're giving it more time to respond. If you enable the chip based on Φ2 however (instead of enabling during Φ1, before Φ2 rises), then you can just leave the OE true all the time. Outputs won't be enabled if the chip is not enabled.

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

-

Karatorian

- Posts: 17

- Joined: 13 Mar 2011

- Location: Rindge NH USA

- Contact:

I've made some more changes to my design. I added a power connector, some pull-up resistors, clock generation, and a reset controller. I also fixed and improved the address decoding, rearranged the bus headers, and redid the whole layout using bus lines, which makes it a lot less messy.

The power connector is going to be a standard Molex type so I can use the spare PC power supply I currently use as a workbench power supply.

I've got pull-up resistors on all the CPU's input lines that connect to the bus. I've also got pull-ups on two new control lines I added, /REST (reset trigger), and CLKE (clock enable). I haven't worked out the exact values yet. Does anyone know what sort of rise and fall times the W6502S requires? The datasheet gives numbers for the clock pulse (5ns max), but it's unclear whether that's intended for all inputs as well. (Which seems unlikely, at 1ns/v, it'd be the pickiest CMOS around.)

I've got the clock generator setup so it can use full or half size can oscillators. I added a flip-flop to handle any symmetry issues, but I wonder if it's really needed. Since the CPU is fully static, and you can stretch or even stop the clock, does a 40-60% (max) duty cycle really matter? Speaking of stopping the clock, there's now a bus line to do just that. (However, when the clock output is high impedance, the flip-flop's clock input is floating. I'd better fix that.)

Reset control is handled by a simple MAXIM voltage monitor. The one I selected has a minimum of features, but does include a manual reset input (which is now on the bus), with switch debouncing. I also added power and reset LEDs. I'm a little concerned about the reset LED. It's not by any chance going to pull down the reset line, is it?

Address decoding has been much improved. I fixed the FRAM's write protection scheme so that it no longer causes bus contention. I also split it into two banks of 4k, with individual write protection. The idea is to store the critical boot code in the top 4k (normally protected) and use the lower 4k (normally writeable) for general non-volatile storage. However, if I end up wanting to protect all 8k, I have the option.

I also fixed the SRAM so that it won't be subject to spurious writes. Thanks to Garth's explanation of /CE vs /OE, I think I've got chip selection straightened out as well.

Despite Garth's admonition not too, I'm still planning on running the CPU's bus lines off the board and placing the IO on mezzanine cards. Perhaps I'm just naive, but it doesn't seem like the stack will be the speed limit. The bus I'm designing is very similar to the PC/104 bus, and it runs at 6 and 8 MHz (perhaps it can't handle the full 14 plus the CPU can, but I don't really expect to be able to go that fast anyway). I wish I could get better docs on the PC/104 bus. The standard is available, but it mostly just references the ISA standard, which IEEE never finalized and I can't find. Anyone know of a good reference? All the ones I found just covered the basics (little more than the pinout).

I decided to increase the number of bus pins to sixty-four. This gives me a common header size (2x32, of which I found some nice stackable ones), and more room for expansion in the future. With more pins, I rearranged some things. Moving from two single row headers to one double row header also gives me more flexibility with the form-factor, as there's now no need to make expansion boards a specific size.

I think the mainboard design is just about wrapped up, so now I'm gonna start on the PCB layout. (I've experimented a bit with the earlier layouts.) I'm also thinking about a basic IO board and want to get back to working on the in-circuit programmer.

The power connector is going to be a standard Molex type so I can use the spare PC power supply I currently use as a workbench power supply.

I've got pull-up resistors on all the CPU's input lines that connect to the bus. I've also got pull-ups on two new control lines I added, /REST (reset trigger), and CLKE (clock enable). I haven't worked out the exact values yet. Does anyone know what sort of rise and fall times the W6502S requires? The datasheet gives numbers for the clock pulse (5ns max), but it's unclear whether that's intended for all inputs as well. (Which seems unlikely, at 1ns/v, it'd be the pickiest CMOS around.)

I've got the clock generator setup so it can use full or half size can oscillators. I added a flip-flop to handle any symmetry issues, but I wonder if it's really needed. Since the CPU is fully static, and you can stretch or even stop the clock, does a 40-60% (max) duty cycle really matter? Speaking of stopping the clock, there's now a bus line to do just that. (However, when the clock output is high impedance, the flip-flop's clock input is floating. I'd better fix that.)

Reset control is handled by a simple MAXIM voltage monitor. The one I selected has a minimum of features, but does include a manual reset input (which is now on the bus), with switch debouncing. I also added power and reset LEDs. I'm a little concerned about the reset LED. It's not by any chance going to pull down the reset line, is it?

Address decoding has been much improved. I fixed the FRAM's write protection scheme so that it no longer causes bus contention. I also split it into two banks of 4k, with individual write protection. The idea is to store the critical boot code in the top 4k (normally protected) and use the lower 4k (normally writeable) for general non-volatile storage. However, if I end up wanting to protect all 8k, I have the option.

I also fixed the SRAM so that it won't be subject to spurious writes. Thanks to Garth's explanation of /CE vs /OE, I think I've got chip selection straightened out as well.

Despite Garth's admonition not too, I'm still planning on running the CPU's bus lines off the board and placing the IO on mezzanine cards. Perhaps I'm just naive, but it doesn't seem like the stack will be the speed limit. The bus I'm designing is very similar to the PC/104 bus, and it runs at 6 and 8 MHz (perhaps it can't handle the full 14 plus the CPU can, but I don't really expect to be able to go that fast anyway). I wish I could get better docs on the PC/104 bus. The standard is available, but it mostly just references the ISA standard, which IEEE never finalized and I can't find. Anyone know of a good reference? All the ones I found just covered the basics (little more than the pinout).

I decided to increase the number of bus pins to sixty-four. This gives me a common header size (2x32, of which I found some nice stackable ones), and more room for expansion in the future. With more pins, I rearranged some things. Moving from two single row headers to one double row header also gives me more flexibility with the form-factor, as there's now no need to make expansion boards a specific size.

I think the mainboard design is just about wrapped up, so now I'm gonna start on the PCB layout. (I've experimented a bit with the earlier layouts.) I'm also thinking about a basic IO board and want to get back to working on the in-circuit programmer.

@loop: lda (src),y — sta (dst),y — iny — bne @loop — inc src+1 — inc dst+1 — dex — bne @loop

- GARTHWILSON

- Forum Moderator

- Posts: 8775

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

A few things that pop out:

The SRAM's OE\, CS\, and WE\ inputs are just that, meaning active low, not active high. This is pretty normal. A low voltage on OE\ enables the output (if the chip is selected and you're not in write-enable), a low on the CS\ selects the chip (ie, makes it respond), and a low on WE\ enables writing to it (if the chip is selected). You'll need to change some logic.

Although the 65816's Φ2 pin is an input, on the 6502 it's an output. Input must come through Φ0 on the 6502. It looks like you don't have any clock input.

The FRAM's enable circuit has an awful lot of gate delays. See if you can reduce it.

just a note: Some I/O ICs like the 6522 require that the RS and CS lines be valid and stable before Φ2 rises; meaning you can't select them with a circuit that goes through your '138 which is enabled by Φ2.

As to whether the RST\ line will be pulled down by the LED: That depends on the resistor value you choose for it. Even with no resistor at all, the LED will not pull the line down low enough to be a valid 0, but the MAX6804 may hardly be able to pull it up hard enough to get a valid 1 to let the processor run. (I have not looked up the current-- I'll let you do that.)

For low operating speeds, the rise and fall times for most things are not very critical since they are level-sensitive. The Φ0 input is a Schmitt-trigger input, so even an RC between Φ0, Φ1, and Φ2 will work for an oscillator (I did that for hundreds of something we have flying in aircraft cockpits), and by the time the signal gets to the Φ2 output, it will have a good rise and fall time. The '816 OTOH requires a really clean clock input since the same signal feed everything.

Having the oscillator's duty cycle at 50% is not necessary if you're well below the maximum operating speed anyway.

For the connectors to another board, it would be good to have more grounds sprinkled in, or at least move the ground pins you do have to a quarter of the way in from the ends (ie, half way to the middle of the connector) so that the return path for any given signal is not so far from the signal pin.

The SRAM's OE\, CS\, and WE\ inputs are just that, meaning active low, not active high. This is pretty normal. A low voltage on OE\ enables the output (if the chip is selected and you're not in write-enable), a low on the CS\ selects the chip (ie, makes it respond), and a low on WE\ enables writing to it (if the chip is selected). You'll need to change some logic.

Although the 65816's Φ2 pin is an input, on the 6502 it's an output. Input must come through Φ0 on the 6502. It looks like you don't have any clock input.

The FRAM's enable circuit has an awful lot of gate delays. See if you can reduce it.

just a note: Some I/O ICs like the 6522 require that the RS and CS lines be valid and stable before Φ2 rises; meaning you can't select them with a circuit that goes through your '138 which is enabled by Φ2.

As to whether the RST\ line will be pulled down by the LED: That depends on the resistor value you choose for it. Even with no resistor at all, the LED will not pull the line down low enough to be a valid 0, but the MAX6804 may hardly be able to pull it up hard enough to get a valid 1 to let the processor run. (I have not looked up the current-- I'll let you do that.)

For low operating speeds, the rise and fall times for most things are not very critical since they are level-sensitive. The Φ0 input is a Schmitt-trigger input, so even an RC between Φ0, Φ1, and Φ2 will work for an oscillator (I did that for hundreds of something we have flying in aircraft cockpits), and by the time the signal gets to the Φ2 output, it will have a good rise and fall time. The '816 OTOH requires a really clean clock input since the same signal feed everything.

Having the oscillator's duty cycle at 50% is not necessary if you're well below the maximum operating speed anyway.

For the connectors to another board, it would be good to have more grounds sprinkled in, or at least move the ground pins you do have to a quarter of the way in from the ends (ie, half way to the middle of the connector) so that the return path for any given signal is not so far from the signal pin.

- BigDumbDinosaur

- Posts: 9428

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

GARTHWILSON wrote:

The SRAM's OE\, CS\, and WE\ inputs are just that, meaning active low, not active high.

Quote:

The FRAM's enable circuit has an awful lot of gate delays. See if you can reduce it.

Quote:

just a note: Some I/O ICs like the 6522 require that the RS and CS lines be valid and stable before Φ2 rises; meaning you can't select them with a circuit that goes through your '138 which is enabled by Φ2.

On the other hand, R/W should be qualified by Ø2 so a write only occurs while Ø2 is high. Otherwise you run the risk of a wild write hitting the wrong register in a device—or even the wrong device—as the MPU sets up the address lines. Also, in all members of the 65xx family, D0-D7 is invalid during the first half of Ø2 low, which is also why R/W should occur only when Ø2 goes high. The 65C02 timing diagram makes this all pretty clear.

incidentally, the VDA and VPA outputs of the 65C816 make address qualification a bit less onerous than with the 65C02, as the VDA and VPA outputs are asserted only when the address bus is valid.

Quote:

For the connectors to another board, it would be good to have more grounds sprinkled in, or at least move the ground pins you do have to a quarter of the way in from the ends (ie, half way to the middle of the connector) so that the return path for any given signal is not so far from the signal pin.

Lastly, and I'm sure Garth and others will agree with me on this, try not to let too much creeping featurism get into your first effort. Sometimes folks who are venturing forth with their first 65xx-based computer try to do too much and end up with a complicated design that doesn't initially work and is beyond their skill level to debug. You really want to use a minimalist approach for your first design. In other words, it's best to learn how to make a single-engine plane fly before building that four-engine jumbo jet.

x86? We ain't got no x86. We don't NEED no stinking x86!