Getting started with Xilinx CPLD's & FPGA's

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Getting started with Xilinx CPLD's & FPGA's

All info in this thread applies to the first steps needed to interface Xilinx CPLD's and/or FPGA's to an "x86 PC" using the JTAG interface along with the Xilinx ISE software, in an effort to successfully program these CPLD's/FPGA's. Your PC will need 1 port for the JTAG interface, typically either a parallel or USB interface.

Previous knowledge of basic TTL/CMOS logic design is assumed.

If you are ready to get your "feet wet" using programmable logic arrays and are starting a new project, forget ABT, ACT, & F series TTL!

Join this CPLD/FPGA revolution and you will understand why it's becoming more and more difficult to find these older discrete devices.

Your journey will be similar to crossing a river by hopping from stone to stone. Sometimes the jumps are quick. Other times, not so quick and you look around and wonder how you got to where you are after so many, many jumps. And then how to make the next jump! One thing I am realizing is that there is no end to crossing the river, it's all about the journey. And forums are a great way to learn!

I'd like to share the little I've learned, in an attempt to learn more.

At the end of this post, you will be ready to make your 1st jump. Good luck!...

I remember looking at my first CPLD Datasheet. It was a Xilinx XC9572 that Daryl was using for his 65SPI controller. Being a regular reader of TTL datasheets, I remember thinking: "How does one go about wiring all the I/O pins?". When reading the CPLD/FPGA datasheet, these pins are just named I/Oxx.

The simple answer is: The ISE software automatically assigns I/O pins based on your schematic/VHDL/Verilog/netlist source.

So you work with ISE to design FIRST, then observe ISE's pin assignments, and then wire it up! Afterwards, you can lock your pins in ISE, so you won't have to rewire your design.

Realize though, once a design expands to a certain level, you may start to observe errors in ISE. If this happens, unlock all pins and see if your design will re-"fit" with the current IC. If you're still having errors, try fitting for a larger device and/or "Clean UP Project Files" under the Project Menu of ISE...

Back to the basics though!

Let's say you need an address decoding circuit. A Xilinx XC9536 ( http://www.xilinx.com/support/documenta ... /ds064.pdf ) would be an excellent choice as it is the smallest of the Xilinx family. It has 5V I/O, 5ns speed, and comes in a 44-pin PLCC. Easy to find a socket for those. (Although, last time I checked DigiKey, only the 10ns version was available in PLCC. Price ~$4US each). Imagine!, you have 34 I/O pins to assign... No problem using all 16 (or more) address lines from a 6502, for a complete "no waste" memory address decode. And don't worry about delays. I've used up to 3 gates in series and have not observed a "summation" of prop delays associated with each gate like one would expect using TTL. Another beauty? Check out the library of gates you get to choose from!: http://www.xilinx.com/itp/xilinx10/book ... ll_scm.pdf

Now, let's say you have your socket and your CPLD. What next?

You will also need a 6-pin male SIP header. Call it the JTAG header.

Next, you will need a JTAG cable.

You can get one from Digilent for $12US. It uses a PC parallel port and will work with many different voltages (1.8V and up) required by various CPLD's/FPGA's. USB versions are a little more expensive ~$50.

Digilent also sells the JTAG header for $1. On the end of the cable is printed the JTAG pin assignments so there's no confusion. http://www.digilentinc.com/Products/Cat ... ,395&Cat=5

We're almost ready. The final piece of the puzzle is the ISE software, and it's free. It's a large download @4GB+, so start downloading it NOW!

We've spent so far, minus shipping: $4 CPLD, $1 PLCC socket, $1 JTAG header, $12 JTAG cable. $1 bypass cap's. <$20 is not too bad ?

Now, to complete the 1st "JUMP".

Wire up all your power connections to the CPLD according to the datasheet and be sure to include include bypass capacitors.

Wire the JTAG header to the CPLD.

Plug in your JTAG cable to your PC and connect it to your header.

Apply power to the CPLD.

Now run the Xilinx Impact program. Right click in the middle of the screen and choose "initiate chain".

If you've done everything correct, ISE Impact will recognize the XC9536.

You are now ready for your second JUMP. Design using the main ISE program!

Previous knowledge of basic TTL/CMOS logic design is assumed.

If you are ready to get your "feet wet" using programmable logic arrays and are starting a new project, forget ABT, ACT, & F series TTL!

Join this CPLD/FPGA revolution and you will understand why it's becoming more and more difficult to find these older discrete devices.

Your journey will be similar to crossing a river by hopping from stone to stone. Sometimes the jumps are quick. Other times, not so quick and you look around and wonder how you got to where you are after so many, many jumps. And then how to make the next jump! One thing I am realizing is that there is no end to crossing the river, it's all about the journey. And forums are a great way to learn!

I'd like to share the little I've learned, in an attempt to learn more.

At the end of this post, you will be ready to make your 1st jump. Good luck!...

I remember looking at my first CPLD Datasheet. It was a Xilinx XC9572 that Daryl was using for his 65SPI controller. Being a regular reader of TTL datasheets, I remember thinking: "How does one go about wiring all the I/O pins?". When reading the CPLD/FPGA datasheet, these pins are just named I/Oxx.

The simple answer is: The ISE software automatically assigns I/O pins based on your schematic/VHDL/Verilog/netlist source.

So you work with ISE to design FIRST, then observe ISE's pin assignments, and then wire it up! Afterwards, you can lock your pins in ISE, so you won't have to rewire your design.

Realize though, once a design expands to a certain level, you may start to observe errors in ISE. If this happens, unlock all pins and see if your design will re-"fit" with the current IC. If you're still having errors, try fitting for a larger device and/or "Clean UP Project Files" under the Project Menu of ISE...

Back to the basics though!

Let's say you need an address decoding circuit. A Xilinx XC9536 ( http://www.xilinx.com/support/documenta ... /ds064.pdf ) would be an excellent choice as it is the smallest of the Xilinx family. It has 5V I/O, 5ns speed, and comes in a 44-pin PLCC. Easy to find a socket for those. (Although, last time I checked DigiKey, only the 10ns version was available in PLCC. Price ~$4US each). Imagine!, you have 34 I/O pins to assign... No problem using all 16 (or more) address lines from a 6502, for a complete "no waste" memory address decode. And don't worry about delays. I've used up to 3 gates in series and have not observed a "summation" of prop delays associated with each gate like one would expect using TTL. Another beauty? Check out the library of gates you get to choose from!: http://www.xilinx.com/itp/xilinx10/book ... ll_scm.pdf

Now, let's say you have your socket and your CPLD. What next?

You will also need a 6-pin male SIP header. Call it the JTAG header.

Next, you will need a JTAG cable.

You can get one from Digilent for $12US. It uses a PC parallel port and will work with many different voltages (1.8V and up) required by various CPLD's/FPGA's. USB versions are a little more expensive ~$50.

Digilent also sells the JTAG header for $1. On the end of the cable is printed the JTAG pin assignments so there's no confusion. http://www.digilentinc.com/Products/Cat ... ,395&Cat=5

We're almost ready. The final piece of the puzzle is the ISE software, and it's free. It's a large download @4GB+, so start downloading it NOW!

We've spent so far, minus shipping: $4 CPLD, $1 PLCC socket, $1 JTAG header, $12 JTAG cable. $1 bypass cap's. <$20 is not too bad ?

Now, to complete the 1st "JUMP".

Wire up all your power connections to the CPLD according to the datasheet and be sure to include include bypass capacitors.

Wire the JTAG header to the CPLD.

Plug in your JTAG cable to your PC and connect it to your header.

Apply power to the CPLD.

Now run the Xilinx Impact program. Right click in the middle of the screen and choose "initiate chain".

If you've done everything correct, ISE Impact will recognize the XC9536.

You are now ready for your second JUMP. Design using the main ISE program!

Last edited by ElEctric_EyE on Mon Dec 06, 2010 1:31 am, edited 15 times in total.

I am also working with the Xilinx CPLDs. I've written up my experience here: http://www.6502.org/users/andre/icaphw/xilinx.html

What I find very helpful is that you can simulate VHDL with the free ghdl (VHDL compiler based on GCC) compiler. This makes turnaround times really quick

André

What I find very helpful is that you can simulate VHDL with the free ghdl (VHDL compiler based on GCC) compiler. This makes turnaround times really quick

André

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Andre, I checked out your link. You appear to be having a similar problem that I am currently having: implementing bidirectional data buses internally. Except you are using a CPLD. I'm thinking I have unwisely switched to FPGA, albeit for previously good reasons.

I'm starting to realize that my need to have multiple internal I/O ports (in my PWA project here: viewtopic.php?t=1370&start=291 ) is not going to work inside an FPGA. More likely it will work in a CPLD. I did some testing today...

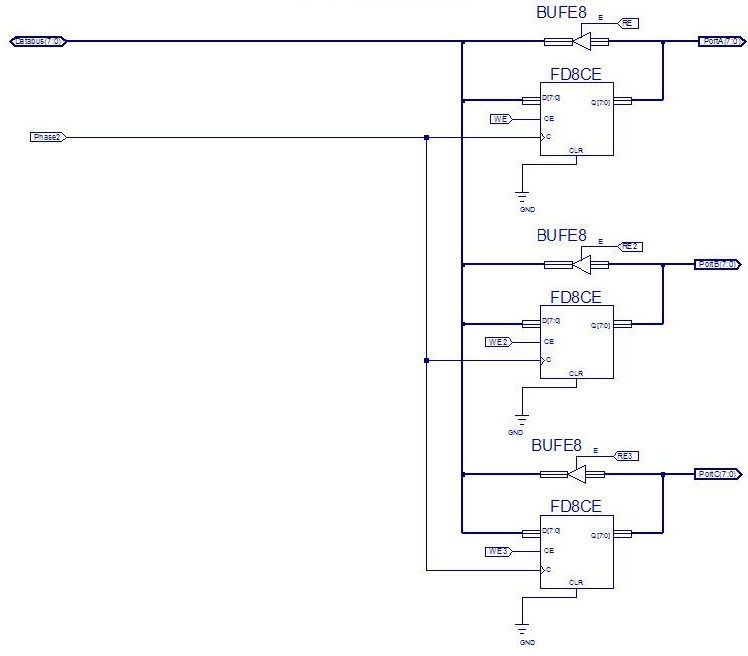

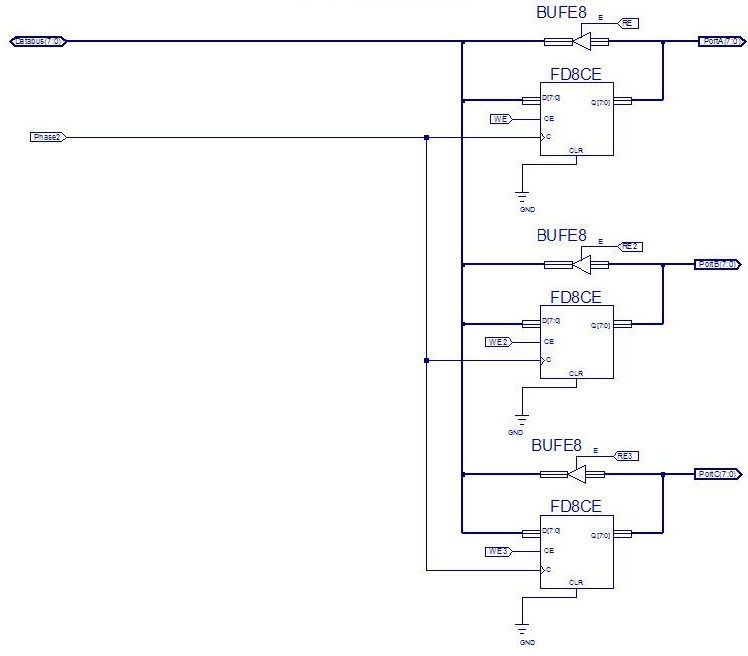

A simple, proven design that worked previously on the CPLD for me. But it gives me errors on the FPGA.

http://i207.photobucket.com/albums/bb73 ... error1.jpg

Then I tried the following, which worked on the FPGA.

http://i207.photobucket.com/albums/bb73 ... /pass1.jpg

But, I needed more I/O ports. These didn't work in the FPGA. Tried a couple different ways. No pass.

http://i207.photobucket.com/albums/bb73 ... error2.jpg

http://i207.photobucket.com/albums/bb73 ... error3.jpg

The following however, does seem to work using a CPLD. It passes with warnings, as did the first design above.

http://i207.photobucket.com/albums/bb73 ... /pass4.jpg

Note: The previous pics are representative of a project assembled only for testing ISE, as you see here. The ports are intended to control internal registers that will be compatible with RMW commands like INC/DEC $xxxx. The ports were not intended to have outputs as you see here.

I'm starting to realize that my need to have multiple internal I/O ports (in my PWA project here: viewtopic.php?t=1370&start=291 ) is not going to work inside an FPGA. More likely it will work in a CPLD. I did some testing today...

A simple, proven design that worked previously on the CPLD for me. But it gives me errors on the FPGA.

http://i207.photobucket.com/albums/bb73 ... error1.jpg

Then I tried the following, which worked on the FPGA.

http://i207.photobucket.com/albums/bb73 ... /pass1.jpg

But, I needed more I/O ports. These didn't work in the FPGA. Tried a couple different ways. No pass.

http://i207.photobucket.com/albums/bb73 ... error2.jpg

http://i207.photobucket.com/albums/bb73 ... error3.jpg

The following however, does seem to work using a CPLD. It passes with warnings, as did the first design above.

http://i207.photobucket.com/albums/bb73 ... /pass4.jpg

Note: The previous pics are representative of a project assembled only for testing ISE, as you see here. The ports are intended to control internal registers that will be compatible with RMW commands like INC/DEC $xxxx. The ports were not intended to have outputs as you see here.

Completley forget about doing any internal logic with signals with multiple drivers.

FPGAs do not work like that. In fact, modern CMOS does not work like that. If you ask for a multi-driver bus, then the software will synthesize it poorly by building a big multiplexer somewhere for all your outputs, then feeding all the inputs off the output of the mux.

The bus that connects to the outside world can go as input to all your components; thats fine. Now, build a mux, and feed it the outputs of all your devices. However you want the mux to work is up to you; it can either be just an OR of them all (and they each have their own shutoffs), or it can be an actual selector fed with the address decode logic. The output drivers of this mux should be controlled by the read/write signal.

Because you're now designing to the hardware, you'll find things work better. They will also be smaller.

(This is one of the reasons I recommend anyone planning on doing FPGA/CPLD work learn Verilog or VHDL. They make you think much more closely about how the hardware actually works. In the long run, you will also find it much faster to work in.)

FPGAs do not work like that. In fact, modern CMOS does not work like that. If you ask for a multi-driver bus, then the software will synthesize it poorly by building a big multiplexer somewhere for all your outputs, then feeding all the inputs off the output of the mux.

The bus that connects to the outside world can go as input to all your components; thats fine. Now, build a mux, and feed it the outputs of all your devices. However you want the mux to work is up to you; it can either be just an OR of them all (and they each have their own shutoffs), or it can be an actual selector fed with the address decode logic. The output drivers of this mux should be controlled by the read/write signal.

Because you're now designing to the hardware, you'll find things work better. They will also be smaller.

(This is one of the reasons I recommend anyone planning on doing FPGA/CPLD work learn Verilog or VHDL. They make you think much more closely about how the hardware actually works. In the long run, you will also find it much faster to work in.)

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

@OwenS,

It is nice to finally be able to post here in the 6502 forums as a beginner to CPLD/FPGA design and have someone familiar, with more knowledge offer a more expert advice! I post in the Xilinx forums rarely because I am a proponent of schematic design... I seem to be the only one!

A multiple driver design 'error' implies a design with feedback, thus inputs and outputs are in conflict. Xilinx CPLD's seem to give you more room in this regard. More room than their FPGA's.

How would a FPGA design correctly implement multiple internal I/O ports through a single external bus?

It is nice to finally be able to post here in the 6502 forums as a beginner to CPLD/FPGA design and have someone familiar, with more knowledge offer a more expert advice! I post in the Xilinx forums rarely because I am a proponent of schematic design... I seem to be the only one!

A multiple driver design 'error' implies a design with feedback, thus inputs and outputs are in conflict. Xilinx CPLD's seem to give you more room in this regard. More room than their FPGA's.

How would a FPGA design correctly implement multiple internal I/O ports through a single external bus?

ElEctric_EyE wrote:

How would a FPGA design correctly implement multiple internal I/O ports through a single external bus?

Defenition of the data bus and the use of it:

Code: Select all

entity RB65 is

Port (

......

D : inout std_logic_vector(7 downto 0);

......

);

end RB65;

architecture AR_RB65 of RB65 is

D <= std_logic_vector(D_out) when ((PHI_i = '1') and (RW_i = '0'))

else "ZZZZZZZZ";

IntData <= unsigned(D) when (PHI0 = '1'); -- read data

Opcode <= unsigned(D) when ((PHI0 = '1') and (OpcC_Reset = '1'));

SYNC <= '1' when ((PHI_0 = '1') and (OpcC_Reset = '1')) else '0';

end AR_RB65;

IntData holds the data read at every clock, Opcode speaks for itself IMHO.

Have fun!

Last edited by Ruud on Fri Oct 22, 2010 6:21 am, edited 1 time in total.

Code: Select all

___

/ __|__

/ / |_/ Groetjes, Ruud

\ \__|_\

\___| URL: www.baltissen.org

- BigDumbDinosaur

- Posts: 9426

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

Code: Select all

entity RB65 is

Port (

......

D : inout std_logic_vector(7 downto 0);

......

);

end RB65;

architecture AR_RB65 of RB65 is

D <= std_logic_vector(D_out) when ((PHI_i = '1') and (RW_i = '0'))

else "ZZZZZZZZ";

IntData <= unsigned(D) when (PHI0 = '1'); -- read data

Opcode <= unsigned(D) when ((PHI0 = '1') and (OpcC_Reset = '1'));

SYNC <= '1' when ((PHI_0 = '1') and (OpcC_Reset = '1')) else '0';

end AR_RB65; x86? We ain't got no x86. We don't NEED no stinking x86!

BigDumbDinosaur wrote:

A more readable version of his VHDL.

Code: Select all

___

/ __|__

/ / |_/ Groetjes, Ruud

\ \__|_\

\___| URL: www.baltissen.org

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

ElEctric_EyE wrote:

...How would a FPGA design correctly implement multiple internal I/O ports through a single external bus?

I post for us beginners.

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

BigDumbDinosaur wrote:

Code: Select all

entity RB65 is

Port (

......

D : inout std_logic_vector(7 downto 0);

......

);

end RB65;

architecture AR_RB65 of RB65 is

D <= std_logic_vector(D_out) when ((PHI_i = '1') and (RW_i = '0'))

else "ZZZZZZZZ";

IntData <= unsigned(D) when (PHI0 = '1'); -- read data

Opcode <= unsigned(D) when ((PHI0 = '1') and (OpcC_Reset = '1'));

SYNC <= '1' when ((PHI_0 = '1') and (OpcC_Reset = '1')) else '0';

end AR_RB65; Might have been an error in my code though.

Is there a specific difference between CPLDs and FPGAs in that respect?

Thanks

André

Hallo André,

I had the same problem with Altera CPLDs. That doesn't mean that all CPLDs will behave like this but unfortunately just the ones we picked.

Gideon stated that he is quite sure that future FPGA's won't be bi-directional anymore. I know nowadays FPGAs have a lot of pins. But with a 64-bit processor you'll need at least 192 pins for the address and data bus only!.

fachat wrote:

.... and make that port write-only.

Gideon stated that he is quite sure that future FPGA's won't be bi-directional anymore. I know nowadays FPGAs have a lot of pins. But with a 64-bit processor you'll need at least 192 pins for the address and data bus only!.

Code: Select all

___

/ __|__

/ / |_/ Groetjes, Ruud

\ \__|_\

\___| URL: www.baltissen.org

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Andre,

I can only speak from my use ot FPGA's and CPLD's using schematic entry as I have not crossed the bridge to HDL yet, but I can say this: That link I had posted has given me insight to problems I've been having.

This what I have learned about implementing bidirectional buses inside CPLD's & FPGA's:

When working with CPLD's, you can have a bidirectional bus that goes to each of your internal ports.

RE, WE are Read Enable & Write Enable signals decoded with Address and R/W.

When working with FPGA's however, you can have only 1 point within the entire IC that is bidirectional (i.e. high impedance "Z" state). So, in that link to the Xilinx forums I mentioned earlier, Gabor stated "... it is best to have this bidirectional entry point at the highest level in your design...".

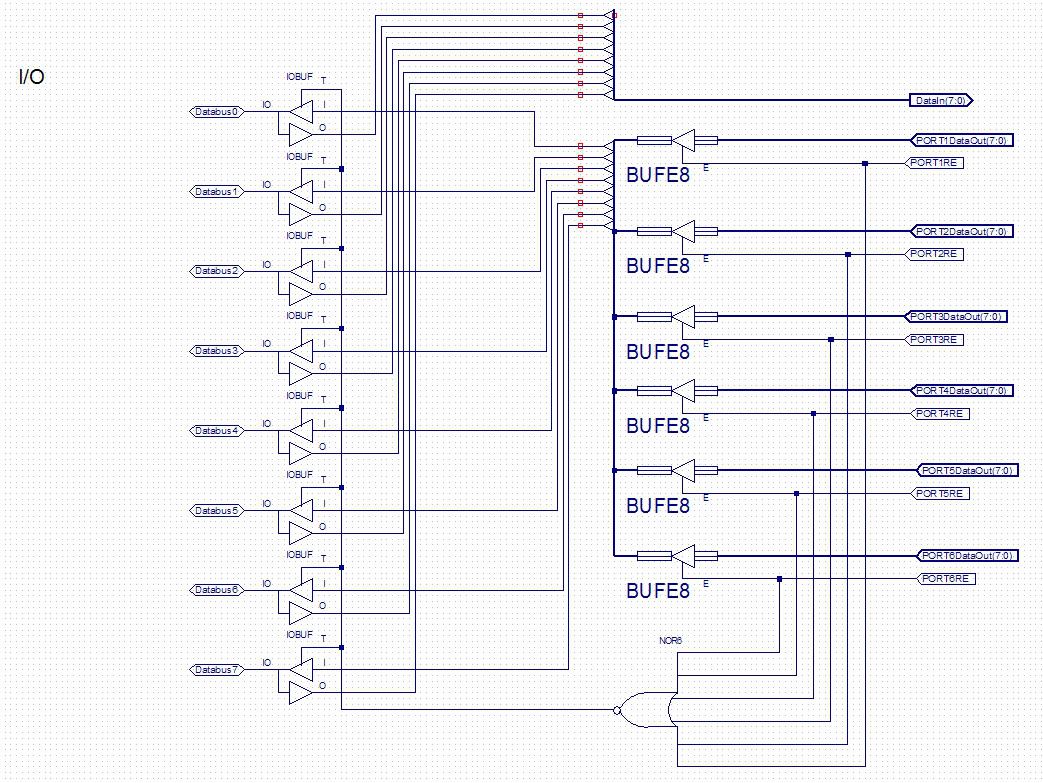

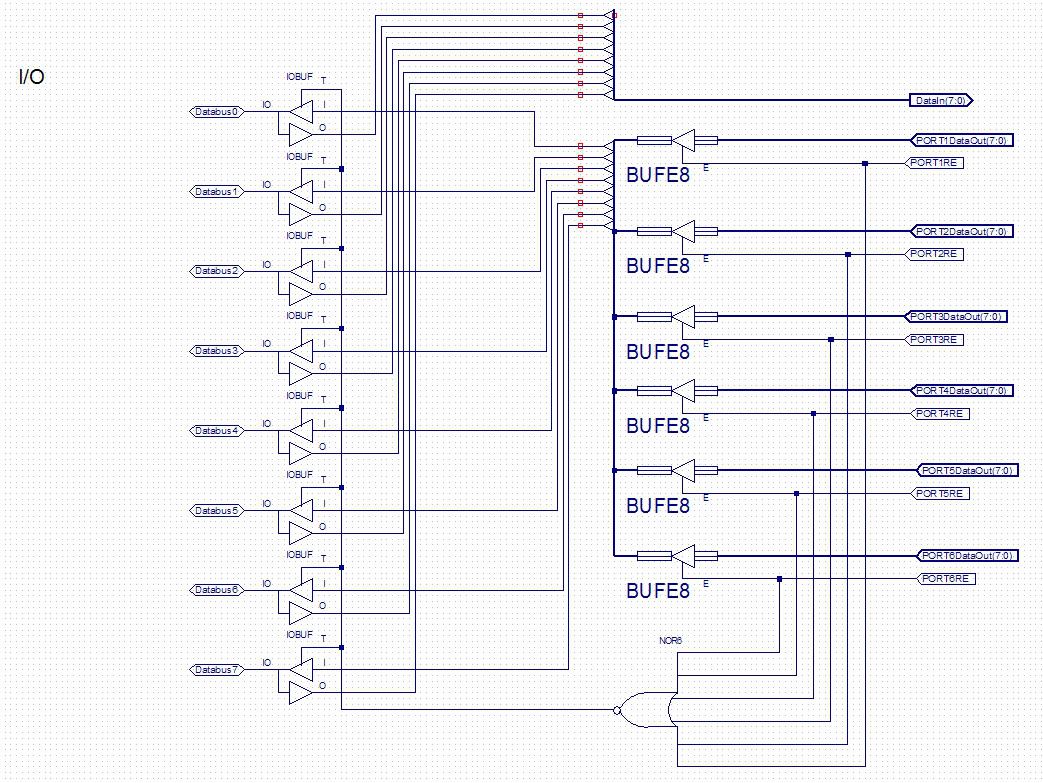

Below is a module similar to one I'm currently using successfully to interface the 6502 databus to multiple, readable output ports inside the FPGA. The only difference is, I've renamed some assignments and added more ports to express the idea more fully.

Databus(7:0) on the left, is assigned to pins on the FPGA. They connect directly to the 6502.

DataIn(7:0) on the top right is common to all the inputs of all the 8-bit PORTs, present inside other modules.

The PORTxRE (read enable) signals from each PORT are NOR'd, to put the data from the corresponding PORT onto the Databus.

I can only speak from my use ot FPGA's and CPLD's using schematic entry as I have not crossed the bridge to HDL yet, but I can say this: That link I had posted has given me insight to problems I've been having.

This what I have learned about implementing bidirectional buses inside CPLD's & FPGA's:

When working with CPLD's, you can have a bidirectional bus that goes to each of your internal ports.

RE, WE are Read Enable & Write Enable signals decoded with Address and R/W.

When working with FPGA's however, you can have only 1 point within the entire IC that is bidirectional (i.e. high impedance "Z" state). So, in that link to the Xilinx forums I mentioned earlier, Gabor stated "... it is best to have this bidirectional entry point at the highest level in your design...".

Below is a module similar to one I'm currently using successfully to interface the 6502 databus to multiple, readable output ports inside the FPGA. The only difference is, I've renamed some assignments and added more ports to express the idea more fully.

Databus(7:0) on the left, is assigned to pins on the FPGA. They connect directly to the 6502.

DataIn(7:0) on the top right is common to all the inputs of all the 8-bit PORTs, present inside other modules.

The PORTxRE (read enable) signals from each PORT are NOR'd, to put the data from the corresponding PORT onto the Databus.

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

So now I have a 7-bit (A14-A20) RAMBANK PORT and a 5-bit (A14-A18) ROMBANK PORT that I can perform INC/DEC on. At least I have proven it on the RAMBANK.

The past few days I've been trying to figure out how to INIT an FD8CE for the ROMBANK as it needs to start out with upper bank selected. I need to INIT the 8-bit port for $FF on powerup.

Sounds easy, but I've been having no luck.

Everything else is working.

I know this because when I disconnect the ROMBANK pins (A14-A18 going to the 512Kx8 EEPROM), inside the FPGA, from the PORT and connect each of these pins individually to VCC, the system works.

Can anyone help with Flip Flop INIT values?

The past few days I've been trying to figure out how to INIT an FD8CE for the ROMBANK as it needs to start out with upper bank selected. I need to INIT the 8-bit port for $FF on powerup.

Sounds easy, but I've been having no luck.

Everything else is working.

I know this because when I disconnect the ROMBANK pins (A14-A18 going to the 512Kx8 EEPROM), inside the FPGA, from the PORT and connect each of these pins individually to VCC, the system works.

Can anyone help with Flip Flop INIT values?

ElEctric_EyE wrote:

The past few days I've been trying to figure out how to INIT an FD8CE for the ROMBANK as it needs to start out with upper bank selected. I need to INIT the 8-bit port for $FF on powerup.

Sounds easy, but I've been having no luck.

Sounds easy, but I've been having no luck.

If you don't want to place a ton of FDCPs, there's a simple workaround: place an INV8 directly before and after the FD8CP. The register will then store inverted data, and the powerup value will be $FF instead of $00.

so long,

Hias