We (myself and richarde) have a couple of FPGA modules from OHO. The 24-pin module is more capable (has on-board RAM) but the 40-pin is a good device for testing designs.

I loaded the T65 free 6502 design and got some 6502-like activity on the pins, but it didn't boot in the Beeb and I haven't investigated yet. It could easily be timing problems because I wasn't at all careful with timing constraints.

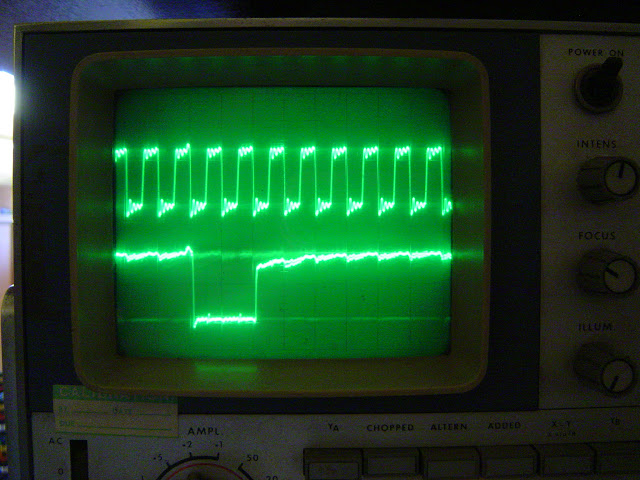

RichardE did much better: he's written a TUBE in verilog, and after a few iterations it came to life. We've only tried it in a single board: the internal second processor board of his BBC Master. There are pictures in our gallery:

]

We need to try some file i/o, which means finding and hooking up a disk drive: Elite would be a good test! We know the performance will be a few percent off because it's a minimal design with less buffering than the original.

Also, somehow, we'd like to see how this design works in other second-processor hardware. Perhaps we can borrow something.

(Other people have done this before, and there are one or two products which include TUBE implementations, but we don't think anyone has released sources.)