First of all, great work!

I stumbled upon a few things while recreating the schematic in KiCad/eeschema which I thought would be nice to share.

First, I noticed that the output databus is latched at the end of phase 1. That's apparently how Logisim RAM works. This is not the same as real hardware where the transaction takes place during phase 2 and ends when R/W goes high again.

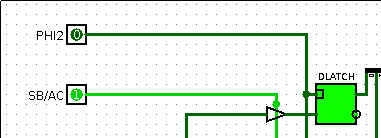

Secondly, I noticed that the transfer of SB to AC on PHI2 only seems to work because of a hazard that occurs in Logisim. SB/AC and PHI2 are not supposed to ever be high at the same time, but there is a small window when PHI2 goes high before SB/AC goes low again.

Attachment:

ALU_AC_latch.png [ 6.9 KiB | Viewed 1007 times ]

ALU_AC_latch.png [ 6.9 KiB | Viewed 1007 times ]

This is a side effect of Logisim's simulation. Other simulations I ran (LCC, another ED simulation, and Verilator) failed to latch SB into AC. I fixed this by latching on SB/AC directly.

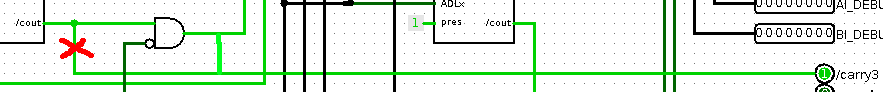

Thirdly, the BCD correction does not work. I traced it back to the following wrong connection:

Attachment:

bcd-fix.png [ 2.76 KiB | Viewed 1007 times ]

bcd-fix.png [ 2.76 KiB | Viewed 1007 times ]

/carry3 connects after the AND port. After that, the full 6502 Dormann test passes!